# UNIVERSITY OF THESSALY

**DOCTORAL THESIS**

# Design space exploration in near-data co-processors for general-purpose acceleration, in high-performance and low-power processing environments

Author: Athanasios TZIOUVARAS Supervisors: Prof. George STAMOULIS Prof. Nestor EVMORFOPOULOS Prof. Athanasios LOUKOPOULOS

A thesis submitted in fulfillment of the requirements for the degree of Doctor of Philosophy

in the

Electronics Lab Department of Electrical and Computer Engineering May 10, 2021

# **Declaration of Authorship**

I, Athanasios TZIOUVARAS, declare that this thesis titled, "Design space exploration in neardata co-processors for general-purpose acceleration, in high-performance and low-power processing environments" and the work presented in it are my own. I confirm that:

- This work was done wholly or mainly while in candidature for a research degree at this University.

- Where any part of this thesis has previously been submitted for a degree or any other qualification at this University or any other institution, this has been clearly stated.

- Where I have consulted the published work of others, this is always clearly attributed.

- Where I have quoted from the work of others, the source is always given. With the exception of such quotations, this thesis is entirely my own work.

- I have acknowledged all main sources of help.

- Where the thesis is based on work done by myself jointly with others, I have made clear exactly what was done by others and what I have contributed myself.

| Signed: |  |  |  |

|---------|--|--|--|

| _       |  |  |  |

Date:

"Fooling around with alternating current (AC) is just a waste of time. Nobody will use it, ever."

Thomas Edison

## UNIVERSITY OF THESSALY

# Abstract

## Department of Electrical and Computer Engineering

## Doctor of Philosophy

## Design space exploration in near-data co-processors for general-purpose acceleration, in high-performance and low-power processing environments

by Athanasios TZIOUVARAS

Modern computer architectures face a performance scaling wall as the throughput and power consumption bottleneck has shifted from the core pipeline towards the DRAM latency and data transfer operations. This phenomenon can be partially attributed to the stop of Dennard's scaling and to the continuous shrinking size of transistors. As a result, the power density of the integrated circuits has increased to a point where most of the cores in a multi-core architecture are forced to operate in near-threshold voltage levels. In order to address such an issue, researchers tend to deviate from the standard Von Neuman architectures towards new computing models. In the last decade there is a resurgence of the NDP paradigm, under which the instructions are executed on the DRAM die instead of the core pipeline. Therefore, the amount of CPU-DRAM transactions is significantly decreased and thus, it positively affects the power dissipation and the achievable throughput of the system. Under this premise, in this dissertation we explore the NDP paradigm for high performance and for low-power computing. Regarding the high performance computing, we propose a novel approach that considers general purpose loop execution. Our design employs an instruction scheduling methodology which issues each individual instruction on a custom integrated circuit acting as loop accelerator that is located on the logic layer of an HMC DRAM. There, instructions are iteratively executed in parallel in a software pipelining fashion, while intermediate results are forwarded through an on-chip interconnection network. Regarding the low-power computing, we develop a novel timing analysis methodology that is based on the premises of STA, specifically for low-power, low-end pipelines. The proposed timing methodology considers the excitation of the timing paths for each instruction supported by the ISA, and calculates the worst-case slack for each individual instruction. As a result, we obtain timing information on an instruction level and we proceed in exploiting such knowledge to adaptively scale the clock frequency according to instruction types that execute in the pipeline at any given time. In the sequel, we employ the aforementioned BTWC methodology to co-design a pipeline from the ground up to support a clock scaling mechanism with cycle-to-cycle granularity. We focus on the general purpose code execution and we implement our design on the logic layer of an HMC DRAM in order to enable near-data execution. We opt to evaluate both the high performance and the low power architectures on post-layout simulations in order to strengthen the validity of our designs. Results indicate a significant performance increase in terms of throughput over the baseline processors while the power consumption levels are critically reduced.

# **Greek Abstract**

Εξερεύνηση σχεδιαστικού χώρου των συν-επεξεργαστών κοντά στην κύρια μνήμη για επιτάχυνση κώδικα γενικού σκοπού, σε περιβάλλοντα υψηλών επιδόσεων και χαμηλής κατανάλωσης ισχύος

Οι σύγχρονες αρχιτεκτονικές υπολογιστών είναι αντιμέτωπες με ένα σοβαρό πρόβλημα που αφορά την κλιμάκωση της απόδοσης τους, καθώς η συμφόρηση της πληροφορίας έχει μετατοπιστεί από τον πυρήνα του επεξεργαστή στην μονάδα της κύριας μνήμης και στις λειτουργίες μεταφοράς δεδομένων. Το φαινόμενο αυτό μπορεί μεριχώς να αποδοθεί στο τέλος της ισχύος του νόμου του Dennard και στην διαρκή μείωση του μεγέθους των τρανσίστορς. Ως αποτέλεσμα, η πυχνότητα ισχύος των ολοχληρωμένων χυχλωμάτων έχει αυξηθεί τόσο, ώστε η λειτουργία των πολύ-πυρηνικών επεξεργαστών να επιτελείται σε τάσεις που βρίσκονται κοντά στην τάση κατωφλίου. Για να ξεπεράσουν το πρόβλημα αυτό, οι ερευνητές τείνουν να αποκλίνουν από τις κλασικές αρχιτεκτονικές προσεγγίσεις τύπου Von Neuman και να στρέφουν την προσοχή τους σε νέα μοντέλα επεξεργασίας. Την τελευταία δεχαετία έχει παρατηρηθεί μία αναζωπύρωση του ενδιαφέροντος για το παράδειγμα εκτέλεσης εντολών κοντά στην κύρια μνήμη (NDP), κατά το οποίο οι εντολές εκτελούνται στο κύκλωμα της κύριας μνήμης αντί του κεντρικού επεξεργαστή. Έτσι, ο αριθμός των λειτουργιών της μεταφοράς δεδομένων μεταξύ της χύριας μνήμης και του επεξεργαστή μειώνεται σημαντικά, κάτι το οποίο επιδρά θετικά στην κατανάλωση ισχύος και την επιτεύξιμη απόδοση του συστήματος. Κινούμενοι προς αυτήν την υπόθεση, στην διατριβή αυτή εξερευνούμε το NDP παράδειγμα για επεξεργαστές υψηλής απόδοσης αλλά και για επεξεργαστές χαμηλούς ισχύος. Όσον αφορά του επεξεργαστές υψηλής απόδοσης, προτείνουμε μία προσέγγιση στην οποία λαμβάνουμε υπ' όψη μας την εκτέλεση βρόγχων γενικού σκοπού. Η αρχιτεκτονική την οποία προτείνουμε κάνει χρήση μίας μεθοδολογίας χρονοδρομολόγησης εντολών, κατά την οποία η κάθε εντολή του βρόγχου εκδίδεται σε ένα ειδικά προσαρμοσμένο ολοκληρωμένο κύκλωμα που έχει τον ρόλο του επιταχυντή της εκτέλεσης του βρόγχου. Το κύκλωμα αυτό τοποθετείται στο λογικό επίπεδο μίας κύριας μνήμης υβριδικού κύβου (HMC). Στο επίπεδο αυτό οι εντολές εκτελούνται επαναληπτικά και παράλληλα, με έναν τρόπο που θυμίζει αυτόν της επικάλυψης λογισμικού, ενώ τα ενδιάμεσα παραγόμενα αποτελέσματα παροχετεύονται δια μέσου ενός δικτύου διασύνδεσης που βρίσκεται πάνω στο ολοκληρωμένο χύχλωμα. Όσον αφορά τις αρχιτεχτονιχές χαμηλής χατανάλωσης ισχύος, αναπτύσσουμε μία καινοτόμο μεθοδολογία ανάλυσης χρονισμού, η οποία βασίζεται στις αρχές του STA και προσανατολίζεται συγκεκριμένα προς συστήματα χαμηλών προδιαγραφών και χαμηλής κατανάλωσης ενέργειας. Η μεθοδολογία αυτή λαμβάνει υπ' όψη της την διέγερση των διαδρομών χρονισμού της κάθε εντολής που υποστηρίζεται από το σετ εντολών του επεξεργαστή (ISA) και υπολογίζει την καθυστέρηση της χειρότερης περίπτωσης για την κάθε εντολή ξεχωριστά. Ως αποτέλεσμα, αντλούμε πληροφορίες για την χρονική καθυστέρηση σε επίπεδο εντολής και εκμεταλλευόμαστε την πληροφορία αυτή ώστε να κλιμακώνουμε την συχνότητα του ρολογιού δυναμικά, ανάλογα με τον τύπο εντολής που εκτελείται στο κύκλωμα σε κάθε χρονική στιγμή. Στην συνέχεια χρησιμοποιούμε την μεθοδολογία που περιγράψαμε για να συν-σχεδιάσουμε μία αρχιτεκτονική, με γνώμονα την δυναμική μεταβολή της συχνότητας του ρολογιού του επεξεργαστή η οποία

εκτείνεται στον βαθμό λεπτομέρειας του κύκλου μηχανής. Επικεντρωνόμαστε ξανά στην εκτέλεση κώδικα γενικού σκοπού και υλοποιούμε συνδυαστικά τη αρχιτεκτονική στο λογικό επίπεδο μίας μνήμης τύπου HMC ώστε να καταστήσουμε ικανό το σύστημα μας για εκτέλεση εντολών δίπλα στην μνήμη τυχαίας προσπέλασης. Επιλέγουμε να αξιολογήσουμε τις αρχιτεκτονικές που υλοποιήσαμε (της υψηλής απόδοσης αλλά και της χαμηλής κατανάλωσης ισχύος) σε επίπεδο υλοποίησης ολοκληρωμένου κυκλώματος σύμφωνα με τα πρότυπα της βιομηχανίας ώστε να ενισχύσουμε την εγκυρότητας της μεθοδολογίας μας. Τα αποτελέσματα τα οποία παίρνουμε υποδεικνύουνε μία μεγάλη αύξηση της απόδοσης του συστήματος όσον αφορά την επιτάχυνση της λειτουργίας του σε σύγκριση με την αρχική αρχιτεκτονική, ενώ η κατανάλωση ισχύος πέφτει σε πολύ χαμηλά επίπεδα.

# Acknowledgements

I would like to express my sincere gratitude to Prof. George Dimitriu for his continuous support of my Ph.D study and related research, for his motivation and for his intelligent recommendations. His advices, counseling and analytical suggestions constitute for me not only a source of inspiration, but also play a major role on the concepts incorporated within this work. He also assisted me meticulously with the writing process of this dissertation and I think that the realization of this work would be very difficult if not impossible, if it weren't for his help.

I would also like to thank Prof. George Stamoulis for his thoughtful guidance through this period of time. He managed to impart remarkable knowledge and to elaborate on concepts which are more than important for the research process. He has made several scientific remarks and contributions to this thesis for which I am grateful. He also provided substantial supervision during the research and oversaw the writing process.

Besides Prof. George Dimitriu and Prof. George Stamoulis, I would like to thank the rest of my thesis committee: Prof. Nestor Evmorfopoulos, and Prof. Athanasios Loukopoulos, for their insightful comments, encouragement, but also for their remarks which motivated me to broaden my research subject and to explore different perspectives. My sincere thanks also goes to the other committee members for accepting the invitation.

Finally, I thank everyone who assisted, supported and encouraged me during this process of exploration, experimentation and hard work.

# Contents

| De | eclara     | tion of .      | Authorship                                                       | iii      |

|----|------------|----------------|------------------------------------------------------------------|----------|

| Ał | ostrac     | t              |                                                                  | vii      |

| Gı | reek A     | bstrac         | t                                                                | ix       |

| Ac | know       | ledgem         | ients                                                            | xi       |

| 1  |            | oductio        |                                                                  | 1        |

|    | 1.1        |                | uction                                                           | 1        |

|    | 1.2<br>1.3 |                | butions                                                          | 2<br>3   |

| 2  | Near       | r data p       | processing for high performance architectures                    | 5        |

|    | 2.1        |                | uction                                                           | 5        |

|    | 2.2        | Relate         | d work                                                           | 5        |

|    | 2.3        | Backg          | round                                                            | 7        |

|    |            | 2.3.1          | Hybrid memory cube organization                                  | 7        |

|    |            | 2.3.2          | CGRA architecture                                                | 8        |

|    | 2.4        | NDP f          | for general purpose applications                                 | 8        |

|    |            | 2.4.1          | CGRA microarchitecture for general purpose instruction execution | 9        |

|    |            | 2.4.2          | Loop pipelining for the CGRA microarchitecture                   | 11       |

|    |            | 2.4.3          | Instruction issue for the CGRA                                   | 11       |

|    |            | 2.4.4          | Loop execution on the CGRA                                       | 13       |

|    | 2.5        | · ·            | nentation                                                        | 15       |

|    |            | 2.5.1          | System architecture                                              | 15       |

|    | 0.6        | 2.5.2          | NDP design space exploration and layout                          | 16       |

|    | 2.6        | · ·            | mental evaluation                                                | 20       |

|    |            | 2.6.1          | Normalized speedup                                               | 20       |

|    |            | 2.6.2<br>2.6.3 | Energy reduction                                                 | 23<br>24 |

|    |            | 2.6.3          | Power and area efficiency                                        | 24<br>26 |

|    |            | 2.6.5          | Comparison with related works                                    | 20<br>26 |

| 3  | Timi       | ing ana        | lysis for low power pipelines                                    | 29       |

| •  | 3.1        |                | uction                                                           | 29       |

|    | 3.2        |                | d word                                                           | 30       |

|    | 3.3        |                | round                                                            | 32       |

|    |            | 3.3.1          | Static and dynamic timing analysis                               | 32       |

|    | 3.4        | Timing         | g analysis in processor datapaths                                | 32       |

|    |            | 3.4.1          | The instruction path exhaustive timing analysis concept          | 32       |

|    |            | 3.4.2          | Dynamic opcode value changes compensation                        | 33       |

|    | 3.5        | Clock          | scaling of RISC-V using IPE-STA                                  | 35       |

|    |            |                |                                                                  |          |

|    |       | 3.5.1          | Adaptive clock scaling in pipelined Processors                                                        | 35       |

|----|-------|----------------|-------------------------------------------------------------------------------------------------------|----------|

|    |       | 3.5.2          | Scaling clock by opcodes                                                                              | 36       |

|    |       | 3.5.3          | Dynamic Clock Scaling Mechanism                                                                       | 38       |

|    | 3.6   | Implei         | mentation                                                                                             | 40       |

|    |       | 3.6.1          | RISC-V processor parameters                                                                           | 40       |

|    |       | 3.6.2          | CAD toolflow and simulation                                                                           | 41       |

|    |       | 3.6.3          | Clock tree synthesis                                                                                  | 42       |

|    | 3.7   | Experi         | imental evaluation                                                                                    | 43       |

|    |       | 3.7.1          | Normalized speedup                                                                                    | 43       |

|    |       | 3.7.2          | Normalized power consumption                                                                          | 44       |

|    |       | 3.7.3          | Overhead of the IPE-STA methodology                                                                   | 45       |

|    |       | 3.7.4          | PVT tolerance considerations                                                                          | 46       |

| 4  | N     |                |                                                                                                       | 40       |

| 4  |       |                | processing for low power architectures                                                                | 49       |

|    | 4.1   |                | uction                                                                                                | 49       |

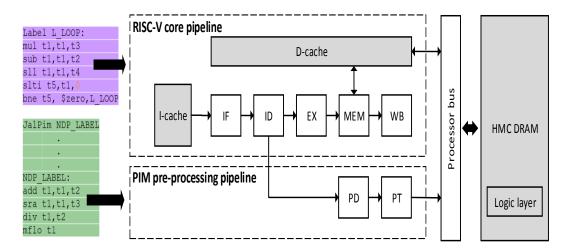

|    | 4.2   |                | System Architecture                                                                                   | 49       |

|    |       | 4.2.1          | Host system architecture                                                                              | 49       |

|    | 1 2   | 4.2.2          | PIM core architecture                                                                                 | 50       |

|    | 4.3   |                | C-NDP co-design methodology                                                                           | 53       |

|    |       | 4.3.1<br>4.3.2 | Application of IPE-STA to the PIM core         PIM core microarchitecture with adaptive clock scaling | 53<br>54 |

|    | 4 4   |                |                                                                                                       |          |

|    | 4.4   | 4.4.1          | mentation                                                                                             | 56<br>56 |

|    |       | 4.4.1          | Design space exploration and parameter considerations                                                 | 50<br>57 |

|    |       | 4.4.2          | CAD toolflow and simulation                                                                           | 57       |

|    |       | 4.4.3          | Adaptive clock scaling with multiple clocks                                                           | 58       |

|    | 4.5   |                | Area and power budget                                                                                 | 58       |

|    | 4.3   | 4.5.1          | Workload characterization                                                                             | 58       |

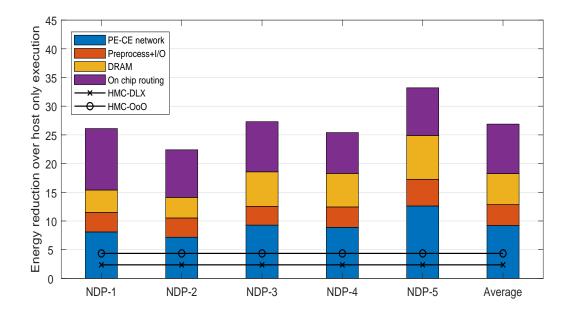

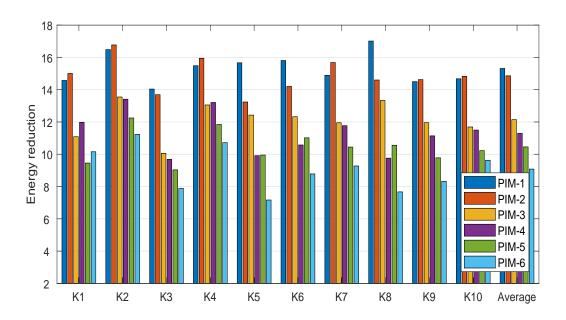

|    |       | 4.5.1          |                                                                                                       | 50<br>59 |

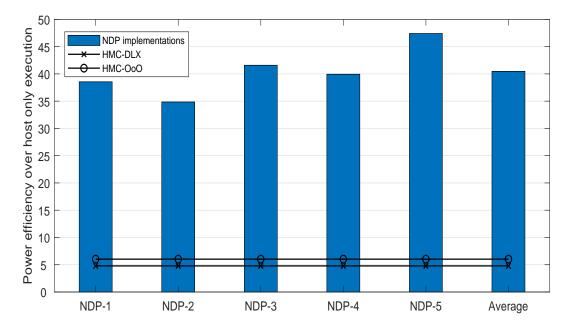

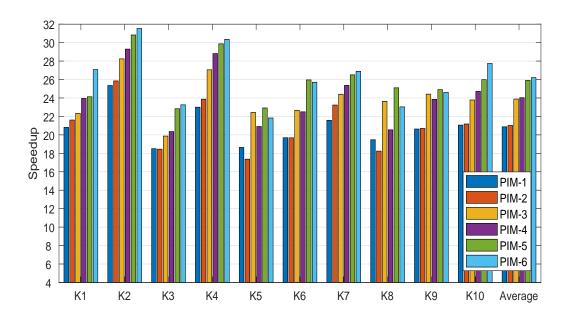

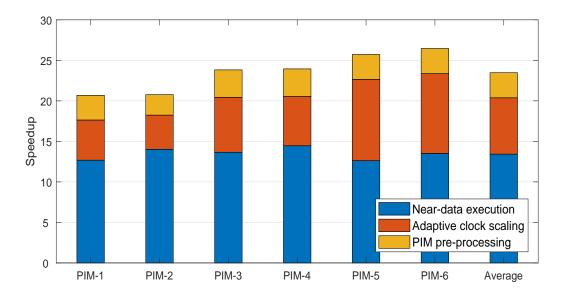

|    |       | 4.5.2          | Normalized speedup                                                                                    | 59<br>61 |

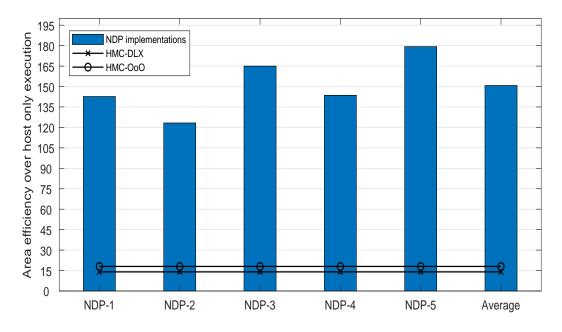

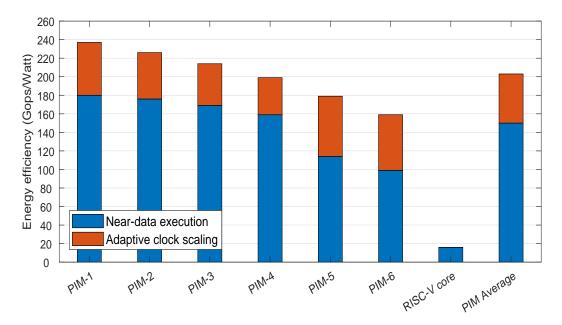

|    |       | 4.5.3          | Normalized energy reduction         Energy efficiency                                                 | 61       |

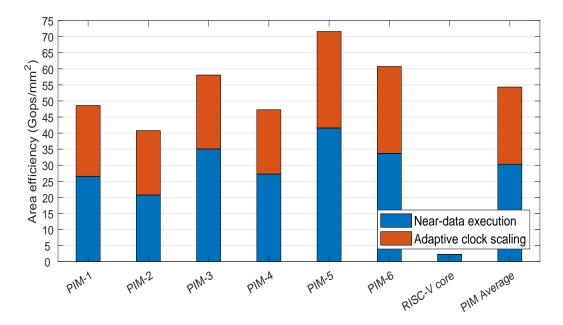

|    |       | 4.5.4          | Area efficiency                                                                                       | 62       |

|    |       | 4.5.5          |                                                                                                       |          |

| 5  |       |                | s and Future Directions                                                                               | 65       |

|    | 5.1   |                | usions                                                                                                | 65       |

|    | 5.2   | Future         | Directions                                                                                            | 66       |

| A  | Rele  | vant Pu        | ublications                                                                                           | 67       |

|    |       |                | blications                                                                                            | 67       |

| Ri | bligg | raphy          |                                                                                                       | 69       |

|    | SHORI | apity          |                                                                                                       | 5)       |

# **List of Figures**

| 2.1  | Architecture diagram of HMC DRAM.                                            | 8  |

|------|------------------------------------------------------------------------------|----|

| 2.2  | The proposed CGRA grid architecture deployed on the logic layer of the       |    |

|      | HMC DRAM.                                                                    | 9  |

| 2.3  | PE microarchitecture.                                                        | 11 |

| 2.4  | The loop pipelining optimization.                                            | 12 |

| 2.5  | The outcome of the instruction issue process after which each operation is   |    |

|      | issued on a PE.                                                              | 14 |

| 2.6  | Instruction execution instance on CGRA microarchitecture.                    | 15 |

| 2.7  | System architecture for general purpose NDP.                                 | 16 |

| 2.8  | The speedup improvement of the proposed NDP implementations for each         |    |

|      | kernel normalized to the host processor execution time.                      | 21 |

| 2.9  | Host processor-HMC data transfer reduction and its contribution to the nor-  |    |

|      | malized speedup of each NDP implementation.                                  | 22 |

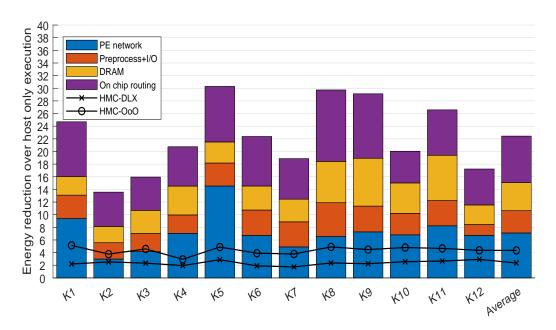

| 2.10 | Normalized energy reduction of the NDP methodology.                          | 23 |

|      | Energy consumption breakdown of NDP implementations.                         | 24 |

|      | Normalized power efficiency of the NDP implementations.                      | 25 |

|      | Normalized area efficiency of the NDP implementations.                       | 26 |

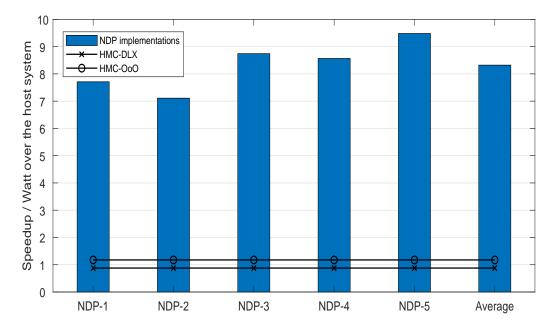

|      | Speedup per Watt of each NDP implementation.                                 | 27 |

|      |                                                                              |    |

| 3.1  | An instruction execution instance of the Rocket core implementation display- |    |

|      | ing the minimum operational clock period during each stage                   | 38 |

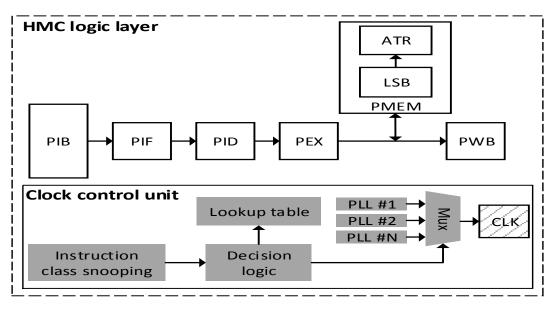

| 3.2  | The clock control unit integrated in the rocket core                         | 39 |

| 3.3  | Unstable clock behavior due to subsequent clock selections                   | 39 |

| 3.4  | The clock instability compensation technique.                                | 40 |

| 3.5  | The configuration parameters of both processor implementations               | 41 |

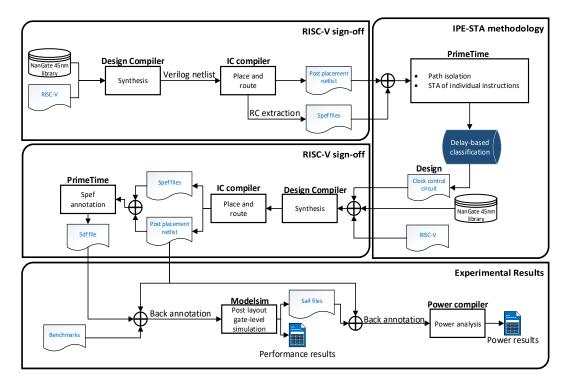

| 3.6  | The CAD toolflow for the IPE-STA methodology.                                | 42 |

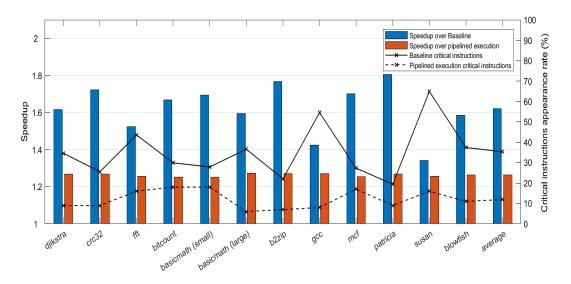

| 3.7  | Normalized throughput improvement and critical instruction appearance rate   |    |

|      | of the proposed design methodology compared to the corresponding baseline    |    |

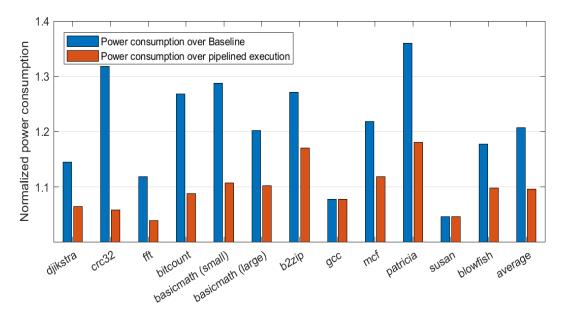

|      | processors                                                                   | 43 |

| 3.8  | Normalized power consumption increase of the proposed methodology com-       |    |

|      | pared to the baseline processors.                                            | 45 |

|      |                                                                              |    |

| 4.1  | The host system architecture composed by the BOOM core and the PIM pre-      | -  |

|      | processing pipeline.                                                         | 50 |

| 4.2  | The PIM core architecture                                                    | 51 |

| 4.3  | An instruction execution instance of the PIM core depicting the minimum      |    |

|      | operational clock period during each stage.                                  | 55 |

| 4.4  | The CCU implemented on the PIM core in the HMC logic layer.                  | 55 |

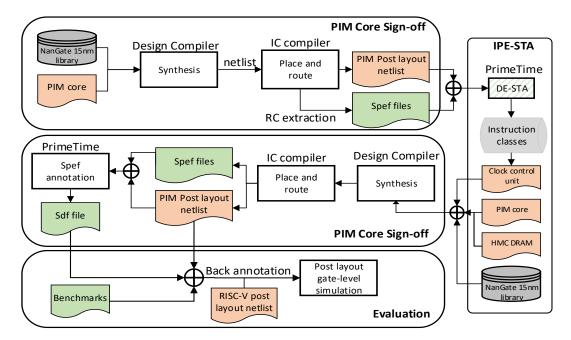

| 4.5  | Toolflow of the IPE-STA methodology for the PIM core                         | 57 |

| 4.6  | Normalized speedup of each PIM core implementation over the baseline         |    |

|      | RISC-V pipeline.                                                             | 59 |

| 4.7  | Impact of different design techniques on each PIM core speedup factor        | 60 |

|      |                                                                              |    |

| •   |  |

|-----|--|

| XV1 |  |

| 4.8  | Normalized energy reduction of each PIM core implementation over the       |    |

|------|----------------------------------------------------------------------------|----|

|      | baseline RISC-V pipeline.                                                  | 61 |

| 4.9  | Energy efficiency of the PIM core and RISC-V core pipeline implementations | 62 |

| 4.10 | Area efficiency of the PIM core and RISC-V core pipeline implementations . | 63 |

# **List of Tables**

| 2.1 | Key parameters of the host processor die and of the HMC implementations.        | 17 |

|-----|---------------------------------------------------------------------------------|----|

| 2.2 | PE and CE post-layout requirements in terms of area, power and latency.         | 18 |

| 2.3 | Implementation parameters of 5 different NDP designs.                           | 18 |

| 2.4 | Workload characterization.                                                      | 20 |

| 2.5 | Comparison of the proposed NDP architectures with the current state of the art. | 27 |

| 3.1 | Analysis of the instruction classes of the RISC-V Rocket core architecture.     | 37 |

| 3.2 | The clock periods for critical instructions along with the typical clock period |    |

|     | for the Rocket core implementation.                                             | 37 |

| 3.3 | Throughput improvement comparison between Application-adaptive guard-           |    |

|     | banding and IPE-STA.                                                            | 44 |

| 3.4 | Throughput improvement comparison between Blueshift OpenSPARC, Ra-              |    |

|     | zor and IPE-STA methodology.                                                    | 44 |

| 3.5 | The power and area overhead of the clock control and instruction snooping       |    |

|     | circuits in comparison to RiscV                                                 | 45 |

| 3.6 | Area overhead comparison between IPE-STA methodology and the state of           |    |

|     | the art                                                                         | 46 |

| 3.7 | Time requirements of DTA, STA and IPE-STA to complete the timing anal-          |    |

|     | ysis of RiscV pipeline.                                                         | 46 |

| 4.1 | Instruction class IPE-STA analysis of PIM core architecture for different sup-  |    |

|     | ply voltages                                                                    | 54 |

| 4.2 | NDP design parameters                                                           | 56 |

| 4.3 | Area and power requirements of the RISC-V and PIM core implementations .        | 58 |

| 4.4 | Workload characterization                                                       | 59 |

# **List of Abbreviations**

| BTWC    | Better Than Worst Case              |  |

|---------|-------------------------------------|--|

| TS      | Timing Speculation                  |  |

| PVT     | Process Voltage Temperature         |  |

| ISA     | Instruction Set Architecture        |  |

| STA     | Static Timing Analysis              |  |

| DTA     | Dynamic Timing Analysis             |  |

| IPE-STA | Instruction Path Exhaustive STA     |  |

| DRAM    | Dynamic Random Access Memory        |  |

| PIM     | Process In Memory                   |  |

| NDP     | Near Data Processing                |  |

| TSV     | Trough Silicon Via                  |  |

| HMC     | Hybrid Memory Cube                  |  |

| CGRA    | Coarse-grained Reconfigurable Array |  |

| PE      | Processing Element                  |  |

| CE      | Control Element                     |  |

| 000     | Out of Order                        |  |

| SSD     | Solide State Drive                  |  |

| ILP     | Instruction Level Parallelism       |  |

| LP      | Loop Pipelining                     |  |

| RaW     | Read After Write                    |  |

| RF      | Register File                       |  |

| MMU     | Memory Management Unit              |  |

| VC      | Vault Controller                    |  |

| SoC     | System-on-Chip                      |  |

| IPC     | Instruction Per Clock               |  |

| HPC     | High Performance Computing          |  |

|         |                                     |  |

Dedicated to everyone who assisted me in translating this research conception into an engineering realization.

# Chapter 1

# Introduction

## 1.1 Introduction

Traditional processors employ the standard Von Neumann architecture which separates the core pipeline from the main memory, while the communication between such entities is handled through an off-chip bus interface. This approach has been adopted by both the academia and industry and it has evolved into a well established paradigm that drives the contemporary design methodologies of integrated circuits. Furthermore, the continuous shrinking of transistor size seems to confirm Moore's law which indicates that the number of transistors in a dense integrated circuit will double about every two years. Moore's Law, coupled with Dennard scaling [1] has led to a stable increase in the processor core count and to proportional performance scaling over the last 20 years. Consequently, the resulting computer architecture paradigm focuses on multi-core or many-core systems, on pipeline optimizations and on parallelism exploitation to drive the evolution of the market processors.

As Dennard's scaling stops mainly due to supply voltage limits and leakage power drain, power densities rapidly increase on the chip and benefits of multi-core scaling begin to abate well before we hit the physical manufacturing limits. Therefore the industry races down the multi-core path and the dark silicon phenomenon [2] emerges. Under the dark silicon effect, the cores in a multi-core processor cannot be functional at the same time due to the lack of energy efficiency and thus, the performance scaling of the CPUs begins to decelerate. As the essential question of "how much more performance can be extracted from the multi-core path in the near future" [2] is formulated, latest research concludes that large performance workload variations are to be expected in present-day computer architectures [3] [4]. Such inherent variations may lead to unpredictable and sub-optimal performance in tightly coupled applications.

Nowadays computer architecture research suggests that the Von Neuman model begins to realize its upper limit in terms of power and throughput, while the performance bottleneck is shifting away from the core pipeline to the DRAM [5]. More specifically, the long DRAM latency and the costly data transfer between the CPU and the DRAM severely affect the energy consumption and throughput of computing systems. In order to alleviate such a scaling wall, researchers have proposed the adoption of the NDP paradigm in which the computations are moved near the DRAM silicon die. NDP promises to decrease the CPU-DRAM transactions and thus, to minimize the energy consumption of the system while also maintaining a very high throughput compared to the core pipeline.

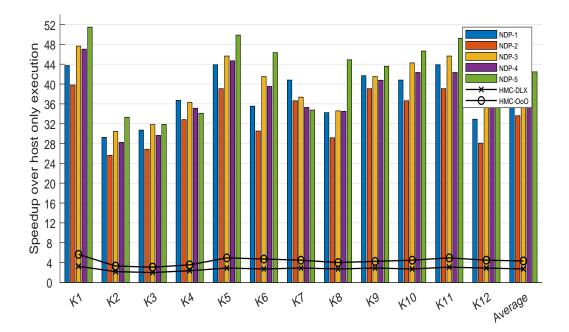

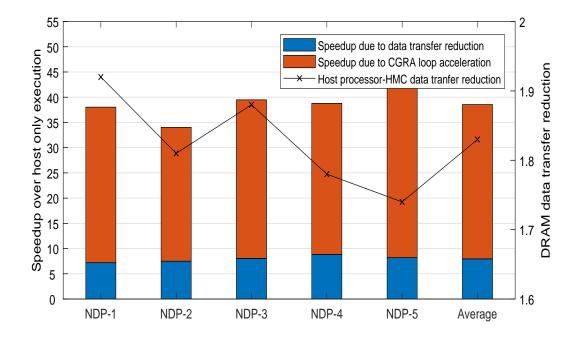

In this work, we explore the premises and prospects of the NDP computing paradigm in both HPC and low power computing domains. To this end, we propose a novel high performance NDP design for general purpose applications that executes instructions on the logic layer of a 3D-stacked DRAM. Under this premise, we deploy a network of functional units within a mesh interconnection network in conjunction with an instruction scheduling methodology which is tailored to minimize the dark silicon phenomenon. To achieve this, we focus our efforts on a high functional unit utilization rate and low power constraints, both of which diminish the dark silicon effect. The proposed design methodology issues one instruction on each functional unit and propagates the intermediate results through the mesh interconnection network. In this sense, loop execution resembles the software-pipelining paradigm, as each loop instruction executes iteratively in a dedicated functional unit near the DRAM. As a result we manage to obtain a theoretical throughput of one loop iteration per clock cycle while avoiding the costly CPU-DRAM data transactions. We evaluate our methodology by conducting a detailed design space exploration in a post-layout simulation environment using the standard industry CAD toolflow. Results indicate a speedup of 42x and an energy reduction of 22.4x over a high performance OoO CPU.

Considering the NDP for low power computer architectures we shift our focus on low-end small pipelines which are designed for reduced energy consumption. In order to efficiently implement a low-power NDP system we develop a novel timing methodology specifically targeting low-end pipelines and we explore a co-design approach between the proposed technique and the NDP paradigm. The rationale behind the low-end pipeline consideration is supported by the fact that in the Internet of Things era, the low-end processor domination of the embedded market is expected to be further reaffirmed. Then, a question will arise, on whether it is possible to enhance performance of such processors without the cost of high-end architectures. To this end, this part of our work focuses on frequency scaling and the study of related techniques which can boost processor performance with a low cost. Frequency scaling has been recently used in conjunction with the BTWC processor design paradigm. Traditional designs operate under worst-case timing constraints which avert incurring execution errors. However, such constraints impose heavy performance penalties. The BTWC designs are allowed to operate above their critical levels, but expensive error-correction hardware must then be incorporated, to fix any possible errors. Under this premise, we propose a BTWC methodology which enables the processor pipeline to operate at higher clock frequencies compared to the worst-case design approach. We employ a novel timing analysis technique, which calculates the timing requirements of individual processor instructions statically, while also considering the dynamic instruction flow in the processor pipeline. Therefore, using an appropriate circuit that we designed within this work, we are able to selectively increase clock frequency, according to the timing needs of the instructions currently occupying the processor pipeline. In this way, the error-free instruction execution is preserved without requiring any error-correction hardware. In the sequel we apply the proposed timing methodology on a low-end, low-power architecture that is implemented on the logic layer of an HMC DRAM. We design the system pipeline from the ground up to support the frequency scaling mechanism and we make the necessary modifications on the host system to facilitate a pre-processing pipeline that minimizes the power overhead of the NDP processing. Results demonstrate an average speedup factor of 23x with 12x reduction in energy consumption compared to the baseline implementation. We also show that the proposed methodology produces at least 9x times more energy efficient and 24.5x times more area efficient designs and we conclude that it significantly enhances the overall performance of the low-power NDP implementations.

## **1.2** Contributions

The main contributions of this work to the current state of the art are considered as follows:

We expand applicability of the NDP paradigm by designing and implementing an HPC NDP system for general purpose loop execution. In particular, we design the control and the processing elements as well as a forwarding unit that speedups the execution of general purpose loop bodies. We employ such a general purpose approach to allow any type of application to exploit the NDP technology, instead of focusing on an application specific methodology as most of previous works do.

- We provide an NDP instruction issue methodology which issues each loop body instruction on a single functional unit. In this way each functional unit executes one instruction iteratively until the loop execution completes and thus, the NDP throughput is maximized. We also make sure that the whole loop can be mapped on the functional units by optimizing the efficiency of the issue process.

- We propose a novel timing analysis methodology implemented on the circuit level which considers instruction opcodes for performance increase. Previous consideration of opcodes for performance increase has been compiler-only consideration or through the DTA technique.

- Our BTWC methodology accurately identifies the timing requirements of any incoming instructions. Since we are a priory aware of such constraints we do not deploy any error detection or error correction mechanisms and thus, the hardware implementation costs are significantly reduced.

- We co-design and implement an NDP architecture for low-end processors from the ground up, capable of facilitating the aforementioned methodology. We design the NDP architecture considering the processor low-power and low-area requirements, while also providing hardware support for the proposed timing analysis.

- We explore an NDP architecture-oriented approach to the BTWC design paradigm. Our work studies the NDP pipeline architecture to extract timing information based on the ISA of the processor. We consider this approach to have greater applicability, as it can be used on any processor without requiring to adjust or change the premise of our technique.

# 1.3 Outline

The following chapters of this dissertation are organized as follows. In chapter 2, we present our methodology for the HPC NDP architecture and we provide a detailed design space exploration in order to verify and evaluate the proposed technique. In chapter 3, we introduce the concept of timing analysis for low-end pipelines and we elaborate on the timing analysis approach we employ. In chapter 4 we discuss our co-design perspective between the NDP and the proposed timing analysis technique, and we provide the evaluation of the implemented architectures. Finally, chapter 5 concludes our work.

# Chapter 2

# Near data processing for high performance architectures

# 2.1 Introduction

Modern processor throughput encounters a scaling wall as the performance bottleneck has shifted from the core pipeline to the DRAM data transfer operations. To address such issue, researchers proposed the adoption of the NDP paradigm, in which the computations are moved near the DRAM silicon die. Nowadays there is a growing trend towards NDP research that focuses on application specific accelerators, while the general purpose paradigm has received relatively little attention so far. In this chapter we propose an NDP methodology for general purpose applications that targets high performance architectures with complex pipelines and complicated forms of control. Our design is optimized for loop acceleration under the general purpose computing paradigm, in order to cover a wide range of application types. In this sense, we do not employ NDP for application specific execution as previous works do, instead we focus on moving general purpose loop computations to the DRAM from the host system. The proposed architecture consists of a mix of PEs capable of executing simple arithmetic operations, CE that evaluate control statements and a mesh interconnection network that handles the communication between the deployed PEs. Typical CGRAs employ dynamic switching mechanisms that manage the flow of information within the mesh interconnection and thus, enabling the forwarding process between individual PEs. Our design diverges from the standard CGRA approach, as we opt for a scheduling methodology that issues each loop instruction on a single PE, by employing the loop pipelining optimization. Under this premise, the forwarding processes is not dynamically managed, instead it is statically configured to activate the forwarding streams that resolve the instruction data dependencies as they eventuate after the scheduling process completes. As a result, our design leverages the CGRA dataflow execution, but also utilizes a loop acceleration technique to further improve throughput and reduce the energy consumption. In order to verify our methodology we utilize a post-layout netlist of RISC-V OoO BOOM core and a post-layout implementation of a HMC DRAM architecture. Post-layout simulations on the NDP design demonstrate an average speedup factor of 42x, while the energy consumption is reduced by a factor of 22.4x over the host CPU execution.

# 2.2 Related work

Modern computer architectures are bound by energy constraints that impose heavy penalties on the system's throughput scaling capabilities. Such constraints derive not only from the high energy requirements of temporary storage circuits such as register files and cache memories, but also from the energy cost of data transfer operations to the DRAM, as previous work in [6] demonstrates. In order to alleviate such limitations, researchers have proposed to execute the computations closer to the data, i.e. to the DRAM. The concept of NDP has been explored in the past, as previous work in [7] shows, but due to technology limitations the applicability of such an approach was limited. Nowadays a resurgence in NDP research is observed mainly due to the appearance of TSV interconnections and 3D stacked memories, which are key enablers for the NDP concept, as mentioned in [7]. Despite the fact that previous work in [8] suggests that the adoption of NDP model can be accomplished without requiring 3D stacked memories, most of the ongoing research focuses on TSV and 3D RAM technologies to deliver near data computations. The NDP promises to alleviate the performance bottleneck imposed by the DRAM bus in modern processors as a previous survey in [9] elaborates and also to increase the performance-to-power ratio of modern processing systems [10]. In [9] researchers argue the existence of a performance wall due to the slow RAM - CPU communication and mention that such a wall leads to performance scaling problems. Although NDP seems a promising solution to the aforementioned scaling problem, there are some challenges that should be addressed, in order for this paradigm to be adopted in the industry. Such challenges include the optimization of NDP architectures, the memory coherence maintenance and the perseverance of the sequential programming model, as previous works in [7] [9] elaborate.

Under this premise, researchers mainly focus on a certain application type to perform NDP optimizations as previous work in [11] demonstrates. In that work authors deploy a near data graph processing accelerator achieving high throughput and reducing the power consumption, while also maintaining memory coherence by defining non-cachable memory spaces. Another work in [12] focuses on bitwise operation execution in memory, while in [13] authors propose an NDP framework for IoT applications. Big data applications are also suitable for NDP due to the increased memory bandwidth requirements they exhibit [14]. Authors in [15] use a HMC architecture to map computing kernels inside the memory network, leveraging in-network computing in data-flow style. CGRAs have also been proposed for the processing elements in NDP systems as in [16]. In that work researchers deploy a network of functional units in a mesh like structure for NDP applications while the proposed solution does not require any micro-architectural changes to the host processor. In other related work [17] authors incorporate heterogeneous reconfigurable logic arrays, which behave like CGRAs in order to improve throughput and reduce the power consumption of target applications. CGRA capabilities are also explored in [18] along with different TSV interconnection networks in order to find the optimal CGRA-TSV combination that leads to the higher speedup improvement. A common target application of CGRAs and NDP is the training and inference of deep neural networks as previous works in [19] and [20] demonstrate. In [19] authors deploy RISC-V cores in a mesh-like structure on the logic layer of an HMC, to provide a scalable architecture for deep neural network training and inference operations. Similarly, in [20] authors explore neural network optimizations to reduce the data transfer rates between the NDP cores and a non-volatile memory system, while also exploiting the parallel execution capabilities of an on-chip processing network to reduce training time. Non-volatile memory structures are considered ideal for hosting NDP processing due to their ability to behave both as storage and as processing units. Previous work in [21] proposes a query acceleration methodology that also reduces the energy consumption per operation on a non-volatile memory. Another work in [22] explores the application of the NDP framework for database operations in SSDs by employing data flow programming features and code reuse optimizations, while in [23] authors employ a near-memory hash table to speed up search operations in databases for big data.

Memory consistency and coherence is a major challenge for NDP systems. While some works declare certain memory spaces as non-cachable, like [11] mentioned above, others propose ways of maintaining memory coherence. In particular, in [24] authors combine a speculative cache coherence and a compressed signature technique, in order to reduce the overhead of DRAM coherence maintenance with the host system. On the other hand, however, researchers in [25] argue that non-restricted memory regions can often lead to a significant amount of coherence traffic, and thus, a good practice would be to avoid cachable memory blocks.

The concept of programming transparency is explored in [26], where researchers build a GPU framework for NDP that automatically selects the computations to be offloaded to NDP cores, while mapping the instructions on the available processing elements. In this way, programmers are not involved in the offloading procedure and the sequential programming model is maintained. Similarly, in [27] authors exclude the programmer from making decisions on near data execution, instead an automatic mechanism migrates the computations to NDP units, according to the observed levels of data locality. Also in [28] an NDP solution is proposed for heterogeneous systems that provides application transparency, while utilizing the processing power of the SSD devices for NDP operations.

To the best of our knowledge, there is no such a work proposed so far. Previous works in [11] [12] [13] [14] [19] [20] [21] [22] and [23] authors propose NDP frameworks for specific application types, and thus their designs take into account the requirements of the corresponding applications, while our work focuses on general purpose loop acceleration. In [10] [15] [26] [27] [28] [29] and [30] authors propose NDP architectures for general purpose applications but their approach does not include CGRAs, instead they rely on processor pipelines and task-specific accelerators to increase the system performance. In [31] researchers focus on diverse kernel workloads, but their CGRA network design is based on the profiling results of the executing kernels. On the contrary, our work does not require any profiling operation prior to code execution due to the fact that the CGRA is designed for loop acceleration and thus, it can support any issued loop without additional effort. Further, authors in [8] [16] [17] and [18] utilize CGRAs in conjunction with the NDP paradigm but their focus shifts to different aspects of the NDP execution paradigm. Under this premise, previous works lack the application mapping approach or the loop acceleration focus we employ as they do not utilize the CGRA network to execute instructions in an iterative way, i.e. to issue an instruction per processing element. To this end, they rely on run-time reconfiguration techniques [17], memory data buffer exploitation [8] and exploration of TSV interconnection microarchitectures [16] [18] to enable the NDP processing and to increase the throughput of the system.

## 2.3 Background

#### 2.3.1 Hybrid memory cube organization

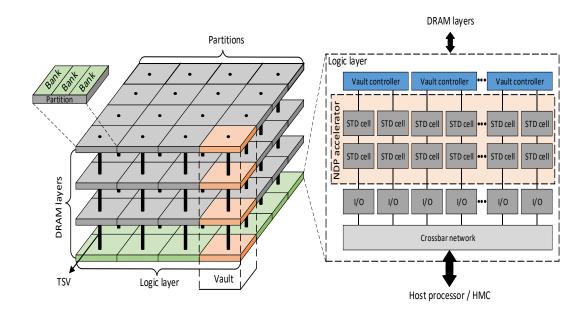

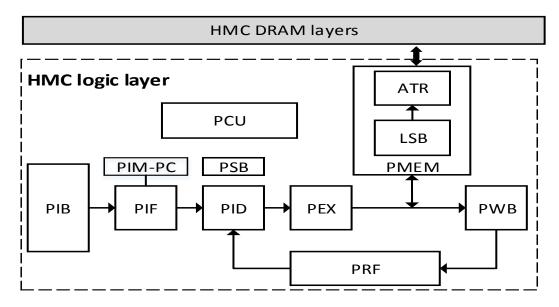

HMC architectures are widely adopted by NDP paradigms as previous work in [32] shows, mainly due to the 3D-stacked DRAM layers they employ. An HMC DRAM consists of multiple DRAM layers and achieves much greater internal bandwidth than conventional DRAMs, due to the TSVs, which are vertical links that connect the multiple layers of a DRAM stack together. Figure 2.1 depicts the architecture of a HMC DRAM as described according to the HMC specification in [33]. HMC is organized in vertically structured memory vaults which consist of partitions. Each partition contains a number of banks which store the DRAM data. The lower DRAM layer is reserved for implementing logic and facilitates vault controllers that manage the data transfer process between the corresponding vaults. Vault controllers also internally handle the refresh operations of each vault, removing this responsibility from the host memory controller. In order to support high BW within its vaults, HMC utilizes TSVs that connect vertically the vault layers and redirect data to the vault controllers. In this work we employ the NDP paradigm and thus, we also adopt the aforementioned HMC hierarchy.

FIGURE 2.1: Architecture diagram of HMC DRAM.

## 2.3.2 CGRA architecture

CGRAs are frequently employed as hardware accelerators due to the increased performance to area ratio they achieve [34]. A typical CGRA grid consists of a number of PEs arranged in a 2D array structure. The processing elements are designed to execute basic arithmetic or logical operations while their communication is managed by an interconnection network. Previous work in CGRAs usually focuses on targeted applications such as Givens Rotation acceleration [35], convolution neural network applications [36], deep neural networks [19] and wireless telecommunication receiver algorithms [37]. Such designs are proven to be very efficient in terms of performance to area ratio, but their operation is restricted within specific application types. In contrast, CGRA related work that treats them as general purpose architectures often focuses on the instruction mapping procedure of the accelerator [38]. As a result, CGRA architectures tend to exploit local data reuse [39], utilize a local register file of the PEs [40] and organize the instruction mapping process in an efficient way [41].

Despite the fact that such works deal with the routing and resource mapping problems of a CGRA network they employ complex scheduling algorithms which are not suitable to the NDP paradigm due to the restricted area and power requirements of NDP designs. Also when general purpose code execution is considered, the data forwarding and pipeline stalling tasks should be taken into consideration as general purpose applications usually display a great amount of data dependencies. Additionally general purpose code requires a lot of control statements which should be taken into account in order for the CGRA design to be efficient. We consider such requirements critical for designing the CGRA architecture and thus we incorporate them in the design process. Under this premise we design a novel CGRA architecture from the ground up capable of supporting near data general purpose loop execution. To this end, we opt for a static-scheduling static-dataflow (SSD) execution [42] in which each loop instruction is statically scheduled on a corresponding processing element while the execution process leverages the dataflow parallelism of the corresponding loop. We discuss the micro architecture details of such an architecture in the following section.

# 2.4 NDP for general purpose applications

Host processor bus

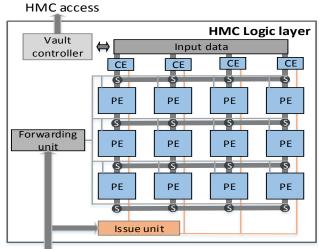

FIGURE 2.2: The proposed CGRA grid architecture deployed on the logic layer of the HMC DRAM.

#### 2.4.1 CGRA microarchitecture for general purpose instruction execution

The proposed CGRA microarchitecture focuses on adopting the general purpose execution paradigm, while also leveraging the dataflow parallelism offered by the CGRAs. Figure 2.2 depicts the architecture of a  $4 \times 4$  CGRA grid implemented on the logic layer of the HMC DRAM. The array consists of multiple PEs and CE organized in a mesh-like structure, and of an on-chip interconnection network capable of handling the communication among the PEs. Each PE is capable of executing arithmetic or logical operations and utilizes inputs either from the HMC DRAM or from the outputs of other PEs. Each CE is responsible for evaluating control statements that change the execution flow of the instruction sequence. The flow of data between the HMC and the CGRA is controlled by the vault controllers, which execute memory requests heading to the HMC DRAM. In order to manage the data transfer within the CGRA grid, we utilize switches that are designed to redirect data paths to designated PEs and CEs.

We will now discuss the microarchitecture of the units deployed on the CGRA grid. Since this work focuses on loop acceleration for general purpose execution, instructions scheduled on the CGRA units are assumed to be loop instructions. More specifically, the instructions scheduled constitute the pipelined body of a loop and are not changed until all loop iterations are finished. Our detailed model for loop pipelining and acceleration is presented later on.

**Issue unit:** The issue unit is responsible for the instruction issue process to the PE-CE grid. In order to avoid the power and area costs of a complex instruction issue circuit, we perform the scheduling process on the host processor as part of a pre-processing stage. The outcome of this process is transferred to the NDP architecture and specifically to the issue unit, which propagates the instruction operation codes and inputs to the corresponding PEs.

In the proposed NDP methodology, each PE is assigned multiple instructions but it may execute only one at any given time. In this sense the amount of the instructions that can be executed simultaneously is bound by the total amount of PEs-CEs. We take such a constraint into consideration when designing the issue unit, in order to maximize the amount of issued instructions along the CGRA, while also maximizing exploitation of ILP in instruction execution. Under this premise, we design the unit to schedule instructions, taking into account the control statements that disrupt the sequential code execution, such as if-else branches and nested loop iterations. Such statements always prohibit certain instructions from being executed, after the evaluation of the branch conditions takes place. For example a control statement enables the execution of the instructions in the if body or in the *else* body, but does not allow the execution of both if and *else* body sequences simultaneously. The same rule applies to the nested loop iterations as well. In order to exploit ILP in such cases, we design the issue unit to issue mutually exclusive instructions on the same PEs. Under this premise, a PE may execute an instruction that belongs to an if body, but also the same PE may execute an instruction that belongs to the side of the *else* body as well. Which instruction is actually executed depends on the evaluation of the branch condition. In this way, we not only allow more parallel instructions to be issued on the grid, but we also decrease the area requirements for our design, as we are able to issue more instructions in the same PE-CE die area.

**Forwarding unit:** The forwarding unit manages the forwarding and stalling processes by generating the necessary signals that propagate to the corresponding switches and PEs-CEs. After the issue process is complete, the data hazards between the PEs-CEs are known when the loop instructions are assigned to the corresponding PEs-CEs. Thus, the forwarding unit forwards the corresponding data to the appropriate CEs-PEs in order to eliminate data hazards. To accomplish this task, it generates control signals that propagate to the switching elements which act as multiplexors for the incoming data. As instructions and thus data dependencies do not change over consequent loop iterations, this process needs to be conducted at the beginning of the loop execution in order to open the corresponding data forwarding paths. Such data paths may change during the run time only when control statement evaluation results in a redirection of the instruction execution sequence flow. In this case the forwarding unit propagates the corresponding control signals in order to forward the required data to the dependent CEs-PEs. As a result, any unnecessary switching signals are omitted and dynamic power consumption is reduced. The forwarding unit also generates stall signals that freeze the instruction execution on specific PEs-CEs when necessary.

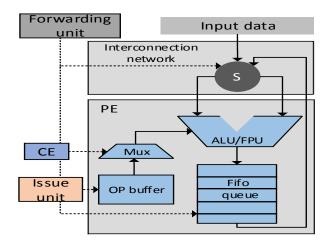

Processing element: The microarchitecture of a PE is depicted in Figure 2.3. Each PE is composed of an ALU or FPU unit capable of executing arithmetic or logical operations and two multiplexors that control the unit's input operands. Such inputs may originate from the DRAM, from other PE outputs or from the output of the same PE, depending on the data dependencies of the executing loop. To resolve such dependencies we utilize the forwarding unit which selects the appropriate inputs for each PE as described above. Each PE is assigned multiple instructions, but it may execute one operation per clock cycle. We modify the PEs so that the output of such an operation is temporarily stored to a fifo queue before propagated to the PE network. In the case of a stall the forwarding unit evokes the write privileges of the ALU/FPU output to the queue and thus, no new entries are stored. Each PE also contains a small operation buffer (OP buffer) for storing the assigned instructions for execution. As described above, each PE is assigned a number of instructions which cannot be executed simultaneously, for example different branches of an if-else statement. Such instructions are propagated through the issue unit to the PE network and are stored in the OP buffer of the corresponding PEs. In the sequel, the CEs control which operation the PEs will execute for each clock cycle via a multiplexor, depending on the evaluation of the branch condition.

**Control element:** We design the CEs dedicated to the execution of branch related instructions. We opt to implement dedicated units for executing comparison operations due to the high amount of control statements that are usually present within general purpose binaries. As a result, we consider the execution of such instructions in the PEs as inefficient due to the larger amount of power and area requirements of the PEs. To this end, each CE is a small unit capable of comparing two inputs and producing an output that reflects their relative value status. The microarchitecture of CEs is similar to the PEs as depicted in figure 3.3 with two distinct differences. First of all the ALU/FPU is replaced by a small comparator circuit which performs a comparison operation according to the assigned opcode, i.e. "greater than",

FIGURE 2.3: PE microarchitecture.

"less then", "equal" etc. Further, the fifo queue of each CE is smaller than the corresponding fifo queues of the PEs as the outputs of the CEs are not 32-bit or 64-bit wide. Also the comparison results which are stored in the fifo queue are forwarded to PEs, where they act as control signals for the multiplexors, in order to choose which instruction to execute from the OP buffer. As a result, the CE size and power consumption is significantly lower that the PE's and thus, we are able to incorporate more of them in the CGRA implementation.

#### 2.4.2 Loop pipelining for the CGRA microarchitecture

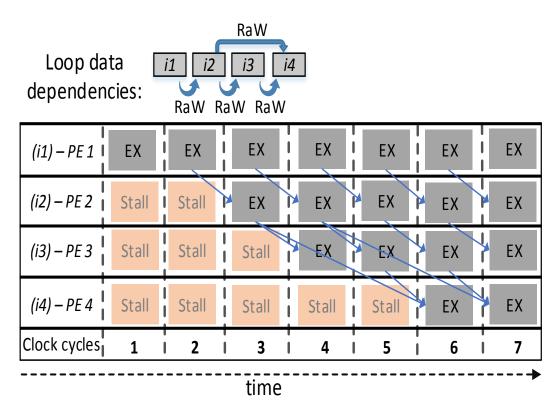

LP of software pipelining is a loop optimization technique that improves the performance of loop execution by overlapping consequent loop iterations and thus, hiding the underlying latency of each iteration. This form of pipelining is widely used as a compiler optimization technique. Previous work in [43] demonstrates that such a technique can also be efficiently mapped on CGRAs resulting in an drastic decrease in loop execution time and power consumption [44]. Previous work in [43] demonstrates that LP can also be efficiently mapped on CGRAs resulting in an drastic decrease in loop execution time and power consumption [45]. LP achieves such results by transforming the loop body in a way that hazards caused by the data dependencies between participating instructions, RaW are reduced. Loop data dependencies come into two forms, intra-loop and inter-loop. Intra-loop are data dependencies that appear within the same loop iteration, while inter-loop dependencies span from one iteration to another. Figure 2.4 depicts an example of software pipelining transformation for a simple loop that contains intra-loop RaW data dependencies. In this example the loop consists of four instructions: a memory operation instruction (mem) with 2 cc latency, an addition operation instruction (add) with 1cc latency, a multiplication operation instruction (mull) with 2cc latency and a subtraction operation instruction (sub) with 1cc latency. We use the variable x to denote the dependencies of each instruction within the iteration x. To this end, the *add* instruction depends on the execution of mem, the mull on the add and the sub on the mull and *add* as they process the same data space. In order to alleviate such dependencies, LP constructs a loop steady state so that it contains instructions from future iterations and may iterate with a reduced number of internal data hazards. The loop steady state is accompanied by a prologue which manages the setup process and an epilogue that waits for the remaining instructions to finish.

## 2.4.3 Instruction issue for the CGRA

|               |           |             | RaW          |             |

|---------------|-----------|-------------|--------------|-------------|

| Loop data     | mem (x)   | add (x)     | mull (x)     | sub (x)     |

| dependencies: | Ra        |             | a W          | RaW         |

| lter. 1:      |           |             |              |             |

| l Iter. 2:    | mem (2)   | prologue    |              |             |

| l Iter. 3:    | mem (3)   | add (1)     | ]            | l           |

| l Iter. 4:    | mem (4)   | add (2)     | mull (1)     | l           |

| lter. 5:      | mem (5)   | add (3)     | mull (2)     | <br>        |

| steady state  | mem (x+5) | add (x+3)   | mull (x+2)   | sub (x)     |

| lter. max     |           | add (max-1) | mull (max-2) | sub (max-4) |

| l Iter. max   | x-3:      | add (max)   | mull (max-1) | sub (max-3) |

| lter. max     | -2:       |             | mull (max)   | sub (max-2) |

| lter. max     | -1:       |             |              | sub (max-1) |

| lter. max     |           | epilogue    |              | sub (max)   |

FIGURE 2.4: The loop pipelining optimization.

| g  | orithm 1 The proposed instruction issue technique for the CGRA. |

|----|-----------------------------------------------------------------|

| p  | erform LP                                                       |

| W  | hile not converged do                                           |

|    | if Instr. No. < Issue slots then                                |

|    | unroll the loop                                                 |

|    | else if Instr. No. > Issue slots then                           |

|    | roll back the loop                                              |

|    | else if Instr. No. $==$ Issue slots OR tries $>$ threshold then |

|    | converge                                                        |

|    | end if                                                          |

| e  | nd while                                                        |

| G  | enerate control dependency graph                                |

| F  | orm mutually exclusive execution groups                         |

| G  | enerate data dependency graph                                   |

| f( | or mutually exclusive groups do                                 |

|    | get mutually exclusive instructions                             |

|    | map them in PEs OP buffers                                      |

| e  | nd for                                                          |

| f( | or rest of non-control instructions <b>do</b>                   |

|    | get data depended instructions                                  |

|    | issue them in neighboring PEs                                   |

| e  | nd for                                                          |

| f( | or control instructions <b>do</b>                               |

|    | get data depended control instructions                          |

|    | issue them in neighboring CEs                                   |

| e  | nd for                                                          |

Although the idea of the LP is not new, the mapping of LP to hardware accelerators is not a trivial process, as previous work in [46] demonstrate. In this work we focus on improving the throughput and the area efficiency of the CGRA grid and thus, we opt for an instruction issue methodology that takes advantage of the LP optimization and the PE-CE network presented in Section 2.4.1. We employ LP as it does not only reduce the RaW data hazards of the loop body, but it also generates a self contained loop steady state which may be efficiently scheduled. The proposed CGRA architecture consists of a grid of processing and control elements, with each PE containing an OP buffer. In this sense, each PE is assigned a number of instructions equal to the OP buffer size, provided that operations can be executed in a mutually exclusive way. Thus, each PE may execute only one instruction at any given time, but it may have been issued more. The total number of instruction issue slots equals to *number of PEs* × *OP buffer size*.

Algorithm 1 depicts the heuristic method we employ for mapping loop instructions onto the CGRA grid. We first perform LP optimization in order to minimize the data hazards from RaW dependencies, which are very common in general purpose loops. In the sequel, we analyze the number of instructions located in the steady state. If their number is less than the total number of free issue slots, we perform a loop unrolling operation. Loop unrolling is a loop optimization technique, in which the steady state of the loop is increased in size by adding instructions from future loop iterations. In contrast with LP, loop unrolling replicates the loop body and modifies the replicated instructions in order to refer to future iterations. In this way we increase the number of instructions that can be issued to the PEs while also reducing the execution time as we simultaneously execute instructions from future iterations. On the contrary if the amount of the steady state instructions is larger than the free issue slots, the loop cannot be issued and thus we reduce the steady state's size by rolling back the loop to a previous valid state. We repeat this process until the heuristic converges either by equalizing the steady state size with the number of issue slots or by reaching a preset repetition limit. In the sequel we generate the control dependency graph for the steady state of the loop. Such graph classifies the participating instructions into groups that can be executed in a mutually exclusive way. We issue instructions from the same groups, i.e. operations that are not executed in a mutually exclusive way to different CEs-PEs while instructions from different groups are issued on the same PEs provided that the corresponding OP buffers are not full.

The issue process also takes into consideration the data dependencies of the scheduled instructions. To this end, we generate the data dependency graph of the steady state instructions which provides information on the RaW dependencies of each operation. We prioritize the issue of instructions with data dependencies on neighboring CEs-PEs in order to reduce the data routing delays. If some instructions cannot be mapped to neighboring CEs-PEs due to the OP buffers being full, we map them as close as possible with the depended operation. After the PE scheduling completes the control statements of the loop are issued on the CEs . The scheduling procedure of the control instructions follows the greedy method for simplicity reasons. To this end, each control statement is issued on a single CE while taking into account the data dependencies between the data and control instructions in the same way as described above.

#### 2.4.4 Loop execution on the CGRA

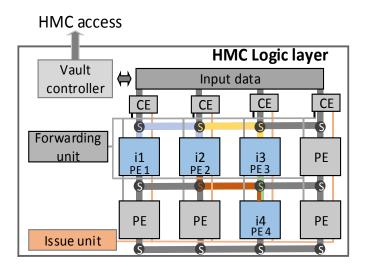

By employing the aforementioned methodology we manage to efficiently map the loop instructions on the CGRA network. Figure 2.5 depicts the outcome of the issue process after its application on the instruction sequence used in figure 2.4. The number notated by *i1* refers to the *mem* operation instruction, the *i2* to the *add*, the *i3* to the *mull* and the *i4* to the *sub* instruction. Data dependent instructions are issued on neighboring PEs and the forwarding unit generates the appropriate control signals, to conduct the data forwarding on the corresponding PEs. Following the data dependencies established in figure 2.4, PE-1 propagates its outputs to PE-2, PE-2 to PE-3 and PE-4, while PE-3 forwards the produced data to PE-4. The rest of the PEs are marked with gray color, since they are not assigned any instructions in this scenario. Under this premise, after the loop execution begins each PE iteratively executes one instruction that belongs in the loop body and thus, the CGRA produces the outputs of one loop iteration per clock cycle when the pipeline is filled.

Figure 2.6 depicts a run time instance of this loop after being issued on the CGRA grid. The data dependency constraints would normally dictate that instruction i4 should wait for both i2 and i3 to finish their execution so that the required inputs for i4 become available. As a result, i2 would not execute at the clock cycles 4 and 5 due to the fact that the produced output of the clock cycle 3 would be overwritten. Stalling *i*2 for 2cc creates a 2 cycle latency bubble that is propagated throughout the instruction sequence, resulting in throughput decrease and PE under-utilization. This problem is solved as we employ fifo queues capable of storing the outputs of each PE hence, enabling the PEs to continue executing instructions while previously generated outputs are not discarded. As a result, instruction i2 is never stalled, instead it continues its iterative execution, while its outputs are stored in the PE's fifo. In the sequel, instruction i4 is forwarded the corresponding results from the i2 and i3 fifo queue and thus, eliminating the need to stall the pipeline. We mark the forwarding process with blue arrows that depict the flow of data from the fifo queues to the inputs of the corresponding PEs. The aforementioned technique requires the CGRA pipeline to be full and the intermediate results to be stored in the fifo queues of the PEs. In this sense, after a certain amount of clock cycles, each PE will be able to execute one instruction per clock cycle achieving a theoretical maximum of 1 IPC per PE. Considering that the whole loop body is mapped on the CGRA array with each PE executing one instruction per clock cycle, we are able to execute one loop iteration per clock cycle, after the pipeline is filled.

Such a theoretical throughput estimation is affected by the depth of data dependencies of the loop body and the size of the PE fifo queues. Generally we avoid pipeline stalling when the RaW dependencies appear within a number of instructions equal or less to the amount of fifo slots available. For this reason the LP optimization is employed as discussed in the previous section. as it reduces hazards from the data dependencies in the loop steady state and thus, ensuring that the pipeline stalls are minimized. In order to make sure that any loop can be scheduled on the CGRA, we also equip the forwarding unit with a stalling mechanism

FIGURE 2.5: The outcome of the instruction issue process after which each operation is issued on a PE.

that is enabled when necessary. Nonetheless, we manage to greatly reduce the frequency of such a situation, when using the proposed instruction issue methodology.

# 2.5 Implementation

#### 2.5.1 System architecture

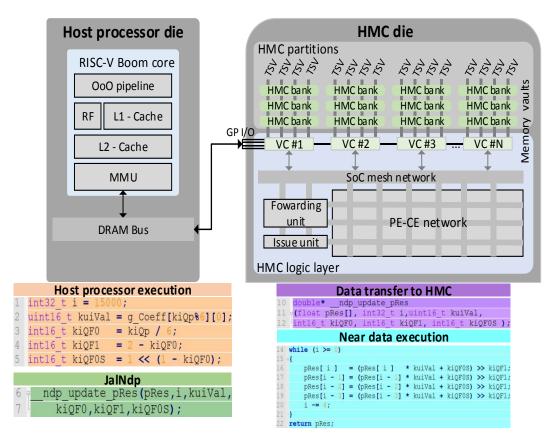

Figure 2.7 depicts the system architecture we propose for a general purpose NDP methodology. A host system is implemented consisting of a RISC-V CPU core with regular cache hierarchy, RF and a MMU. The host processor die also employs a bus capable of exchanging data with the HMC DRAM. We implement the HMC on a separate die and we design its logic layer to facilitate the NDP accelerator as described in section 2.4. We deploy a SoC mesh network to transfer data between the PE-CE network and the VCs which are responsible for the memory address translation and memory access operations. Each die operates independently from the other, while the communication between them is managed via the MMU and the processor bus.

In order to automate the NDP offloading procedure, we extend the RISC-V instruction set to facilitate the *jalNdp* (jump and link ndp) assembly instruction. This new instruction functions similarly to a *jal* instruction which is used for function calling. The key difference from *jal* is that *jalNdp* initiates the NDP preprocess operation and thus, offloads the instructions located in the function body to the NDP core. For code outside the function invoked through the *jalNdp* instruction, the HMC supports regular memory load/store operations.

In Figure 2.7 we also present a binary execution instance of the H264 encoding protocol. More specifically, the host processor executes the first part of the encoder, namely the part under the *host processor execution* label and above the *jalNdp* instruction. In the sequel, as the *jalNdp* instruction is executed, the NDP preprocess operation is conducted on the host system and accumulates the workload to be dispatched to the NDP core. Such a workload

FIGURE 2.6: Instruction execution instance on CGRA microarchitecture.

is composed of decoded instructions with their corresponding operands and data dependencies. Thus the instruction decoding and register fetching stages are executed on the host system. The pre-process operation also generates the data dependency graph and performs the scheduling technique as discussed in section 2.4.3. The resulting outputs include the instructions issued to the PE-CE network and the control signals required for NDP instruction execution. Such data is then transferred to the HMC via the processor bus and the GP I/O links that connect the host processor and HMC dies. On the DRAM side the loop is executed as described in section 2.4.4. In this scenario, the VCs access the memory banks according to the PE-CE load/store requests in order to fetch the required data and deliver them to the CGRA network via the SoC mesh. The switching elements of the SoC interconnect select the VC outputs that fit to each PE-CE memory request and forward the necessary data to the corresponding units. After the loop execution finishes, any outputs needed by the host code are transmitted back to the host system.

In order to maintain the sequential programming model, we stall the host processor pipeline until the NDP execution completes and the results are transferred back to the host die. In this way we enforce that any data dependencies between the executing loop and the rest of the instructions remain unbroken and the loop is executed in-order with the rest of the code. For memory coherence maintenance we consider certain parts of the DRAM uncachable and thus, no information is exchanged between the host cache and the HMC during the NDP execution.

#### 2.5.2 NDP design space exploration and layout

Table 2.1 depicts the host system and HMC design parameters. For the host system we implement a multi-core system that consists of four identical Berkeley Out-of-Order Machine

FIGURE 2.7: System architecture for general purpose NDP.

|                   | Host processor                     |  |  |

|-------------------|------------------------------------|--|--|

| Core              | RiscV Boom OoO, 1 GHz, 64 bit      |  |  |

| Amount of Cores 4 |                                    |  |  |

| Pipeline          | 10 stages, 4 issue width           |  |  |

| L1 cache          | 32 KB, 8-way, 4 cycle latency      |  |  |

| L2 cache          | 512 KB, 8-way, 12 cycle latency    |  |  |

| Branch prediction | gshare, 9-bit history, 512 entries |  |  |

| TLB size          | 512 entries                        |  |  |

|                   | HMC 8 GB                           |  |  |

| Memory vaults     | 32                                 |  |  |

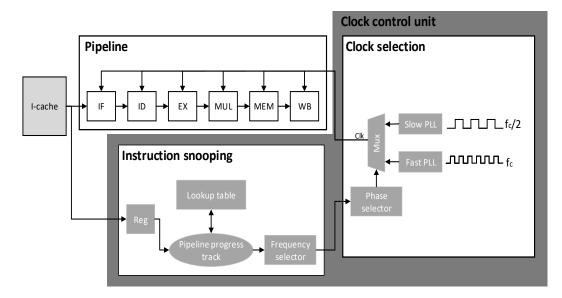

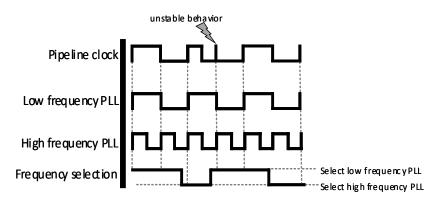

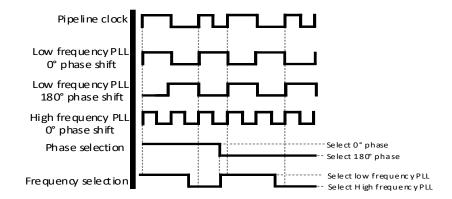

| Memory banks 512  |                                    |  |  |