## University of Thessaly

PhD Dissertation

## Exploiting Intrinsic Hardware Guardbands and Software Heterogeneity to Improve the Energy Efficiency of Computing Systems

Author:

Panagiotis Koutsovasilis

Supervisor: Christos D. Antonopoulos

Advising committee: Christos D. Antonopoulos, Nikolaos Bellas, Spyros Lalis

A dissertation submitted in fulfillment of the requirements for the degree of Doctor of Philosophy

to the

Department of Electrical and Computer Engineering

March 25, 2020

## Πανεπιστήμιο Θεσσαλίας

Διδακτορική Διατριβή

## Αξιοποίηση των Εγγενών Περιθωρίων Προστασίας του Υλικού και της Εγγενούς Ετερογένειας του Λογισμικού για τη Βελτίωση της Ενεργειακής Αποδοτικότητας των Υπολογιστικών Συστημάτων

Συγγραφέας: Παναγιώτης Κουτσοβασίλης Επιβλέπων: Χρήστος Δ. Αντωνόπουλος

Συμβουλευτική επιτροπή: Χρήστος Δ. Αντωνόπουλος, Νικόλαος Μπέλλας, Σπύρος Λάλης

Η διατριβή υποβλήθηκε για την εκπλήρωση των απαιτήσεων για την απονομή Διδακτορικού Διπλώματος

στο

Τμήμα Ηλεκτρολόγων Μηχανικών και Μηχανικών Υπολογιστών

25 Μαρτίου 2020

# Committee

| Christos D. Antonopoulos                                                        |

|---------------------------------------------------------------------------------|

| Associate Professor                                                             |

| Department of Electrical and Computer Engineering, University of Thessaly       |

| Advisor                                                                         |

| Nikolaos Bellas                                                                 |

| Associate Professor                                                             |

| Department of Electrical and Computer Engineering, University of Thessaly       |

| Advising Committee Member                                                       |

| Dimitris Gizopoulos                                                             |

| Professor                                                                       |

| Department of Informatics and Telecommunications, University of Athens          |

| External Committee Member                                                       |

| George Karakonstantis                                                           |

| Assistant Professor                                                             |

| Electronics, Electrical Engineering and Computer Science, Queen's University of |

| Belfast                                                                         |

| External Committee Member                                                       |

| Georgios Keramidas                                                              |

| Assistant Professor                                                             |

| Department of Informatics, Aristotle University of Thessaloniki                 |

| External Committee Member                                                       |

| Nectarios Koziris                                                               |

| Professor                                                                       |

| Electrical and Computer Engineering, National Technical University of Athens    |

| External Committee Member                                                       |

| Spyros Lalis                                                                    |

| Associate Professor                                                             |

| Department of Electrical and Computer Engineering, University of Thessaly       |

| Advising Committee Member                                                       |

"The reality we can put into words is never reality itself."

Werner Heisenberg

# Abstract

#### Panagiotis Koutsovasilis

Exploiting Intrinsic Hardware Guardbands and Software Heterogeneity to Improve the Energy Efficiency of Computing Systems

A key challenge for both current- and next-generation computing infrastructure deployments is to increase the delivered computational performance within stringent power budget constraints due to power delivery, cooling and cost-related concerns. Techniques such as transistor shrinking, frequency scaling, and parallelism exploitation have contributed to shaping the power efficiency envelope of today's computing systems. However, all of the aforementioned practices are bound to hit the power wall of CMOS technology. Another approach towards power efficiency is hardware-level specialization. Heterogeneous computing combines different architectures, each appropriate for specific computational patterns, within the same system. A typical example is General Purpose programming on Graphics Processing Units (GPGPU), which exploits GPUs to efficiently execute certain classes of embarrassingly parallel computations. Heterogeneous computing, though, comes at the expense of significantly increased programmer effort.

At the same time, chip manufacturers are introducing redundancy at various levels of CPU design to guarantee fault-free operation, even for worst case combinations of non-idealities in process variation and system operating conditions. This redundancy partly translates to CPUs operating at a higher voltage than what is strictly required, in the form of voltage margins. However, these worst case scenarios may appear only rarely or even not at all during the lifecycle of a given machine. Consequently, the operating voltage setting is overly pessimistic for typical operating conditions and leads to excessive power dissipation, which hinders the effort towards improving the power efficiency of computing infrastructures.

On the software side, programmers very often write code that solves problems at a significantly higher accuracy than actually required to meet the Quality of Service (QoS) requirements of the application. In the same vein, all parts of the code are treated as equally important, despite the fact that their contribution to the quality of the end result may vary significantly. As a result, developers tend to write programs that "over-compute", a practice which results in lower energy efficiency.

The quest for more energy-efficient systems may necessitate a transition from CMOS towards a more efficient semiconductor technology. However, until a new, commercially viable candidate technology appears, optimizing the energy efficiency of systems based on CMOS technology is a worthy undertaking. In this dissertation we focus on the exploitation of the intrinsic hardware guardbands and software heterogeneity. We design and develop mechanisms that reduce the CPU operating voltage and, thus, minimize the CPU power footprint by considering and exploiting the computational characteristics of the executed workload. Besides improving energy/power efficiency, these mechanisms can also be used to mitigate performance penalties induced on a power-constrained platform. We also evaluate the trade-off between quality of results and energy efficiency when combining heterogeneous computing with various approximation techniques. More specifically:

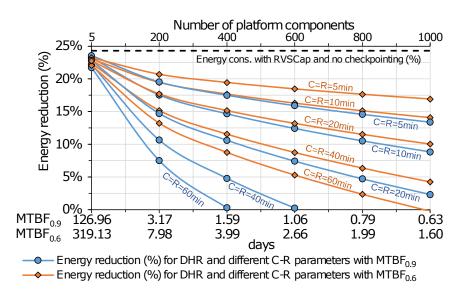

Power capping is commonly used to regulate the limited power resources of computing infrastructure deployments. We investigate the impact of reducing CPU voltage margins on the efficiency of software- and hardware-based power capping mechanisms on a variety of commercial, off-the-shelf platforms. We observe that operation at reduced voltage margins can significantly improve the efficiency of existing power capping mechanisms in terms of performance, CPU and system node power, as well as CPU temperature. Based on our investigation, we introduce a CPU power capping mechanism that preserves performance in power-constrained environments by operating the CPU at reduced voltage margins to reduce frequency throttling. We show that CPU power capping at reduced voltage margins results in performance improvement by up to 64% and 24% on average, compared with Intel's RAPL and Dynamic Frequency Scaling (DFS) mechanisms, respectively. Given that CPU operation at reduced voltage margins may potentially limit the effectiveness of a reliability safeguard introduced by manufacturers, we validate the robustness of our approach with a set of long-running experiments. We also show that significant energy gains can be achieved even when taking into account the cost of checkpointing and recovery in large-scale systems.

Furthermore, we investigate the association of workload characteristics with the extent of exploitable reduction of CPU voltage margins. We introduce a run-time governor that dynamically reduces the supply voltage of modern multicore Intel x86-64 CPUs. Our governor employs a model that takes as input a set of performance metrics which are directly measurable via performance monitoring counters and have high predictive value for the minimum tolerable supply voltage, to dynamically predict and apply the appropriate reduction for the workload at hand. Compared to the

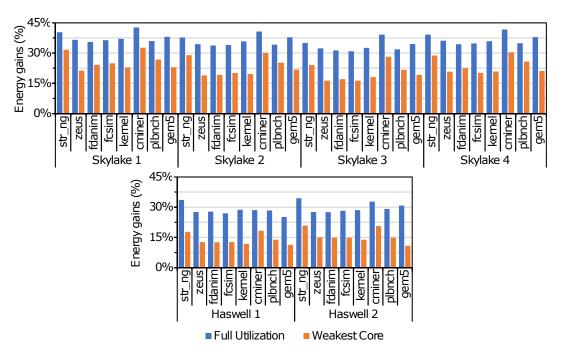

conventional DVFS governor of Intel x86-64 CPUs, our approach achieves significant energy savings, up to 42% and 34%, respectively, for two off-the-shelf processor families.

The quantification and exploitation of CPU voltage margins requires long experimental campaigns, involving multiple systems, multiple configurations and numerous different workloads. Moreover, these experimental campaigns have different targets: characterization of CPU voltage margins, data collection, validation and experimental evaluation of the proposed techniques. Motivated by the complexity of these experimental campaigns, we developed a framework that significantly simplifies the configuration and automates the execution of such experimental campaigns. It supports multiple execution modes, namely OS-controlled and bare-metal execution, it can recover from system crashes due to aggressively reduced voltage margins, and can detect symptoms of erratic workload behavior in the form of Machine Check Exceptions (MCEs), system log entries, or even Silent Data Corruptions (SDCs) if the correct output is supplied as a reference.

Finally, we investigate whether the combination of heterogeneous and approximate computing can yield favorable solutions in the energy efficiency vs. quality of results tradeoff. Approximate computing minimizes the energy footprint of applications at the expense of output quality. More specifically, under the premise that not all parts or execution phases of a program affect the quality of its output equally, developers can introduce approximations in less significant parts of their code in an educated manner, in order to improve the energy efficiency of code execution. We experiment with a set of applications from different domains, with diverse characteristics. We have modified the applications to exploit both heterogeneity and approximations. We evaluate them on heterogeneous platforms (comprising of CPUs and GPUs) and quantify the isolated and combined effect of heterogeneous and approximate computing. Our results show that heterogeneous and approximate computing, independently, result in significant energy gains. Moreover, they can be combined to drastically minimize the energy footprint of executions by up to 94%.

# Περίληψη

#### Παναγιώτης Κουτσοβασίλης

Αξιοποίηση των Εγγενών Περιθωρίων Προστασίας του Υλικού και της Εγγενούς Ετερογένειας του Λογισμικού για τη Βελτίωση της Ενεργειακής Αποδοτικότητας των Υπολογιστικών Συστημάτων

Μία βασική πρόκληση για τη σχεδίαση υπολογιστικών συστημάτων στις μέρες μας, αλλά και στο μέλλον, είναι η αύξηση της επεξεργαστικής ικανότητας εντός αυστηρών περιορισμών κατανάλωσης ισχύος, λόγω παραγόντων που σχετίζονται με το κόστος λειτουργίας και ψύξης, αλλά και τεχνικούς περιορισμούς τροφοδοσίας. Τεχνικές όπως η μείωση των διαστάσεων των τρανζίστορ, η διαχείριση της συχνότητας λειτουργίας των μονάδων επεξεργασίας και ο παραλληλισμός έχουν ήδη αξιοποιηθεί ώστε να διαμορφωθεί το τρέχον επίπεδο αποδοτικότητας ισχύος των υπολογιστικών συστημάτων. Όμως όλες οι προαναφερθείσες πρακτικές δεν μπορούν να προσφέρουν σημαντικές περαιτέρω βελτιώσεις. Μια εναλλακτική προσέγγιση για τη βελτίωση της ενεργειακής αποδοτικότητας τέτοιων συστημάτων είναι η εξειδίκευση σε επίπεδο υλικού. Στις ετερογενείς αρχιτεκτονικές συνυπάρχουν διαφορετικά είδη επεξεργαστικών μονάδων, με διαφορετικά χαρακτηριστικά αποδοτικότητας, καθεμιά κατάλληλη για συγκεκριμένα υπολογιστικά μοτίβα. Ένα τυπικό παράδειγμα είναι η υπολογιστική γενικού σκοπού με χρήση καρτών γραφικών (GPUs) – GPGPU – στα πλαίσια της οποίας αξιοποιούνται κάρτες γραφικών για την εκτέλεση μαζικά παραλληλοποιήσιμων υπολογισμών με συγκεκριμένα χαρακτηριστικά. Ωστόσο, η αξιοποίηση της ετερογένειας προϋποθέτει σημαντική επιπλέον προγραμματιστική προσπάθεια κατά το χρόνο ανάπτυξης του λογισμικού.

Την ίδια στιγμή, οι κατασκευαστές υλικού ενσωματώνουν πλεονασμό σε πολλαπλά επίπεδα κατά τη διάρκεια της σχεδίασης επεξεργαστών, ώστε να εγγυηθούν ορθή εκτέλεση ακόμα και υπό δυσμενείς συνδυασμούς παραμέτρων που οφείλονται, μεταξύ άλλων, στην εγγενή κατασκευαστική ανομοιογένεια των τρανζίστορ και στις συνθήκες λειτουργίας του συστήματος. Ένας τέτοιος μηχανισμός είναι η εφαρμογή επαυξημένης τάσης τροφοδοσίας του επεξεργαστή σε σχέση με αυτή που πραγματικά απαιτείται (περιθώριο τάσης τροφοδοσίας). Ωστόσο, ο συνδυασμός ακραία δυσμενών παραμέτρων λειτουργίας είναι εξαιρετικά σπάνιος ή μπορεί να μην εμφανιστεί ποτέ κατά τη διάρκεια του κύκλου ζωής των επεξεργαστών. Συνακόλουθα, η διαχείριση της τάσης τροφοδοσίας είναι υπερβολικά απαισιόδοξη για τις τυπικές συνθήκες λειτουργίας και οδηγεί σε αχρείαστα υψηλή κατανάλωση ισχύος, λειτουργώντας ως εμπόδιο στην προσπάθεια βελτίωσης της ενεργειακής αποδοτικότητας των συστημάτων.

Στο επίπεδο του λογισμικού, οι προγραμματιστές πολύ συχνά γράφουν κώδικα που επιλύει προβλήματα με σημαντικά υψηλότερη ακρίβεια από αυτή που πράγματι απαιτείται για την κάλυψη των απαιτήσεων ποιότητας της εφαρμογής. Στο ίδιο πλαίσιο, όλα τα τμήματα του κώδικα αντιμετωπίζονται ως εξίσου σημαντικά, παρόλο που η συνεισφορά τους στην ποιότητα του τελικού αποτελέσματος μπορεί να διαφέρει σημαντικά. Κατά συνέπεια τείνουμε να υπερ-υπολογίζουμε και η τάση αυτή επίσης λειτουργεί επιβαρυντικά ως προς την ενεργειακή αποδοτικότητα.

Η ανάγκη για περισσότερο ενεργειακά αποδοτικά συστήματα ενδέχεται να ενθαρρύνει τη μετάβαση από την τεχνολογία CMOS προς μια αποδοτικότερη τεχνολογία σχεδίασης ημιαγωγών. Ωστόσο, μέχρι να εμφανιστεί μια νέα, εμπορικά βιώσιμη υποψήφια τεχνολογία, η βελτιστοποίηση της ενεργειακής αποδοτικότητας των συστημάτων που βασίζονται στην τεχνολογία CMOS αποτελεί σημαντική διέξοδο και αντικείμενο έρευνας. Στην παρούσα διδακτορική διατριβή διερευνώνται τρόποι βελτιστοποίησης της ενεργειακής αποδοτικότητας υπολογιστικών συστημάτων αξιοποιώντας την μείωση των επαυξημένων ορίων λειτουργίας υλικού και την ετερογένεια του υλικού και του λογισμικού. Αναπτύσσουμε μηχανισμούς που μειώνουν την τάση λειτουργίας του επεξεργαστή, και συνακόλουθα το ενεργειακό του αποτύπωμα, αναλόγως των υπολογιστικών χαρακτηριστικών των εκτελούμενων υπολογιστικών έργων. Πέραν της βελτίωσης της ενεργειακής αποδοτικότητας, αυτοί οι μηχανισμοί μπορούν επίσης να χρησιμοποιηθούν για την ελαχιστοποίηση της επίπτωσης στην επίδοση των συστημάτων, όταν αυτά εξαναγκάζονται να λειτουργούν υπό περιορισμούς κατανάλωσης ισχύος. Επίσης, αξιολογούμε τη σχέση μεταξύ της ενεργειακής αποδοτικότητας και της ποιότητας αποτελεσμάτων όταν συνδυάζεται η χρήση ετερογενών συστημάτων με τεχνικές προσεγγιστικού υπολογισμού. Πιο συγκεκριμένα:

Η επιβολή ενός μέγιστου ορίου κατανάλωσης ισχύος των επεξεργαστών (power capping) αποτελεί μια καθιερωμένη τεχνική για τη διαχείριση των περιορισμένων πόρων τροφοδοσίας υπολογιστικών υποδομών. Στη διατριβή μελετάμε τον αντίκτυπο της λελογισμένης μείωσης του επαυξημένου ορίου τάσης τροφοδοσίας των επεξεργαστών στην αποδοτικότητα μηχανισμών power capping που υλοποιούνται σε επίπεδο είτε λογισμικού, είτε υλικού. Πειραματιζόμαστε με πολλαπλές, εμπορικά διαθέσιμες αρχιτεκτονικές επεξεργαστών. Παρατηρούμε ότι η μείωση της πλεονάζουσας τάσης λειτουργίας οδηγεί σε βελτίωση της επίδοσης, της κατανάλωσης ενέργειας σε επίπεδο επεξεργαστή και κόμβου και της θερμοκρασίας του επεξεργαστή. Βασισμένοι στην παραπάνω μελέτη, εισάγουμε έναν νέο μηχανισμό περιορισμού της ισχύος λειτουργίας του επεξεργαστή, που αξιοποιεί την μείωση της πλεονάζουσας τάσης τροφοδοσίας και προσφέρει υψηλότερη επίδοση έως 64% και 24% κατά μέσο όρο, σε σχέση με καθιερωμένους μηχανισμούς όπως το Intel RAPL και η δυναμική κλιμάκωση συχνότητας, αντίστοιχα. Ωστόσο, η λειτουργία του επεξεργαστή με μειωμένα περιθώρια τάσης τροφοδοσίας ενδέχεται δυνητικά να μειώσει την αξιοπιστία λειτουργίας του συστήματος. Για το λόγο αυτό, επικυρώνουμε τον μηχανισμό μας μέσω μιας σειράς μακρόχρονων πειραμάτων. Επιπλέον δείχνουμε πως η λειτουργία του επεξεργαστή με μειωμένα περιθώρια τάσης τροφοδοσίας παραμένει κερδοφόρα, ως προς την ενεργειακή κατανάλωση, ακόμα και σε συστήματα μεγάλης κλίμακας και ακόμη και όταν συνυπολογίσουμε την επιπλέον επιβάρυνση, λόγω της δυνητικά μειωμένης αξιοπιστίας, μηχανισμών για την αντιμετώπιση πιθανών σφαλμάτων, όπως η χρήση checkpointing / αποκατάστασης.

Επιπρόσθετα, μελετάμε τη συσχέτιση των χαρακτηριστικών του υπολογιστικού έργου με το εύρος της αξιοποιήσιμης μείωσης της πλεονάζουσας τάσης τροφοδοσίας του επεξεργαστή. Πιο συγκεκριμένα εισάγουμε μηχανισμό ο οποίος μειώνει δυναμικά την τάση τροφοδοσίας σε επεξεργαστές Intel x86-64. Ο μηχανισμός μας βασίζεται σε μοντέλο το οποίο δέχεται ως είσοδο – κατά το χρόνο εκτέλεσης – ποσοτικές πληροφορίες για την αλληλεπίδραση του λογισμικού που εκτελείται με το υποκείμενο υλικό. Οι πληροφορίες αυτές προέρχονται από τους μετρητές συμβάντων που είναι διαθέσιμοι στους επεξεργαστές Intel και έχουν προγνωστική αξία για την ελάχιστη ανεκτή τάση τροφοδοσίας, η οποία αποτελεί και την έξοδο του μοντέλου. Ο μηχανισμός μας συνεπώς υπολογίζει και επιβάλλει δυναμικά την κατάληλη κάθε στιγμη μείωση τάσης τροφοδοσίας για το υπολογιστικό έργο που εκτελείται. Συγκριτικά με καθιερωμένους μηχανισμούς που διαχειρίζονται τις παραμέτρους λειτουργίας (τάση και συχνότητα) του επεξεργαστή, ο μηχανισμός μας επιτυγχάνει έως 42% και 34% αντίστοιχα μείωση της ενεργειακής κατανάλωσης για δύο εμπορικά διαθέσιμες οικογένειες επεξεργαστών Intel.

Η ποσοτικοποίηση και η αξιοποίηση της μείωσης των περιθωρίων τάσης τροφοδοσίας του επεξεργαστή απαιτεί ευρύ, μακρόχρονο πειραματισμό, με πολλαπλά συστήματα και πολυάριθμες εφαρμογές. Επιπλέον, οι ακολουθίες πειραμάτων ενδέχεται να έχουν διαφορετικούς στόχους: την ποσοτικοποίηση των περιθωρίων τάσης τροφοδοσίας του επεξεργαστή, τη συλλογή δεδομένων (profiling), την επικύρωση και την πειραματική αξιολόγηση των προτεινόμενων μηχανισμών. Ορμώμενοι από την εγγενή πολυπλοκότητα που έχουν τέτοιες πειραματικές καμπάνιες, σχεδιάζουμε και υλοποιούμε υποδομή που απλοποιεί σημαντικά τον ορισμό και αυτοματοποιεί την εκτέλεση τέτοιων ακολουθιών πειραμάτων. Η υποδομή μας υποστηρίζει πολλαπλούς τρόπους εκτέλεσης εφαρμογών, είτε πάνω από λειτουργικό σύστημα, είτε απευθείας πάνω από το υλικό, μπορεί να ανακάμψει από κατάρρευση του συστήματος λόγω επιθετικής μείωσης των περιθωρίων τάσης τροφοδοσίας και μπορεί να ανιχνεύσει συμπτώματα ασταθούς συμπεριφοράς της εκάστοτε εφαρμογής ή του συστήματος ελέγχοντας για λάθη Machine Check Exceptions (MCEs) και Silent Data Corruptions (SDCs), τα τελευταία εφόσον η αναμενόμενη σωστή έξοδος είναι διαθέσιμη.

Τέλος, διερευνούμε κατά πόσο ο συνδυασμός ετερογένειας του υλικού και η προσεγγιστική υπολογιστική μπορεί να αποφέρει επιθυμητές λύσεις ως προς τη σχέση ενεργειακής αποδοτικότητας και μείωσης ποιότητας των αποτελεσμάτων. Η προσεγγιστική υπολογιστική ελαχιστοποιεί το ενεργειακό αποτύπωμα των εφαρμογών σε βάρος της ποιότητας των αποτελεσμάτων. Πιο συγκεκριμένα, δεδομένου ότι όλα τα τμήματα ή οι φάσεις εκτέλεσης μιας εφαρμογής δεν επηρεάζουν εξίσου την ποιότητα των αποτελεσμάτων, οι προγραμματιστές μπορούν να αξιοποιήσουν, με στοχευμένο τρόπο, προσεγγιστικές τεχνικές σε λιγότερο σημαντικά τμήματα του κώδικα τους, προκειμένου να βελτιωθεί η ενεργειακή αποδοτικότητα του εκτελούμενου κώδικα. Πειραματιζόμαστε με ένα σύνολο εφαρμογών με διαφορετικά χαρακτηριστικά, από διαφορετικούς τομείς της επιστήμης και της μηχανικής. Οι εφαρμογές τροποποιήθηκαν ώστε να αξιοποιούν τόσο την ετερογένεια υλικού, όσο και την προσεγγιστική υπολογιστική. Η αξιολόγηση πραγματοποιείται σε ετερογενείς πλατφόρμες (που περιλαμβάνουν επεξεργαστές και κάρτες γραφικών) με στόχο την ποσοτικοποίηση του επιμέρους και του συνδυασμένου οφέλους λόγω της χρήσης ετερογενών συστημάτων και προσεγγιστικής υπολογιστικής. Τα αποτελέσματά μας δείχνουν πως η αξιοποίηση της ετερογένειας του υλικού και του λογισμικού (μέσω προσεγγίσεων) ανεξάρτητα έχει ως αποτέλεσμα τη μείωση της κατανάλωσης ενέργειας. Επιπλέον, μπορούν να συνδυαστούν, ώστε να μειώσουν δραστικά το ενεργειακό αποτύπωμα της εκτέλεσης λογισμικού έως και κατά 94%.

## Acknowledgements

This dissertation is the result of research work conducted while I was pursuing my PhD degree in the Department of Electrical and Computing Engineering of University of Thessaly in Greece.

First and foremost, I would like to thank my mentors, Professors Christos D. Antonopoulos, Nikolaos Bellas, and Spyros Lalis from the University of Thessaly. They have been exceptionally good at guiding me during my initial steps, throughout my MSc and PhD. Without their guidance and mentoring none of this work would be possible. They were always available to discuss and provide constructive criticism.

I would also like to thank my family. Especially, I owe to my father, Spyros, for teaching me to always pursue my dreams and my mother, Helen, for her unconditional love and support all along my academic pursuits. Also, my friends will always have a special place in my heart because they were always there during good times, and bad times to support me with patience and love.

Furthermore, special thanks to my friends and colleagues Kalogirou Christos and Maroudas Manolis with whom I shared, pretty much all of my research career thus far. Our joined research efforts and stimulating discussions were very educating.

Last but not least, I acknowledge the funding agencies which made this research possible with their financial support. These include the European Commission through the UniServer H2020 and SCoRPiO FP7 projects, and the European Social Fund and Greek national resources through the Centaurus project (Aristeia II action).

# Contents

| Al | ostrac | t       |                                                       | iii |

|----|--------|---------|-------------------------------------------------------|-----|

| П  | ερίλη  | ψη      |                                                       | vi  |

| Ac | knov   | ledgem  | ents                                                  | x   |

| 1  | Intr   | oductio | n                                                     | 1   |

|    | 1.1    | Proble  | m                                                     | 1   |

|    | 1.2    | Motiva  | n <mark>tion</mark>                                   | 3   |

|    | 1.3    | Contrib | outions                                               | 5   |

|    |        | 1.3.1   | CPU operation at reduced voltage margins              | 5   |

|    |        | 1.3.2   | Combining approximate & heterogeneous computing       | 7   |

|    | 1.4    | Outline | 2                                                     | 8   |

| 2  | Bac    | kground | l                                                     | 10  |

|    | 2.1    | Platfor | ms Overview                                           | 10  |

|    |        | 2.1.1   | Intel-Based systems                                   | 10  |

|    |        |         | Frequency adjustment                                  | 10  |

|    |        |         | Supply voltage adjustment                             | 11  |

|    |        |         | Power and performance monitoring mechanisms           | 12  |

|    |        | 2.1.2   | ARM-based platforms                                   | 13  |

|    |        |         | Frequency adjustment                                  | 13  |

|    |        |         | Supply voltage adjustment                             | 14  |

|    |        |         | Power and performance monitoring mechanisms           | 14  |

|    | 2.2    | Centau  | rus Runtime & Programming Model                       | 15  |

|    |        | 2.2.1   | Platform model                                        | 15  |

|    |        | 2.2.2   | Execution Model                                       | 15  |

|    |        | 2.2.3   | Directives                                            | 16  |

| 3  | The    | Impact  | of CPU Voltage Margins on Power-Constrained Execution | 19  |

|    | 3.1    | Charac  | terization of Voltage Margins                         | 20  |

|    | 3.2    | Power   | Capping Approaches                                    | 22  |

|    |        | 3.2.1   | Existing techniques                                   | 22  |

|   |      | 3.2.2 RAPL-RM                                                   | 23 |

|---|------|-----------------------------------------------------------------|----|

|   |      | 3.2.3 RVSCap                                                    | 23 |

|   | 3.3  | Experimental Study                                              | 25 |

|   |      | 3.3.1 Benchmarks                                                | 25 |

|   |      | 3.3.2 Effects of CPU voltage margins on power capping           | 27 |

|   |      | 3.3.3 Combining RVSCap with hybrid power capping mechanisms     | 34 |

|   | 3.4  | Platforms Comparison                                            | 36 |

|   | 3.5  | Power Modeling to Mitigate Hardware Limitations                 | 39 |

|   | 3.6  | Related Work                                                    | 41 |

| 4 | Dyn  | amic Reduction of Workload-Dependant CPU Voltage Margins        | 44 |

|   | 4.1  | Offline Quantification of Voltage Margins                       | 45 |

|   | 4.2  | Voltage Margins Modeling and Estimation                         | 49 |

|   |      | 4.2.1 Profiling                                                 | 50 |

|   |      | 4.2.2 Model type                                                | 51 |

|   |      | 4.2.3 Model training                                            | 52 |

|   | 4.3  | Extended Dynamic Voltage Scaling                                | 55 |

|   | 4.4  | Experimental Evaluation                                         | 57 |

|   | 4.5  | Related work                                                    | 62 |

| 5 | Syst | em Reliability when Operating at Reduced Voltage Margins        | 65 |

|   | 5.1  | The Tradeoff of Operating CPUs at Reduced Voltage Margins       | 66 |

|   |      | 5.1.1 Validation of Reduced Voltage Scaling power Capping (RVS- |    |

|   |      | Cap) and Extended Dynamic Voltage Scaling (xDVS)                | 66 |

|   |      | 5.1.2 Effect of Operation at Reduced Voltage Margins on MTBF.   | 66 |

|   |      | 5.1.3 Effects of Operation at Reduced Voltage Margins in Large, |    |

|   |      | Scale-out Deployments                                           | 67 |

|   | 5.2  | Hardware Mechanisms                                             | 69 |

| 6 | A Fı | ramework for Large-Scale Experimentation at Reduced CPU Voltage |    |

|   | Mar  | gins                                                            | 71 |

|   | 6.1  | Framework Objectives                                            | 72 |

|   | 6.2  | $(XM)^2$ for OS-controlled Execution                            | 72 |

|   |      | 6.2.1 Client configuration                                      | 73 |

|   |      | 6.2.2 Applications configuration                                | 75 |

|   |      | 6.2.3 Database                                                  | 79 |

|   | 6.3  | Node Resetting Controller                                       | 79 |

|   | 6.4  | Related Work                                                    | 80 |

| 7  | The            | Individ  | lual and Combined Energy Efficiency Effects of Approxima | ate   |

|----|----------------|----------|----------------------------------------------------------|-------|

|    | <b>&amp;</b> H | leteroge | eneous Computing                                         | 82    |

|    | 7.1            | Platfo   | rm Assumptions                                           | . 83  |

|    |                | 7.1.1    | Hardware assumptions                                     | . 83  |

|    |                | 7.1.2    | Software assumptions                                     | . 83  |

|    | 7.2            | Applic   | cations                                                  | . 84  |

|    |                | 7.2.1    | LULESH                                                   | . 85  |

|    |                | 7.2.2    | Molecular Dynamics                                       | . 86  |

|    |                | 7.2.3    | Monte Carlo PDE solver                                   | . 87  |

|    |                | 7.2.4    | K-Means                                                  | . 87  |

|    |                | 7.2.5    | Fisheye                                                  | . 88  |

|    |                | 7.2.6    | DCT MV                                                   | . 89  |

|    |                | 7.2.7    | SPS-Stereo                                               | . 89  |

|    | 7.3            | Evalua   | ation                                                    | . 90  |

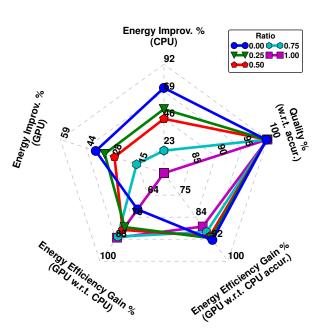

|    |                | 7.3.1    | LULESH                                                   | . 91  |

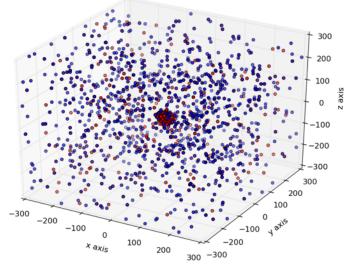

|    |                | 7.3.2    | Molecular Dynamics                                       | . 92  |

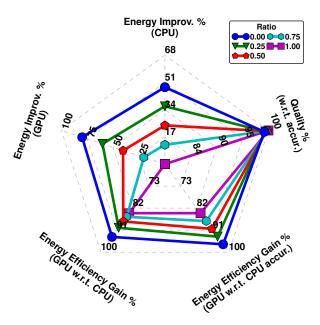

|    |                | 7.3.3    | Monte Carlo PDE solver                                   | . 93  |

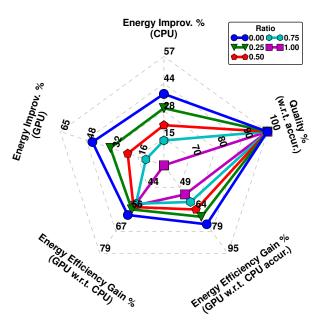

|    |                | 7.3.4    | K-Means                                                  | . 94  |

|    |                | 7.3.5    | Fisheye                                                  | . 95  |

|    |                | 7.3.6    | DCT MV                                                   | . 96  |

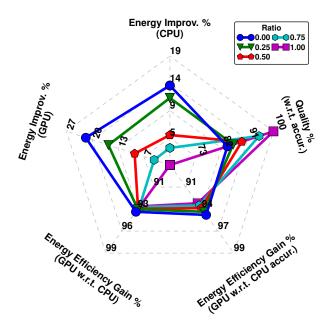

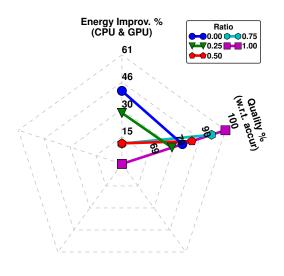

|    |                | 7.3.7    | SPS-Stereo                                               | . 98  |

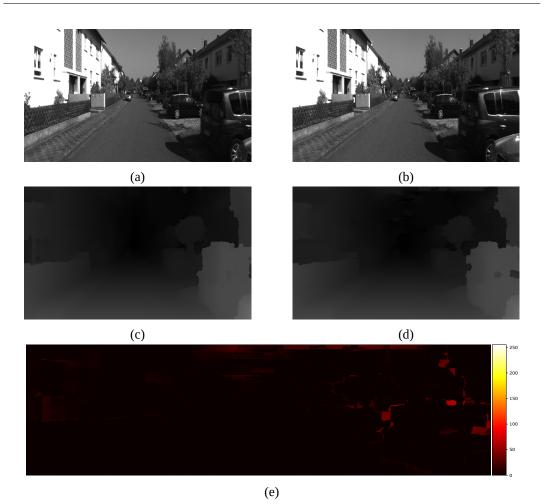

|    | 7.4            | Relate   | d Work                                                   | . 99  |

| 8  | Con            | cluding  | ; Remarks                                                | 101   |

|    | 8.1            | Summ     | ary                                                      | . 101 |

|    | 8.2            | Conclu   | usions                                                   | . 102 |

|    | 8.3            | Future   | Work                                                     | . 104 |

| A  | Rela           | ated Pul | blications                                               | 105   |

| В  | Con            | tributio | on to Joint Publications                                 | 107   |

| Bi | bliog          | raphy    |                                                          | 110   |

# **List of Figures**

| 1.1 | Impact of reducing CPU voltage margins on performance when the         |    |

|-----|------------------------------------------------------------------------|----|

|     | CPU operates at a power cap                                            | 3  |

| 1.2 | Accurate (left) vs Approximate (right) output of a disparity map depth |    |

|     | estimation application.                                                | 5  |

| 2.1 | Speedshift overview.                                                   | 11 |

| 2.2 | Overview of Intel FIVR                                                 | 11 |

| 2.3 | CPPC API overview.                                                     | 13 |

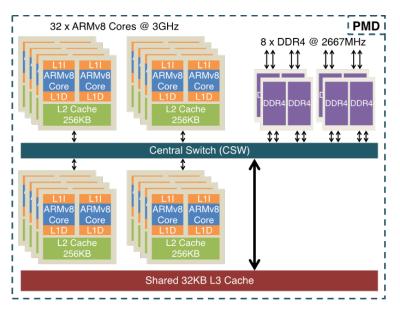

| 2.4 | Overview of PMD domain of X-Gene processors                            | 14 |

| 2.5 | OpenCL Platform Model [14]                                             | 15 |

| 2.6 | Task life in the Centaurus framework.                                  | 16 |

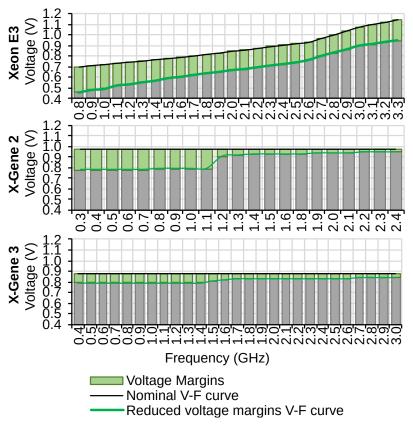

| 3.1 | Voltage (y-axis) vs. frequency (x-axis) for each CPU                   | 22 |

| 3.2 | Flowchart of RVSCap. Only a few components (in blue) are different     |    |

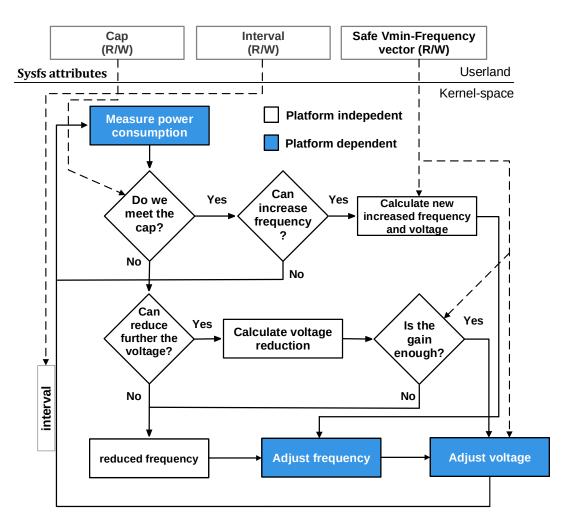

|     | and need to be developed for each target platform                      | 24 |

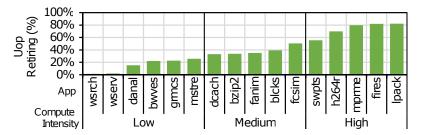

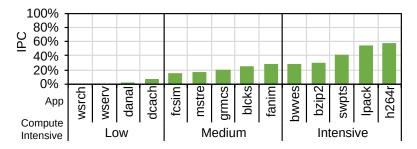

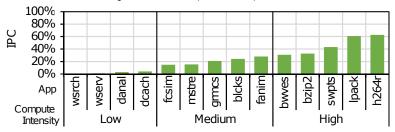

| 3.3 | Uops retiring(%) normalized wrt. CPU max performance (Table 2.1)       |    |

|     | on Xeon E3                                                             | 27 |

| 3.4 | Retired instructions per cycle (IPC)(%) normalized wrt. CPU max        |    |

|     | performance (Table 2.1) on X-Gene 2                                    | 27 |

| 3.5 | Retired instructions per cycle (IPC)(%) normalized wrt. CPU max        |    |

|     | performance (Table 2.1) on X-Gene 3                                    | 27 |

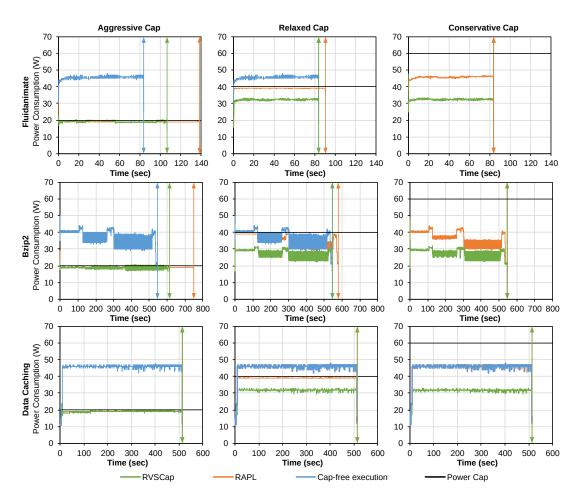

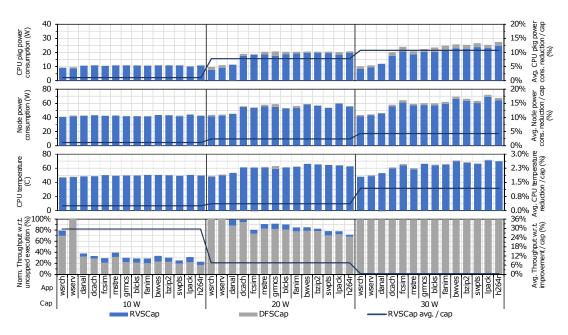

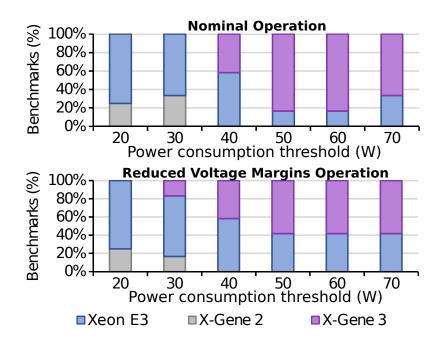

| 3.6 | Power consumption on Skylake for different applications, power caps    |    |

|     | and power capping methodologies.                                       | 28 |

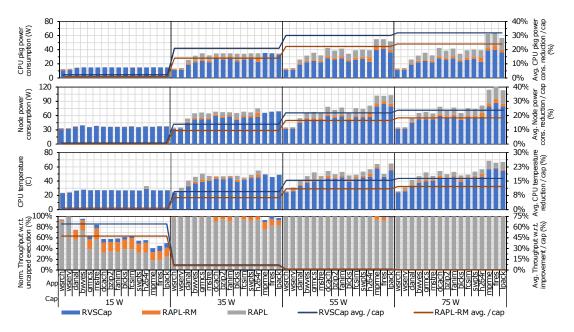

| 3.7 | CPU and total node power dissipation, CPU temperature and perfor-      |    |

|     | mance for different power caps and power capping mechanisms on         |    |

|     | Xeon E3                                                                | 29 |

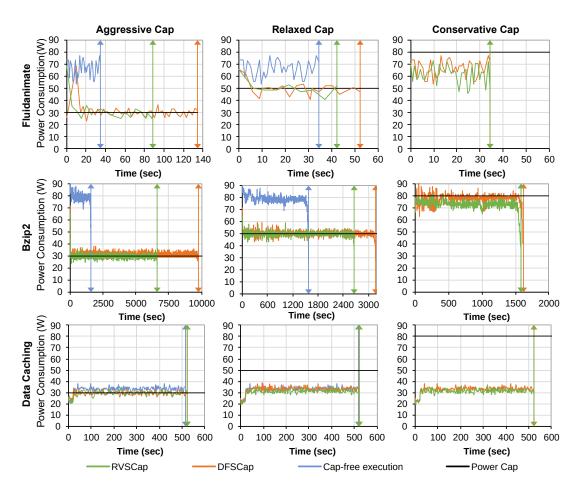

| 3.8 | Power consumption on X-Gene 3 for different applications, power        |    |

|     | caps and power capping methodologies.                                  | 31 |

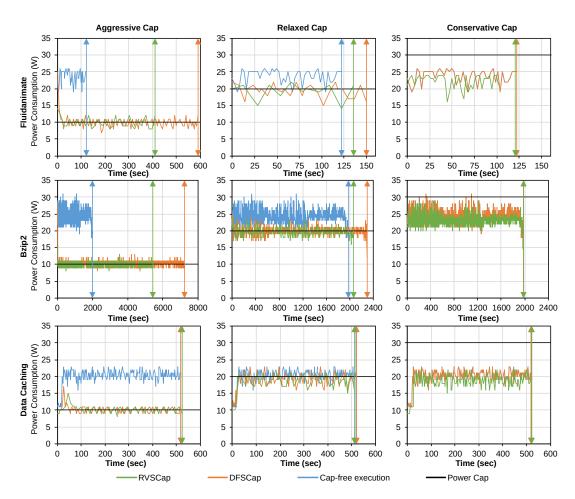

| 3.9 | Power consumption on X-Gene 2 for different applications, power        |    |

|     | caps and power capping methodologies.                                  | 32 |

| 3.10 | CPU and total node power dissipation, CPU temperature and perfor-                |    |

|------|----------------------------------------------------------------------------------|----|

|      | mance for different power caps and power capping mechanisms on                   |    |

|      | X-Gene 2                                                                         | 33 |

| 3.11 | CPU and total node power dissipation, CPU temperature and perfor-                |    |

|      | mance for different power caps and power capping mechanisms on                   |    |

|      | X-Gene 3                                                                         | 33 |

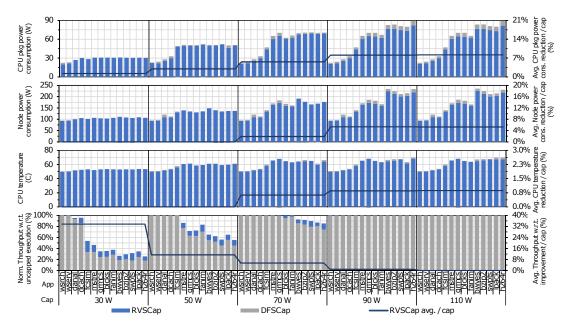

| 3.12 | Normalized performance (wrt. to uncapped execution) and node power               |    |

|      | consumption on Xeon E3 and X-Gene processors                                     | 35 |

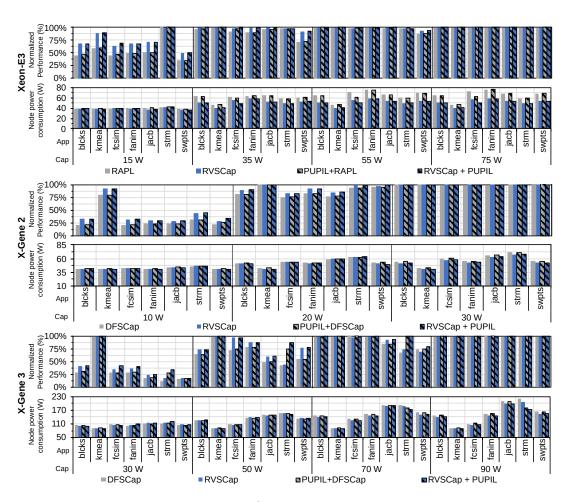

| 3.13 | Percentage of experiments (benchmarks) for which each processor                  |    |

|      | achieved the highest throughput at a given power cap                             | 37 |

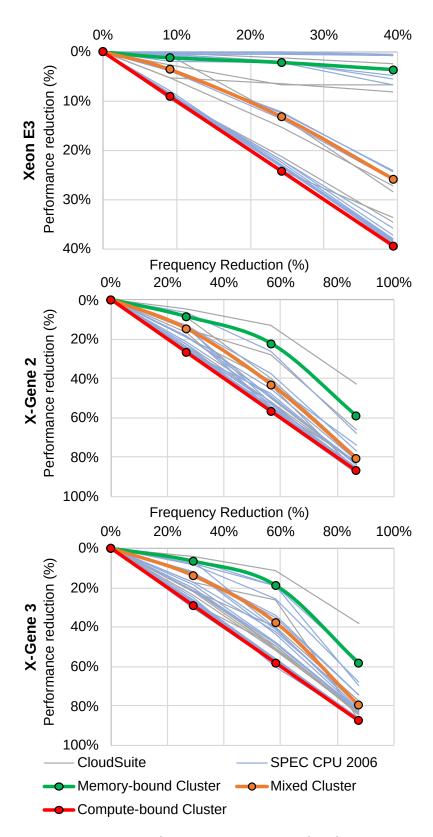

| 3.14 | Classes of applications, in terms of performance sensitivity to fre-             |    |

|      | quency reduction.                                                                | 38 |

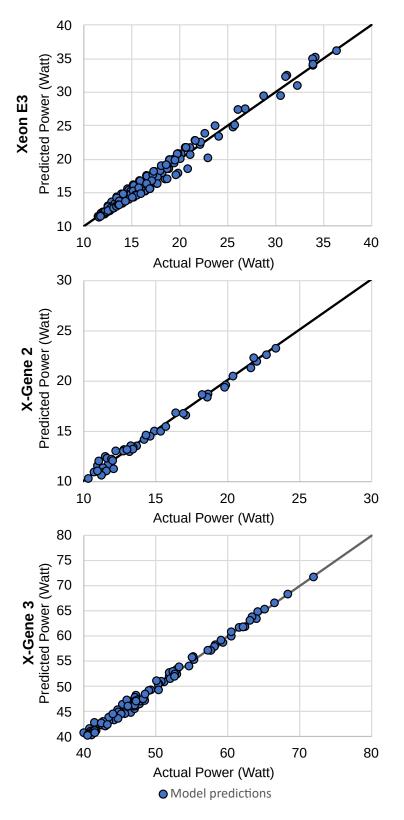

| 3.15 | Predictions of our power estimation models for Xeon E3, and X-Gene               |    |

|      | processors.                                                                      | 40 |

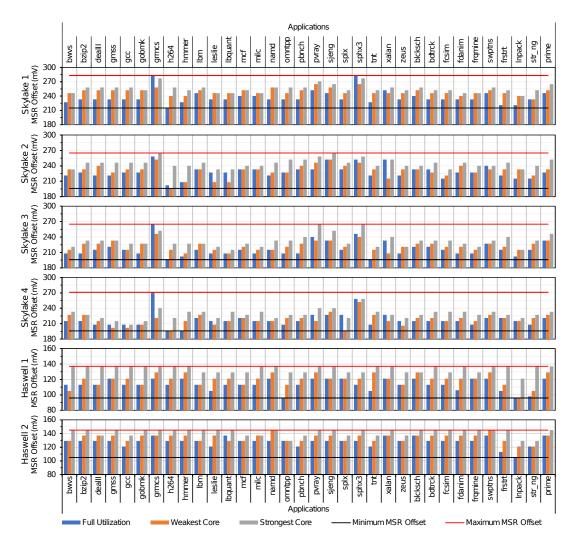

| 4.1  | Evaluation of MSR <sub>offset</sub> settings for 34 benchmarks (10 runs each) in |    |

|      | each workstation.                                                                | 46 |

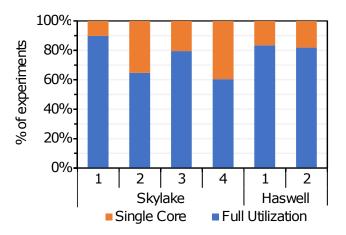

| 4.2  | Percentage of experiments for which single core, or multi-instance/              |    |

|      | threaded workloads resulted to narrower voltage margins                          | 47 |

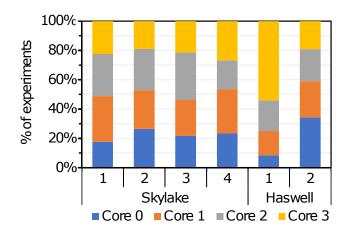

| 4.3  | Percentage of experiments in which any given core resulted being the             |    |

|      | weakest during our characterization phase                                        | 48 |

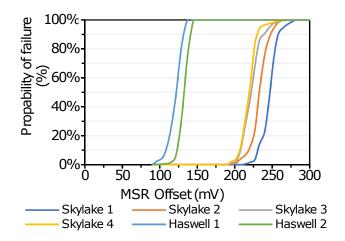

| 4.4  | Average (across all configurations) failure probability CDF for each             |    |

|      | CPU, with respect to the applied MSR <sub>offset</sub>                           | 48 |

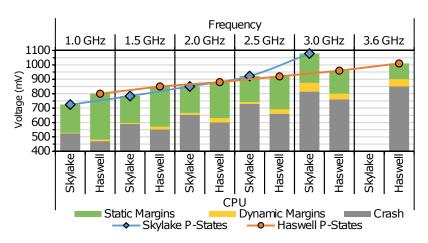

| 4.5  | Voltage margins for a range of CPU operating frequencies for Skylake             |    |

|      | 2 and Haswell 2                                                                  | 49 |

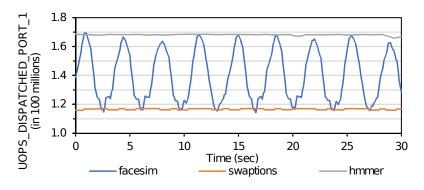

| 4.6  | The number of dispatched uops in port 1 during the execution time                |    |

|      | of an application.                                                               | 53 |

| 4.7  | Prediction of our model with and without the safety margin, for sam-             |    |

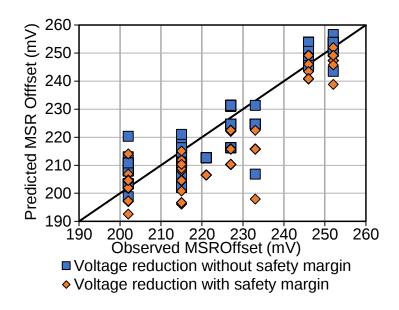

|      | ples in the validation data set                                                  | 54 |

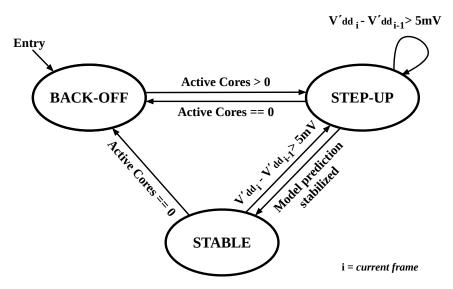

| 4.8  | FSM diagram of the xDVS governor                                                 | 55 |

| 4.9  | MSR <sub>offset</sub> applied by xDVS on Skylake 2, for sudden transitions be-   |    |

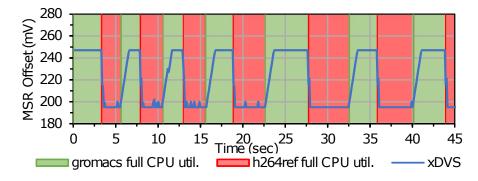

|      | tween workloads with different margins                                           | 57 |

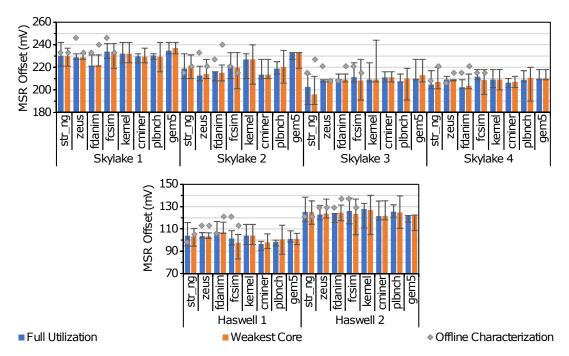

| 4.10 | The bars show the average dynamic MSR <sub>offset</sub> applied by xDVS, for     |    |

|      | Skylake (up) and Haswell (down) workstations                                     | 58 |

| 4.11 | Timeline showing the MSR <sub>offset</sub> for consecutive single core execu-    |    |

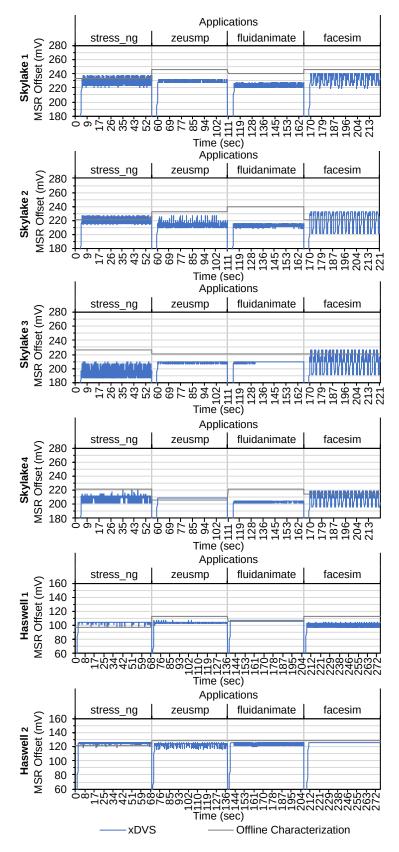

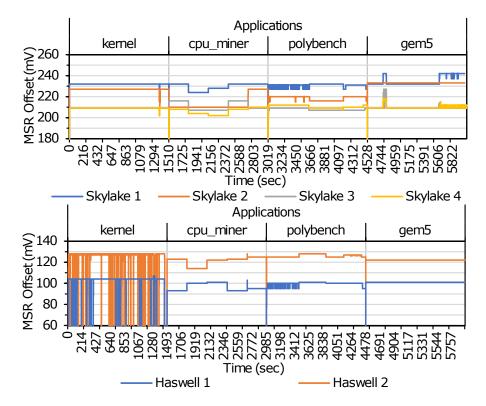

|      | tions of four applications on all target parts (CPU chips).                      | 59 |

| 4.12 | The timeline showing the MSR <sub>offset</sub> applied by xDVS, while execut-<br>ing the large applications in full system utilization for Skylake (up) |    |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | and Haswell (down) workstations.                                                                                                                        | 60 |

| 4.13 | Energy gains of xDVS when compared with Intel P-state governor                                                                                          |    |

|      | for Skylake (up) and Haswell (down) CPUs                                                                                                                | 61 |

| 5.1  | Energy reduction of RVSCap with checkpointing vs. execution at                                                                                          |    |

|      | nominal settings without checkpointing, for $MTBF_{0.9}$ , $MTBF_{0.6}$                                                                                 |    |

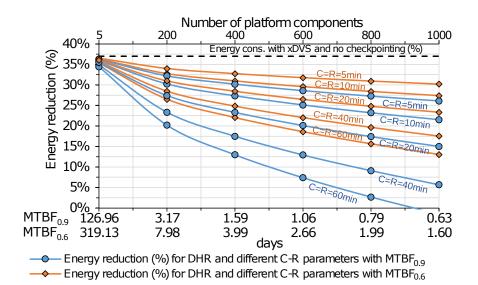

|      | and different $C$ - $R$ parameters                                                                                                                      | 68 |

| 5.2  | Energy reduction of xDVS with checkpointing vs. execution at nomi-                                                                                      |    |

|      | nal settings without checkpointing, for $MTBF_{0.9}$ , $MTBF_{0.6}$ and dif-                                                                            |    |

|      | ferent $C$ - $R$ parameters                                                                                                                             | 69 |

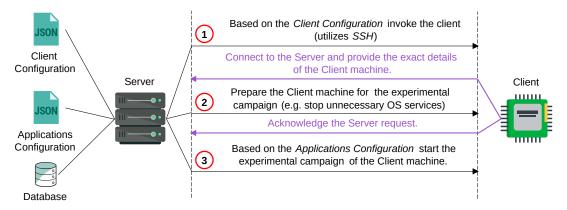

| 6.1  | $(\mathbf{X}\mathbf{M})^2$ for OS-Controller execution overview.                                                                                        | 72 |

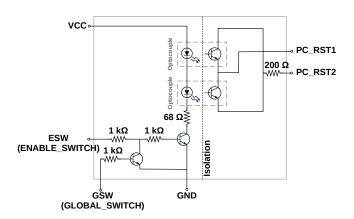

| 6.2  | Complementary circuit for resetting the target platform                                                                                                 | 80 |

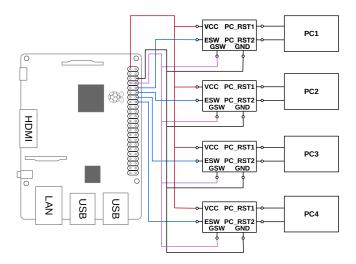

| 6.3  | Controlling the state of multiple platforms with a Raspberry Pi SoC.                                                                                    | 80 |

| 7.1  | LULESH evaluation                                                                                                                                       | 92 |

| 7.2  | MD evaluation                                                                                                                                           | 93 |

| 7.3  | Positions of particles for a fully approximate (red) and accurate (blue)                                                                                |    |

|      | execution).                                                                                                                                             | 93 |

| 7.4  | Monte Carlo PDE solver evaluation                                                                                                                       | 94 |

| 7.5  | K-Means evaluation                                                                                                                                      | 95 |

| 7.6  | Fisheye evaluation                                                                                                                                      | 96 |

| 7.7  | DCT MV evaluation                                                                                                                                       | 97 |

| 7.8  | (a) DCT MV fully accurate output, (b) DCT MV fully approximate                                                                                          |    |

|      | output                                                                                                                                                  | 97 |

| 7.9  | SPS-Stereo evaluation                                                                                                                                   | 98 |

| 7.10 | (a) (b) Respectively, left and right images of the captured scene (c)                                                                                   |    |

|      | SPS-Stereo fully accurate output, (d) SPS-Stereo fully approximate                                                                                      |    |

|      | output, (e) Heatmap of pixel intensity differences of fully accurate vs                                                                                 |    |

|      | fully approximate output.                                                                                                                               | 99 |

# **List of Tables**

| 2.1 | Characteristics of the four target CPUs                                                         | 10 |

|-----|-------------------------------------------------------------------------------------------------|----|

| 3.1 | Benchmark set.                                                                                  | 26 |

| 3.2 | Average gains of RVSCap, compared with RAPL and DFSCap for                                      |    |

|     | Xeon and X-Gene processors respectively, under aggressive and re-                               |    |

|     | laxed power caps, for the different compute-intensity groups of the                             |    |

|     | benchmarks                                                                                      | 34 |

| 4.1 | Most influential performance metrics for $V_{min}$ , as ranked by the MI                        |    |

|     | algorithm.                                                                                      | 52 |

| 6.1 | $(\mathbf{X}\mathbf{M})^2$ configuration differences to perform a <i>characterization</i> or an |    |

|     | <i>evaluation</i> experimental campaign                                                         | 79 |

| 7.1 | List of target applications and their characteristics.                                          | 84 |

Dedicated to my family and friends

## Chapter 1

# Introduction

The Internet is on the verge of a turning point due to the ever-increasing Internetconnected intelligent devices that in the upcoming decade will be in the orders of tens of billions forming the Internet of Things (IoT). Each intelligent device is pushing a little data to the Internet, and a little data pushed by billions of smart devices in Homes, Cities, and Environments will be aggregated to become Big Data, stored and processed currently in huge central datacenters. These large data sets are becoming a core asset in the economy, fostering new industries, processes, and products and creating significant competitive advantages [1]. Turning this opportunity into products and employment growth critically depends on overcoming a formidable obstacle: harnessing efficiently the imminent data flood in the Future Internet. This is contingent on improving the performance of servers that run internet/cloud-based services while reducing their power consumption. This is very important for reducing the running costs in a server farm that supports today's datacenters and cloud providers, while at the same time it enables the placement of servers co-located with the origin of the data (e.g. sensors) where power is limited [2].

As a consequence, current and next-generation devices and systems must evolve to (a) operate on completely new principles, and (b) support completely new architectures.

## 1.1 Problem

Modern datacenters and high-performance computing (HPC) systems are expected to operate under a tight power budget due to cost, power delivery, and cooling limitations. This is a challenging undertaking, as in the past decade power and cooling costs have doubled [3]. In particular, CPUs account for up to 60% of the total power consumption of compute nodes [4], whereas datacenter cooling has a power footprint equal to that of the compute infrastructure. An important exercise for both the datacenter and HPC domains is to design and deploy techniques that optimize throughput/performance in a power-constrained environment. However, aggressive CMOS technology scaling into lower nanometer geometries has led to the variability of transistor characteristics. Traditionally, techniques for dealing with transistor variability involve extra provisioning in logic and memory circuits, in the form of increased voltage margins, reduced operating frequencies and error correction circuitry. Such voltage margins are specified at design time by taking into account the implementation technology, power budget, worst case timing paths, operating conditions, and fabrication process variations.

These voltage margins lead to significant power overheads, which conflicts with the challenges of limiting power dissipation. The average power overhead of CPU voltage margins can be in the order of 35% [5], yet most of the time these margins are excessive and translate to unnecessary power overhead, as the worst-case combinations of adverse conditions that were considered at design time may appear only rarely or even not at all during the life cycle of a given processor. Providing an end-to-end approach that effectively reduces these margins, could have a significant impact on such systems, as the resulting energy gains would enable the utilization of extra resources to support additional parallelism and increased computational capacity. A critical challenge though is to reduce the margins as much as possible, yet without compromising the reliability of the system.

Another hardware/software approach to improve performance per Watt, that does not affect the reliability of the system but requires extra programmer effort, is heterogeneous computing. Heterogeneous computing exploits accelerators which are optimized for efficiently executing certain computational patterns. GPUs are a popular family of accelerators which, in contrast to conventional CPU-like architectures, offer massive, partially asynchronous parallel execution through many computational cores. Although their power footprint is slightly higher than that of a typical CPU, they are superior in terms of performance per Watt. At the expense of a few extra Watts, applications that exhibit sufficient parallelism and GPU-friendly computation and memory access patterns can utilize GPUs to reduce execution time and by extension their energy footprint.

A more aggressive software approach towards improving the energy efficiency of applications, which, similarly to heterogeneous computing requires extra programmer effort, is approximate computing. Computing systems are traditionally engineered and expected to execute programs under the assumption that all computations have the same significance (importance) for the quality of program output. Approximate computing disrupts this rather conservative approach, by relaxing the requirement for fully accurate output, thus enabling a new trade-off among performance, energy footprint and quality of results.

The combination of heterogeneous and approximate computing opens up new

possibilities for power/energy management, energy footprint minimization of applications and hardware classification in terms of energy efficiency. Software can be extended by approximate computing techniques to enable applications that operate under tight energy budgets. Hardware accelerators can be designed to natively support different approximations when instructed to. Large scale datacenters and HPC infrastructure deployments could significantly cut down their power costs, adapt to more stringent power caps and set new standards to metrics such as performance per Watt.

## **1.2 Motivation**

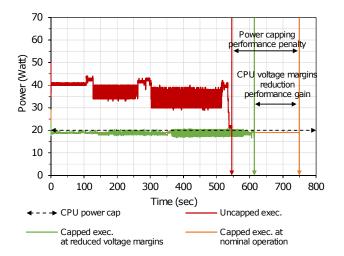

Figure 1.1 depicts the power consumption of *bzip2* from the SPEC CPU2006 benchmark suite [6] for three different execution scenarios: one without a CPU power cap (*dark red* line) and two at a CPU power cap of 20W at nominal (*orange* line) and at reduced CPU voltage margins (*green* line). The experiments have been performed on a Xeon E3-based node which has a Thermal Design Power (TDP) of 80W, and, thus, the 20W power cap is rather restrictive. We concurrently run multiple instances of *bzip2* to fully engage all four cores of the CPU. The horizontal distance between the ending points of the *dark red* and *orange* vertical lines indicate the performance penalty due to CPU power capping. Similarly, the horizontal distance between the ending points of the *orange* and *green* vertical lines represent the performance gains of CPU voltage margins reduction, compared with nominal CPU operation for the same cap.

In the power-constrained execution with nominal CPU operation, the clock frequency is reduced significantly to meet the cap, leading to a 36% drop in performance.

Figure 1.1: Impact of reducing CPU voltage margins on performance when the CPU operates at a power cap.

On the other hand, with CPU operation at reduced voltage margins, the 20W power cap is met without underscaling the frequency as much, and hence, with substantially lower performance degradation. More specifically, for the power-constrained execution at nominal voltage, the CPU frequency is 1.9 GHz on average and for the execution at reduced voltage margins (-170 mV reduction) the average CPU frequency is 2.5 GHz. As a result, we observe 22% improved performance at reduced voltage margins compared with capped execution at nominal voltage. These results demonstrate the opportunity of harnessing voltage margins to meet restrictive power caps without resorting to extreme frequency downscaling.

Furthermore, for certain processor families, CPU voltage margins depend on the computation characteristics of the executing workload. More specifically, the reduction of voltage margins, that does not compromise the system reliability, varies for workloads that exhibit different resource utilization patterns. For example, for the Xeon E3 system of the previous example, we observe that the safe reduction of CPU voltage margins is -192mV and -270mV for h264ref and gromacs applications, respectively, from the SPECCPU 2006 [7] benchmark suite. This divergence demonstrates the opportunity of increasing the energy savings, due to operation at reduced voltage margins, for several applications.

However, as already mentioned CPU operation at reduced voltage margins may affect the system reliability. An approach that does not affect the reliability of the system and offers significant energy savings is the combination of heterogeneous with approximate computing. Approximate computing disrupts the traditional and rather conservative computing approach, by relaxing the requirement for fully accurate output, thus enabling a new trade-off among performance, energy footprint and quality of results. Approximate computing builds upon two observations: (a) several application domains, such as simulations, computer vision, media applications, etc. can tolerate a certain degree of results imprecision, and (b) result quality is not equally affected by all computations of a program; some computations can be approximated or even dropped without heavily penalizing output quality.

As an example, Figure 1.2 presents the output of an application that estimates a dense disparity map of a scene. As shown in the Figure, there are minor differences between the results of the accurate and the approximate versions of the application, because the approximation used lowers the resolution of the sub-regions scanning in the scene. However, the main outputs of the application, namely object positioning, and disparity estimations are still correct. Moreover, with this approximation and by executing the application entirely on a GPU we can achieve sufficient quality of output with 37% improvement in energy consumption, compared with accurate execution of the application on a CPU.

Figure 1.2: Accurate (left) vs Approximate (right) output of a disparity map depth estimation application.

## 1.3 Contributions

#### **1.3.1** CPU operation at reduced voltage margins

We study the reduction of CPU voltage margins, based on the premise that the worstcase combinations, which were considered at design time and translate to higher CPU operating voltage in the form of voltage guardbands, may appear only rarely or even not at all during the lifecycle of a given processor. On the other hand, the reduction of CPU voltage margins may compromise the reliability of the system. This mandates an extensive experimental and theoretical study that ultimately answers the following questions: "How to exploit the voltage margins reduction ?", "Is the system reliability affected ?", and "How to automate the complex experimentation process ?".

#### How to exploit the voltage margins reduction?

A critical step in the exploitation of voltage margins is to identify how they can be reduced without compromising, at least observably, system reliability. More specifically, we need to identify how different CPU utilization scenarios affect the amount by which the CPU operating voltage can be reduced. As an example, we need to observe the difference in voltage margins when a workload utilizes all the cores versus a single core of the CPU, as well as, how applications with different computational characteristics affect the CPU operation at reduced voltage margins.

In the context of this dissertation, we investigate all of the aforementioned aspects and present the results for four different commercially available, off-the-shelf, processors. We find that there is a significant amount of divergence in the width of the CPU voltage margins, depending on the microarchitecture of the processor, and there is a substantial differentiation, even for processors of the same architecture.

Based on our findings, which we will present in detail in the following Chapters, we observe that for certain processors, that exhibit wide voltage margins, there is workload dependability of the extent of CPU operating voltage reduction that can be applied without leading to erroneous execution. However, there are processors, with significantly lower voltage margins, for which the aforementioned effect is almost negligible and completely diminishes when the workload utilizes all the CPU cores. In other words, there is a static portion of CPU voltage margins that can be exploited, but in certain architectures, there is also another dynamic (workload-dependant) portion that can be exploited and leads to greater energy savings. To this end, we present two approaches in the following Sections that exploit appropriately both static and dynamic voltage margins for the corresponding CPUs. More specifically,

- We study the effects of reducing the width of the static CPU voltage margins under power-constrained execution. To the best of our knowledge, this is the first work that studies the interplay between CPU power capping and operation at reduced margins, using multiple evaluation metrics and experimenting across multiple platforms. Also, we experimentally, on real systems, demonstrate that conventional CPU power capping mechanisms can be combined with operation at reduced voltage margins.

- We exploit the workload-dependability of CPU voltage margins by designing an online voltage scaling governor that dynamically adjusts the supply voltage based on a model predicting the extent of exploitable voltage margins. The model is trained using data collected during characterization and profiling experimental campaigns.

#### Is system reliability affected?

Although, the aforementioned approaches reduce the CPU voltage margins in an educated manner that does not lead to observable erratic behavior, given that the CPU operates outside its nominal, manufacturer-defined operating envelope, the possibility of the CPU accidentally entering an operating region where errors may occur can not be eliminated. Both in current and future large-scale systems reliability is and will remain an inherent, first-class design concern, leading to the implementation and use of fault tolerance mechanisms (such as checkpointing and restart), even for systems operating within their nominal configuration envelope. In order to validate the robustness of our mechanisms for reducing voltage margins, we orchestrate a largescale validation campaign on 16 systems, which lasted for 23 days. Based on our results, we provide a pessimistic estimation of the new Mean Time Between Failures (MTBF) when the CPU operates at reduced voltage margins and we show that, even when combined with a fault-tolerance mechanism such as checkpointing, the energy gains of voltage margins reduction remain attractive.

#### How to automate the complex experimentation process?

A necessary undertaking for exploiting CPU voltage margins is quantifying the width of the respective margins. Moreover, mechanisms that operate the systems outside their nominal configuration envelope mandate long, complex validation and evaluation campaigns. As a consequence, there is a need for a framework that supports multiple platforms of different architectures, supports different software stacks – namely OS-controlled and bare-metal execution – can reliably extract the voltage margins of a CPU, and evaluate the performance and robustness of the aforementioned mechanisms. Also, this framework must identify symptoms of errors due to operation at reduced voltage margins, such as Machine Check Exception errors, and Silent Data Corruptions. At the same time, it needs to be resilient to external problems, such as power outages or network failures. We introduce eXtended Margins eXperiment Manager  $((XM)^2)$  which automates the evaluation of software on systems operating outside their nominal configuration envelope. Although  $(XM)^2$  supports both baremetal and OS-controlled execution, we will focus on the OS-controlled flavor.

#### **1.3.2** Combining approximate & heterogeneous computing

We study the combination of heterogeneous with approximate computing, based on the premise that specific phases of computation may incur a high performance and energy toll without a significant contribution to the quality of the result. We focus on applications for which the algorithmic logic of at least some of their phases can be efficiently executed on accelerators such as GPUs. Our study ultimately provides answers to the following questions: "Can approximate and heterogeneous computing be combined ?", and "What is the effect in the energy efficiency vs. quality of results tradeoff ?".

#### Can approximate and heterogeneous computing be combined?

There are several applications for which the combination of approximate and heterogeneous computing can yield significant energy consumption savings without significant / non-tolerable effect to the quality of results. For example, applications that simulate systems of bodies, ranging from atoms to stars and galaxies, are a perfect match to apply the combination of heterogeneous with approximate computing. The governing law of such a system is the equation of motion for particles and, thus, the computational phase can be parallelized at the granularity of a particle, enabling the exploitation of a GPU. Moreover, due to the nature of the simulation, not all particles affect with the same significance the motion of other particles. More specifically, particles that are further away, from the particle of interest, have negligible impact on its motion. As a result, an approximation that would result in saving computational resources with minimal impact to the quality of results is setting a cut-off distance beyond which the interaction of particles is not considered.

#### What is the effect in the energy efficiency vs. quality of results tradeoff?

Effectively combining heterogenous with approximate computing to gracefully tradeoff application output quality with energy/performance gains requires a systematic approach to executing programs using the principles heterogeneous and approximate computing. We introduce a set of 7 applications, that are part of AcHEe (Approximate Computing and Heterogeneity for Energy efficiency), modified to exploit both heterogeneity and approximate computing. Our application set is developed using mainly OpenCL nomenclature, therefore it can target any architecture and accelerator device supporting OpenCL. Each application comes with both accurate and approximate implementations of its computationally intensive parts. The latter exploit different types of approximations, carefully chosen to balance between energy efficiency and quality degradation of results. For example, in the case of the DCT MV application we find that the combination of heterogeneous and approximate computing resulted in 98.7% improved energy efficiency compared with a fully accurate execution on a CPU, at the expense of a tolerable quality loss (PSNR lower by 5 dB, from 38 dB to 33 dB).

## 1.4 Outline

Chapter 2 provides the technical background assumed by the following Chapters.

Chapter **3** introduces our approach for exploiting CPU voltage margins reduction under power-constrained execution. To this end, we present RVSCap, a novel CPU power capping mechanism that operates the CPU at reduced voltage margins, minimizes the performance penalty of power capping at restrictive caps, reduces the power footprint at more generous caps and supports multiple platforms.

Later, in Chapter 4, we introduce xDVS. xDVS is a dynamic voltage scaling governor that exploits the workload dependability of CPU voltage margins. More specifically, we discuss the prediction models of voltage margins reduction and then focus on the design, implementation and evaluation of the xDVSgovernor.

Chapter 5 validates RVSCap and xDVS. We, then, discuss system reliability, fault-tolerance aspects and present the expected energy gains in large-scale deployments where a fault-tolerance mechanism, such as checkpointing, is necessary.

Chapter 6 introduces (XM)<sup>2</sup>, a framework to automate experimental campaigns for CPU voltage margins characterization, application profiling, xDVS and RVSCapvalidation and evaluation.

Then, in Chapter 7, we present our modifications to a set of applications in order to exploit both heterogeneity and approximate computing. In particular, we showcase in practice different approximation techniques for various applications. Moreover, we show that when these approximations are combined with the utilization of accelerators, such as GPUs, the energy efficiency is significantly improved.

Finally, Chapter 8 concludes the dissertation.

## **Chapter 2**

# Background

This Chapter outlines the necessary background to assist the reader in following the discussion in the subsequent Chapters, which introduce the contributions of this dissertation.

## 2.1 Platforms Overview

This Section explains how we adjust the operating points of the CPUs used in the context of this dissertation (Table 2.1), briefly discusses their power-saving modes and outlines their performance monitoring functionality.

#### 2.1.1 Intel-Based systems

#### **Frequency adjustment**

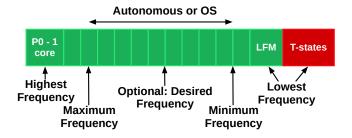

Intel CPUs from the Skylake family, and later on, feature the Speedshift [8] mechanism. As shown in Figure 2.1, Speedshift enables fully autonomous control of P-State selection by the CPU, known as Hardware P-States (HWP), supporting a dynamic, wide power range with faster transition times between the minimum and maximum supported CPU frequencies. To this end, for all the CPUs, utilized in the context of

| Characteristic              | Xeon E3-1220v5        | i7-4790K              | X-Gene 2 | X-Gene 3 |

|-----------------------------|-----------------------|-----------------------|----------|----------|

| CPU Cores                   | 4                     | 4                     | 8        | 32       |

| Hardware threads            | 4                     | 8                     | 8        | 32       |

| Base clock freq.            | 3.0GHz                | 4.0GHz                | 2.4GHz   | 3.0GHz   |

| Turbo clock freq.           | 3.3GHz                | 4.4GHz                | -        | -        |

| Lowest clock freq.          | 0.8GHz                | 0.8MHz                | 0.3GHz   | 0.375GHz |

| Supply Voltage ( $V_{dd}$ ) | 1.15V                 | 1.07V                 | 0.98V    | 0.87V    |

| Manufacturer                | Intel                 | Intel                 | APM      | APM      |

| Family                      | Skylake               | Haswell               | ARMv8    | ARMv8    |

| Technology                  | 14nm                  | 22nm                  | 28nm     | 16nm     |

| Max Performance             | 4 (issue-slots/cycle) | 4 (issue-slots/cycle) | 4 (IPC)  | 4 (IPC)  |

| Freq. Control               | HWP                   | P-State               | CPPC     | CPPC     |

| TDP (W)                     | 80                    | 88                    | 35       | 125      |

Table 2.1: Characteristics of the four target CPUs.

Figure 2.1: Speedshift overview.

this dissertation, all cores are clocked with the same frequency. The OS may disable autonomous scaling by setting the maximum and minimum frequencies of a P-State to the same value. Prior Intel CPUs, before the Skylake family such as the Haswell family, feature a similar mechanism, namely the Intel P-State driver, which features the same logic as Speedshift but is implemented in software.

#### Supply voltage adjustment

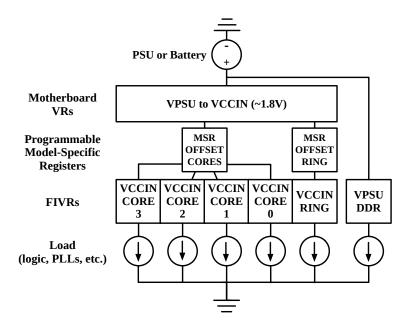

Moreover, the latest generations of Intel CPUs, from the Haswell family and later on, feature the Fully Integrated Voltage Regulator (FIVR) [9] mechanism which selects the optimal supply voltage  $V_{dd}$  for CPU cores according to the frequency of the CPU cores and the executing workload (Figure 2.2). More specifically, FIVR operation requires the presence of voltage regulators (VRs) which are separated into two stages, with the first stage of VRs responsible for converting the Power Supply Unit (PSU) or battery voltage (12-20V) to approximately 1.8V and distributing it across the CPU

Figure 2.2: Overview of Intel FIVR.

die. The second stage is comprised of inner-chip VRs – the total number of VRs is product dependant – which are 140 MHz synchronous multiphase buck converters with up to 16 phases. Each FIVR is independently programmable to achieve optimal operation of the domain it is powering.

It is possible for the software to alter the supply voltage, as shown in Equation 2.1, by writing an offset value into specific Model-Specific Registers (MSRs). Although there are separate MSRs for the core and uncore components, we empirically observed that the supplied voltage changes only when both registers are set to the same value. Thus, we operate the core and the uncore components with the same voltage offset (MSR<sub>offset</sub>). Note that FIVR does not support an independent per-core adjustment of the offset, therefore the offset applies to all CPU cores.

$$V'_{dd} = V_{dd} - MSR_{offset} \tag{2.1}$$

#### Power and performance monitoring mechanisms

Furthermore, Intel CPUs can save energy when idling, by setting CPU cores in a low-power mode. There are several such modes, or so-called *C-states*, which perform clock and power gating to different units inside the core. C-states are numbered starting from C0, the normal CPU operating state in which all CPU modules are powered up and clocked. Higher power-saving states result in an increasing number of circuits and signals being power- or clock-gated, putting the core into a deeper sleep state. The deeper the core sleep state, the higher the performance and energy penalty to revert to C0.

Another power-related mechanism in the arsenal of modern Intel CPUs, including the ones used in the context of this dissertation, is the RAPL [10] mechanism. RAPL is a hardware power reporting and capping mechanism that directly observes the power consumption of the CPU. When RAPL enforces a power cap, it samples CPU power consumption within a user-specified time window and solves a linear equation [10, 11] to dynamically decide and apply the most suitable frequency and voltage pair from the DVFS operating points supported by the CPU. The cap enforcement time window can be as narrow as 1 msec.

To quantify the interaction of applications with hardware Intel CPUs have on-chip Performance Monitoring Units (PMUs), used. For the CPUs used in this dissertation, only up to 8 performance counters per core can be monitored simultaneously. When the hyper-threading capability is enabled, the number of available registers is reduced to 4. Exceeding these limits causes the interleaved monitoring of performance counters. Typically, the PMUs are used by profilers to obtain the CPU resource utilization.

### 2.1.2 ARM-based platforms

#### **Frequency adjustment**

Both ARMv8 microprocessors, namely the Applied Micro's X-Gene 2 and X-Gene 3, used in the context of this dissertation, offer high-end processing performance and contain a dedicated subsystem that features Power Management processor (PMpro) which is orchestrated by a Scalable Lightweight Intelligent Management processor (SLIMpro) to enable flexibility in power management, resiliency, and end-to-end security. The dedicated PMpro processor exposes advanced power management capabilities, such as thermal protection, configures system attributes (e.g. regulates supply voltage, etc.) and clock gating mechanisms. Such capabilities are monitored and managed by the SLIMpro which communicates directly with PMpro through an integrated I<sup>2</sup>C controller and can be accessed by the Linux kernel.

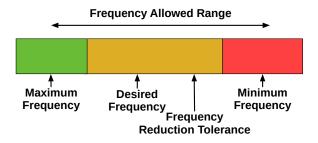

Both processors support the Collaborative Processor Performance Control (CPPC) power and performance management API as it is defined in ACPI 5.0+ specification. CPPC is a new approach to control the CPU performance using an abstract continuous scale in contrast with the traditional discretized P-state scale. As shown in Figure 2.3, the flow of adjusting the operating frequency involves initially the OS making a change request of the frequency to the platform. The communication between the OS and platform occurs through the Platform Communication Channel (PCC). Afterward, the platform (in our case the PMPro) optimizes the new frequency request (desired performance), taking into consideration the maximum, lowest and reduction tolerance performance factors. Also, the frequency can be adjusted at the granularity of CPU cores pairs, which are called PMDs, and can range from 300 MHz up to 2.4 GHz at 300 MHz steps in X-Gene 2 and from 375 MHz to 3.0 GHz at 100 MHz steps in X-Gene 3.

Figure 2.3: CPPC API overview.

#### Supply voltage adjustment

Moreover, both microprocessor chips have three independently regulated voltage domains the PMD (Processor MoDule), PCP (Processor Complex) and the Standby Power domain, with which we can selectively regulate the voltage independently. The power domain that includes the CPU cores as well as the cache memories hierarchy is the PMD (Processor MoDule) domain (shown in Figure 2.4) and is the one that consumes the largest part of the overall power consumption. All the PMDs (4 PMDs in X-Gene 2 and 16 PMDs in X-Gene 3) operate at the same voltage which can change from the nominal 980mV downwards in X-Gene 2 and from the nominal 870mV in X-Gene 3. The PCP domain includes the operating voltage of the DRAM controllers, the central switch and the I/O bridge. Also, the Power Standby domain includes the SLIMpro and PMpro microcontrollers and the corresponding interfaces for the I<sup>2</sup>C buses.

#### Power and performance monitoring mechanisms

The SLIMpro mechanism can read and report the current power consumption of all power domains of the X-Gene processors. In contrast with Intel CPUs, the X-Gene processors do not feature any power capping mechanism. However, they do offer Performance Monitoring Units which capture the computational characteristics of applications. For both X-Gene processors only up to 4 performance counters per core can be monitored simultaneously.

Figure 2.4: Overview of PMD domain of X-Gene processors [12].

## 2.2 Centaurus Runtime & Programming Model

This Section provides an overview of the Centaurus Runtime & Programming model [13], which we use for the study on the combination of heterogeneous and approximate computing which we discuss in Chapter 7.

#### 2.2.1 Platform model

Centaurus assumes a heterogeneous system, consisting of several accelerator devices capable of performing computations independently of the main host CPU. Each of these devices is typically based on a different hardware architecture, thus contributes a unique set of capabilities to the overall system. Energy consumption may be significantly different between devices too, depending on the architecture, semiconductor fabrication geometry, and device utilization. Also in the general case, the availability of each device on a heterogeneous system is not known at any given time. Devices may be busy or disabled depending on the overall system configuration.

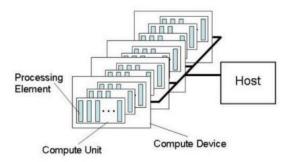

The Centaurus platform inherits the typical OpenCL [14] platform model, depicted in Figure 2.5, providing an abstract execution model for all available devices. That means as a rule, that the programmer can not – in general – make assumptions such as which device executes which computation, however, they can suggest, or even enforce execution on a specific device.

Figure 2.5: OpenCL Platform Model [14]

### 2.2.2 Execution Model

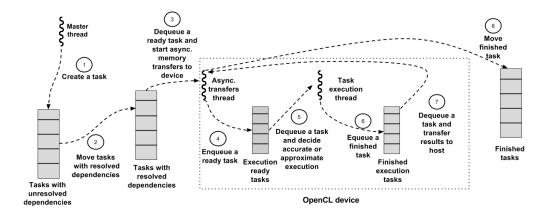

The execution model also resembles the OpenCL one: the main computation is organized in tasks, each implemented as an OpenCL kernel. The tasks execute on one or more devices, and a host program manages task creation and synchronization.

The programmer defines and spawns tasks from the host program, annotated with information about their significance for the quality of results and data dependencies.

The compiler generates different code versions for each case, accurate and approximate. The underlying Centaurus runtime system is responsible for orchestrating the execution and the selection of the accurate or approximate implementation for each task, based on information provided by programmers/end-users through directive clauses. Figure 2.6 depicts the life cycle of a task, from creation to completion.

Figure 2.6: Task life in the Centaurus framework.

A newly spawned task usually has to wait on a queue until all its data dependencies are resolved. Then the runtime transfers its input data to the OpenCL device it will be executed on, executes it either accurately or approximately and then transfers back the output results to the host memory.

#### 2.2.3 Directives

Throughout this Section we employ Discrete Cosine Transform (DCT), a code module used in many multimedia algorithms, as a minimal example to illustrate the use of the main programming model concepts. DCT transforms image blocks to blocks of frequency coefficients. Coefficients corresponding to lower spatial frequencies are more significant for the quality of the final image, due to the fact that the human eye is more sensitive to those frequencies. Listing 2.1 outlines the implementation of DCT.

Listing 2.2 summarizes the *#pragma* directive used for task creation. The body of the accurate implementation of the task is defined as a function call, which corresponds to an OpenCL kernel. We explain each clause referring to our DCT example in Listing 2.1.

The *significant()* clause specifies the relative significance of the computation implemented by the task for the quality of the output, with a value (or an expression) in the range [0.0, 1.0]. If set to 1.0 or omitted, the runtime will always execute the task accurately. If set to zero, the runtime will always execute the task approximately, or

```

1 void dctAccurate(double *image,double *result,int subblock) {/*OpenCL code*/}

2 void dctApprox(double *image, double *result, int subblock) {/*OpenCL code*/}

4 int subblocks=2*4, subblockSize=4*2, blockSize=32, imgW=1920, imgH=1080;

5 /*DCT block to 2x4 subblocks with different significance, image dimensions*/

6 double sgnf_lut[] = { 1, .9, .7, .3,

7 .8, .4, .3, .1};

8 void DCT(double *image, double *result, double sgnf_ratio) {/* entry point */

for (int id = 0; id < subblocks; id++) { /*spawn dct task group*/

9

#pragma acl task in(image) out(&result[id*subblockSize]) \

10

label("dct") \