# Models and Algorithms of Soft Error Inducing Mechanisms in ICs

by

### Pelopidas Tsoumanis

Submitted to the Department of Electrical and Computer Engineering in partial fulfillment of the requirements for the degree of

Doctor of Philosophy in Electrical and Computer Engineering

at the

#### UNIVERSITY OF THESSALY

February 2021

© Pelopidas Tsoumanis 2021. All rights reserved.

| Author       |                                                                        |

|--------------|------------------------------------------------------------------------|

|              | Pelopidas Tsoumanis                                                    |

|              | Department of Electrical and Computer Engineering<br>February 24, 2021 |

| Certified by |                                                                        |

|              | George Stamoulis                                                       |

|              | Professor                                                              |

|              | Thesis Supervisor                                                      |

| Accepted by  |                                                                        |

| 1 0          | Christos D. Antonopoulos                                               |

|              | Associate Professor                                                    |

|              | Chairman, Department Committee on Graduate Theses                      |

# Models and Algorithms of Soft Error Inducing Mechanisms in ICs

by

#### Pelopidas Tsoumanis

Submitted to the Department of Electrical and Computer Engineering on February 24, 2021, in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Electrical and Computer Engineering

#### Abstract

Reliability of Integrated Circuits (ICs) has always been one of the primary concerns in VLSI field, let alone nowadays, when the continuous technology shrinking that follows the Moore's Law renders them more susceptible to various factors. Recently, the reliability challenge of radiation-induced Soft Errors has drawn remarkable attention of many researchers. A particle of sufficient energy that strikes a transistor may create a disturbance of the equilibrium between the electron and holes within the device and result in changing the logic state of the gate output that usually lasts for some picoseconds. This temporary phenomenon that emerges as a glitch, called Single Event Transient (SET), at the output pulse may affect the proper operation of the circuit as it propagates, and eventually get captured by a storage element. This is called a Soft Error and, although it is not permanent, it may cause unexpected behavior to the circuit. Therefore, it is important for the industry to be acquainted with the circuit susceptibility to such kind of errors, especially when it comes to critical systems, such as medical, avionics, military, etc.

In this dissertation, we present an integrated framework for the modeling of the radiation-induced Soft Errors in the combinational logic of ICs, providing an evaluation of the Soft Error Rate (SER), a widely-used metric for the susceptibility of ICs to such hazards. The proposed methodology, which is based on Monte Carlo simulations, takes into consideration the physical layout of a circuit to deal with the Single Event Multiple Transients (SEMTs), which have become more prevalent with the continuous technology downscaling. Two variations of the main SER estimation algorithm, for the identification of the most susceptible areas of a circuit and the most vulnerable gates, are also presented, allowing for slight modifications of either the circuit design, or the placement strategies in the early design stages, or both to mitigate SER. The SER evaluation results are demonstrated by a variety of simulations performed on ISCAS '89 benchmark suite for both 45nm and 15nm technologies and their verification with HSPICE simulation tool indicates an acceptable deviation for the small-scale circuits. Finally, the behavior of the state-of-the-art Fully-Depleted Silicon-On-Insulator (FDSOI) process technology concerning the ion-

izing particle strikes is examined and compared with the traditional Bulk technology through TCAD simulations.

Thesis Supervisor: George Stamoulis

Title: Professor

# Μοντέλα και Αλγόριθμοι Προσομοίωσης Μηχανισμών Πρόκλησης Μεταβατικών Σφαλμάτων σε Ολοκληρωμένα Κυκλώματα

του

### Πελοπίδα Τσουμάνη

Υποβλήθηκε στο Τμήμα Ηλεκτρολόγων Μηχανικών και Μηχανικών Υπολογιστών στις 24 Φεβρουαρίου 2021, ως μερική εκπλήρωση των απαιτήσεων για τον Διδακτορικό Τίτλο Ηλεκτρολόγου Μηχανικού και Μηχανικού Υπολογιστών

### Περίληψη

Η αξιοπιστία των Ολοκληρωμένων Κυκλωμάτων (ΟΚ) ήταν ανέκαθεν μία από τις πιο συχνές ανησυχίες στον τομέα του VLSI, πόσο μάλλον σήμερα, που η συνεχής συρρίχνωση της τεχνολογίας που αχολουθεί το Νόμο του Moore τα χαθιστά πιο ευάλωτα σε διάφορους παράγοντες. Η πρόκληση που έχει να κάνει με την αξιοπιστία και τα Μεταβατικά Σφάλματα που προκαλούνται από ιονίζουσα ακτινοβολία κερδίζει συνεχώς έδαφος και έχει τραβήξει την προσοχή αρκετών ερευνητών προσφάτως. Ένα σωματίδιο επαρχούς ενέργειας που συγχρούεται με ένα τρανζίστορ μπορεί να προχαλέσει διαταραχή στην ισορροπία μεταξύ ηλεκτρονίων και οπών εντός της συσκευής, έχοντας ως αποτέλεσμα την αλλαγή της λογικής κατάστασης της εξόδου της πύλης που διαρχεί συνήθως ορισμένα picoseconds. Το προσωρινό αυτό φαινόμενο που εμφανίζεται ως ένας ανεπιθύμητος παλμός στην έξοδο, που καλείται και Single Event Transient (SET), μπορεί να επηρεάσει τη σωστή λειτουργία του κυκλώματος καθώς διαδίδεται και εν τέλει αποθηκεύεται σε κάποιο στοιχείο μνήμης. Αυτό ονομάζεται Μεταβατικό Σφάλμα και παρόλο που δεν είναι μόνιμο μπορεί να προκαλέσει απρόσμενη συμπεριφορά στο κύκλωμα. Έτσι, είναι σημαντικό για τη βιομηχανία να γνωρίζει την ευπάθεια των χυχλωμάτων σε τέτοιου είδους χινδύνους, ειδιχότερα όταν αυτά αφορούν χρίσιμα συστήματα, όπως ιατρικά, αεροηλεκτρονικά, στρατιωτικά, κ.ά.

Σε αυτήν τη διατριβή παρουσιάζουμε ένα ολοκληρωμένο πλαίσιο για τη μοντελοποίηση των Μεταβατικών Σφαλμάτων εξαιτίας της ιονίζουσας ακτινοβολίας στη συνδυαστική λογική των ΟΚ, παρέχοντας μία εκτίμηση της Συχνότητας Μεταβατικών Σφαλμάτων (ΣΜΣ), ενός ευρέως διαδεδομένου μέτρου για την ευπάθεια των ΟΚ σε τέτοιους κινδύνους. Η προτεινόμενη μεθοδολογία που βασίζεται σε Monte Carlo προσομοιώσεις, λαμβάνει υπόψην το φυσικό σχέδιο ενός κυκλώματος ούτως ώστε να μοντελοποιήσει τα Single Event Multiple Transients (SEMTs), τα οποία γίνονται ολοένα και πιο συχνά με τη συρρίκνωση της τεχνολογίας. Επίσης, παρουσιάζονται δύο παραλλαγές του κύριου αλγορίθμου της εκτίμησης της ΣΜΣ, για την ταυτοποίηση των ευαίσθητων περιοχών και των πιο ευαίσθητων πυλών ενός κυκλώματος, επιτρέποντας μικρές τροποποιή-

σεις είτε της σχεδίασης του χυχλώματος, είτε αχόμη και των στρατηγικών χωροθέτησής του στα πρώτα στάδια της σχεδίασης με σχοπό τη μείωση της ΣΜΣ. Τα αποτελέσματα της εχτίμησης της ΣΜΣ επιδειχνύονται με μία ποιχιλία προσομοιώσεων που πραγματοποιούνται πάνω στα ISCAS '89 χυχλώματα για τις τεχνολογίες των 45nm και 15nm, ενώ η επαλήθευση με το εργαλείο προσομοίωσης HSPICE υποδειχνύει αποδεχτή απόχλιση για τα μιχρής χλίμαχας χυχλώματα. Τέλος, εξετάζεται η συμπεριφορά της σύγχρονης τεχνολογίας κατασχευής ΟΚ Fully-Depleted Silicon-On-Insulator (FD-SOI) απέναντι στα χτυπήματα των σωματιδίων και συγχρίνεται με τη συμβατιχή Bulk τεχνολογία μέσω προσομοιώσεων TCAD.

Επιβλέπων Διατριβής: Γεώργιος Σταμούλης

Τίτλος: Καθηγητής

### Acknowledgments

As the curtain falls on this long, painstaking, but at the same time exciting journey of my doctoral studies, I would like to express my sincere appreciation and my deepest gratitude to some people that without their support and help, it would have been impossible for me to bring this dissertation to fruition.

First, I would like to thank my advisor, Professor George Stamoulis, for supervising my research progress, as well as for his invaluable guidance and constant support throughout my doctoral studies, contributing to my academic self-growth with his technical expertise. I would also like to thank my thesis committee members, Professor Nestor Evmorfopoulos and Professor Fotis Plessas, for assisting me to improve and refine this work with their insightful feedback. In addition, I would like to express my appreciation to my thesis examination committee members, Professor Michael Dossis, Professor Georgios Dimitriou, Professor Antonios Dadaliaris and Professor Spyridon Nikolaidis, for examining and accepting this dissertation, as well as for providing useful technical feedback. I would like to acknowledge all my workmates and friends in the Electronics Lab of the Department for the harmonious and constructive cooperation and, of course, the technical and secretarial support of the Department for facilitating my work throughout my studies.

Last but not least, I would like to thank from the bottom of my heart my family for the unreserved and wholehearted support. My deepest gratitude to my parents for the unconditional support, encouragement and for feeling empathy with my concerns. Without their emotional and financial generosity, this beautiful adventure would have not been crowned with success. Also, special thanks to all my friends for the priceless and unforgettable moments that we have shared all these years helping me to rest my mind outside of my research.

Dedicated to my family

This doctoral thesis has been examined by a Committee of the Department of Electrical and Computer Engineering as follows:

| Professor George Stamoulis                                                                                                |

|---------------------------------------------------------------------------------------------------------------------------|

| Chairman, Thesis Supervisor Professor of Electrical and Computer Engineering University of Thessaly                       |

| Professor Nestor Evmorfopoulos                                                                                            |

| Member, Thesis Committee Associate Professor of Electrical and Computer Engineering University of Thessaly                |

| Professor Fotis Plessas                                                                                                   |

| Member, Thesis Committee                                                                                                  |

| Associate Professor of Electrical and Computer Engineering University of Thessaly                                         |

| Professor Michael Dossis                                                                                                  |

| Member, Examination Committee Professor of Informatics                                                                    |

| University of Western Macedonia                                                                                           |

| Professor Georgios Dimitriou                                                                                              |

| Member, Examination Committee<br>Assistant Professor of Computer Science and Telecommunications<br>University of Thessaly |

| Professor Antonios Dadaliaris                                                                                             |

| Member, Examination Committee Assistant Professor of Computer Science and Telecommunications                              |

| University of Thessaly                                                                                                    |

| Professor Spyridon Nikolaidis                                                                                             |

| Member, Examination Committee Professor of Physics                                                                        |

| Aristotle University of Thessalonik                                                                                       |

# Contents

| A        | bstra  | ct      |                                    | V    |

|----------|--------|---------|------------------------------------|------|

| G        | reek   | Abstra  | act                                | vii  |

| Li       | ist of | Figur   | es                                 | xix  |

| Li       | ist of | Table   | s x                                | xiii |

| Li       | ist of | Abbre   | eviations                          | xxv  |

| 1        | Inti   | roducti | ion                                | 1    |

|          | 1.1    | Motiv   | ation                              | 1    |

|          | 1.2    | Autho   | or Contribution                    | 2    |

|          |        | 1.2.1   | Contribution                       | 2    |

|          |        | 1.2.2   | Publications                       | 3    |

|          | 1.3    | Outlin  | ne                                 | 5    |

| <b>2</b> | Bac    | kgroui  | nd                                 | 7    |

|          | 2.1    | Main    | Causes of Soft Errors              | 7    |

|          |        | 2.1.1   | Alpha particles                    | 8    |

|          |        | 2.1.2   | Cosmic radiation                   | 8    |

|          |        | 2.1.3   | Other sources                      | 10   |

|          | 2.2    | Soft E  | Errors on Silicon                  | 11   |

|          |        | 2.2.1   | Radiation interaction with silicon | 11   |

|          |        | 2.2.2   | Linear Energy Transfer             | 13   |

|   |                         | 2.2.3  | Modeling of the ionizing particle strike                        | 14 |  |  |

|---|-------------------------|--------|-----------------------------------------------------------------|----|--|--|

|   | 2.3                     | Soft E | rror Rate Mitigation                                            | 18 |  |  |

| 3 | Rela                    | ated W | /ork                                                            | 21 |  |  |

| 4 | Soft                    | Error  | Rate Estimation Framework                                       | 27 |  |  |

|   | 4.1                     | Maskii | ng Mechanisms                                                   | 27 |  |  |

|   |                         | 4.1.1  | Logical masking                                                 | 28 |  |  |

|   |                         | 4.1.2  | Electrical masking                                              | 28 |  |  |

|   |                         | 4.1.3  | Timing masking                                                  | 29 |  |  |

|   | 4.2                     | Single | Event Transients                                                | 30 |  |  |

|   |                         | 4.2.1  | Masking mechanisms modeling                                     | 30 |  |  |

|   |                         | 4.2.2  | Reconvergent transient pulses                                   | 35 |  |  |

|   |                         | 4.2.3  | Timing issues                                                   | 36 |  |  |

|   |                         | 4.2.4  | Failure probability calculation                                 | 39 |  |  |

|   |                         | 4.2.5  | Gate sensitivity evaluation                                     | 41 |  |  |

|   | 4.3                     | Single | Event Multiple Transients                                       | 42 |  |  |

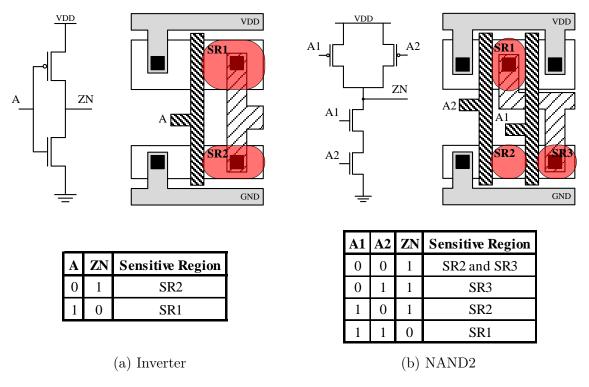

|   |                         | 4.3.1  | Sensitive regions                                               | 43 |  |  |

|   |                         | 4.3.2  | Multiple site identification                                    | 45 |  |  |

|   | 4.4                     | Overal | ll Soft Error Rate Estimation Flow                              | 49 |  |  |

| 5 | Experimental Results 55 |        |                                                                 |    |  |  |

|   | 5.1                     | Soft E | rror Rate Verification                                          | 55 |  |  |

|   | 5.2                     | Experi | imental Results                                                 | 59 |  |  |

|   |                         | 5.2.1  | Experimental setup                                              | 59 |  |  |

|   |                         | 5.2.2  | Impact of the electrical and timing masking modeling on the SER | 59 |  |  |

|   |                         | 5.2.3  | Impact of the masking mechanisms on SET propagation             | 61 |  |  |

|   |                         | 5.2.4  | Evaluation of the effect of SET and SEMT consideration on the   |    |  |  |

|   |                         |        | SER                                                             | 62 |  |  |

|   |                         | 5.2.5  | Circuit site and gate vulnerability evaluation                  | 66 |  |  |

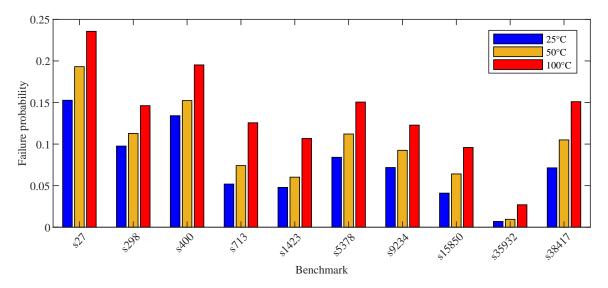

|   |                         | 5.2.6  | Temperature dependence of the SER                               | 68 |  |  |

|              |                                                              | 5.2.7  | Comparison among similar SER estimation approaches | 69         |

|--------------|--------------------------------------------------------------|--------|----------------------------------------------------|------------|

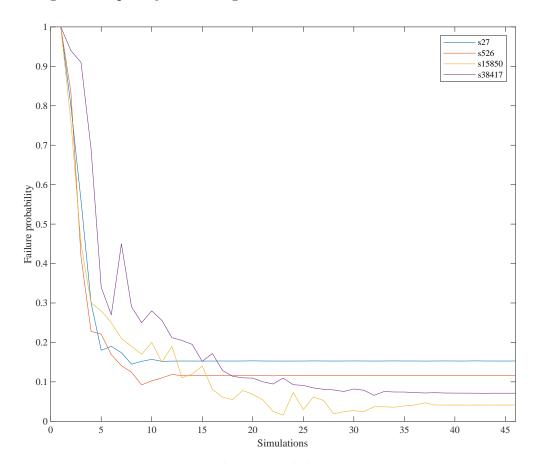

|              | 5.3                                                          | Speed- | up of SER Estimation                               | 71         |

| 6            | Soft                                                         | Error  | s in FDSOI Technology                              | <b>7</b> 5 |

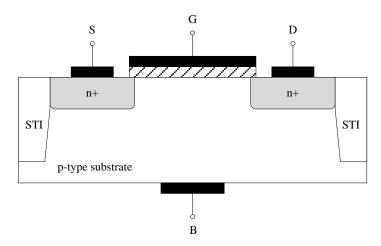

|              | 6.1                                                          | About  | Silicon On Insulator Technology                    | 75         |

|              | 6.2                                                          | Heavy  | Ion Strike TCAD Characterization                   | 77         |

|              |                                                              | 6.2.1  | About TCAD simulations                             | 77         |

|              |                                                              | 6.2.2  | Simulation setup                                   | 78         |

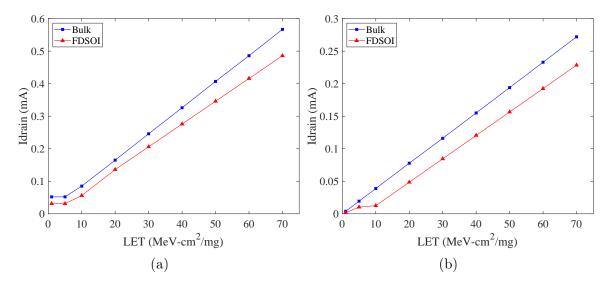

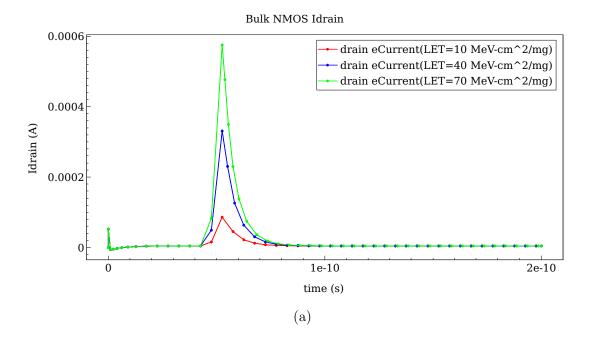

|              |                                                              | 6.2.3  | NMOS and PMOS device simulations                   | 80         |

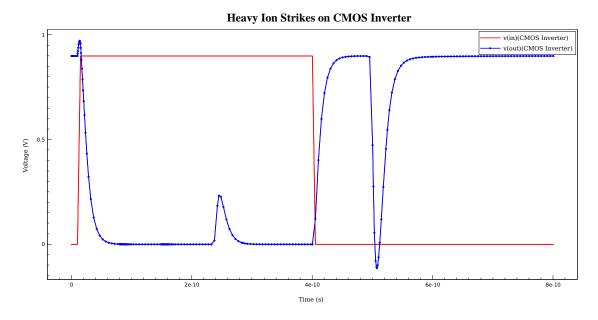

|              |                                                              | 6.2.4  | Mixed-mode CMOS Inverter simulation                | 82         |

| 7            | Conclusions and Future Work                                  |        |                                                    |            |

|              | 7.1                                                          | Conclu | nsion                                              | 85         |

|              | 7.2                                                          | Future | Work                                               | 86         |

| $\mathbf{A}$ | Overall SER Results of ISCAS '89 Benchmarks on 45nm and 15nm |        |                                                    |            |

|              | Tecl                                                         | nnolog | ies                                                | 89         |

| Bi           | bliog                                                        | raphy  |                                                    | 93         |

# List of Figures

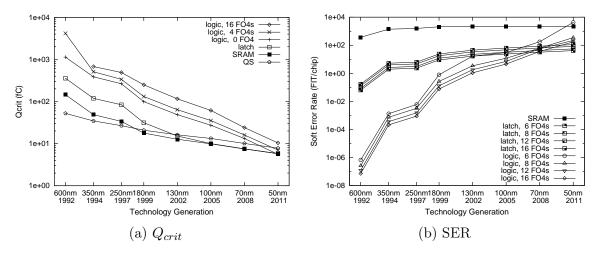

| 1-1 | CMOS technology generation trend of (a) critical charge $(Q_{crit})$ and |    |

|-----|--------------------------------------------------------------------------|----|

|     | (b) Soft Error Rate (SER) of SRAM cells, latches, and combinational      |    |

|     | logic                                                                    | 2  |

| 2-1 | Representation of various particle cascades as high-energy cosmic rays   |    |

|     | interact with earth's atmosphere                                         | 9  |

| 2-2 | Charge generation and collection due to a particle strike on a reverse-  |    |

|     | biased p-n junction. (a) Generation of electron-hole pairs along the ion |    |

|     | traversal, (b) quick drift charge collection and extension of the deple- |    |

|     | tion region towards the substrate forming a funnel, (c) slow diffusion   |    |

|     | charge collection, and (d) the generated current pulse on the transistor |    |

|     | node throughout this process                                             | 12 |

| 2-3 | Energy loss for alpha particles of 5.49 MeV moving through air           | 14 |

| 2-4 | Generated double exponential current pulse                               | 15 |

| 2-5 | Modeling of the radiation particle strike with a current source when     |    |

|     | the strike occurs on (a) nMOS transistor and (b) pMOS transistor of      |    |

|     | an Inverter.                                                             | 16 |

| 2-6 | Particle striking the off pMOS of a CMOS Inverter                        | 17 |

| 4-1 | A SET resulted from an ionizing particle strike on a NAND2 gate          |    |

|     | is subjected to the three masking mechanisms, i.e., (a) logical, (b)     |    |

|     | electrical, and (c) timing, as it propagates through the circuit         | 28 |

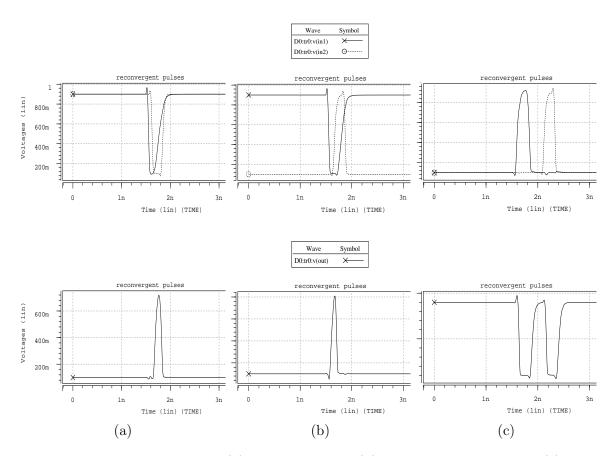

| 4-2 | Output pulses for (a) same direction, (b) different direction, and (c) non-                                                          |    |

|-----|--------------------------------------------------------------------------------------------------------------------------------------|----|

|     | overlapping input reconvergent pulses                                                                                                | 36 |

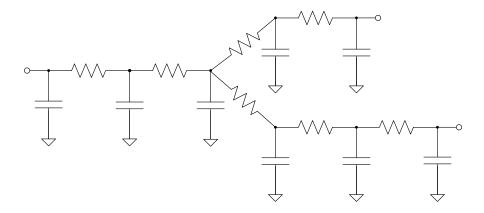

| 4-3 | Distributed RC interconnection tree                                                                                                  | 38 |

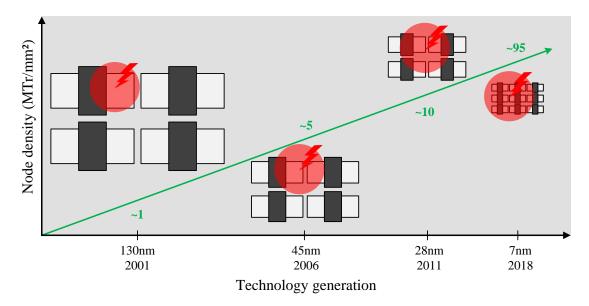

| 4-4 | Node density and SEMTs increase as technology downscales                                                                             | 43 |

| 4-5 | Illustration of the sensitive regions upon the physical layout and their                                                             |    |

|     | dependency on the logic input values of two basic logic cells, (a) In-                                                               |    |

|     | verter and (b) NAND2                                                                                                                 | 44 |

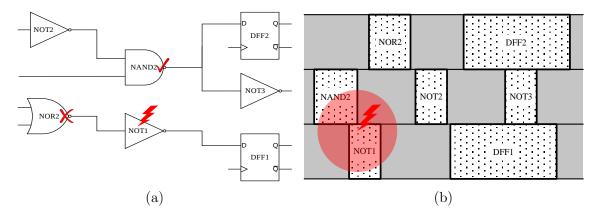

| 4-6 | Juxtaposition of (a) netlist-based and (b) layout-based identification                                                               |    |

|     | of adjacent gates revealing the inaccuracy of the former approach                                                                    | 46 |

| 4-7 | Snippet of (a) COMPONENTS and (b) NETS block statements of a                                                                         |    |

|     | DEF file                                                                                                                             | 46 |

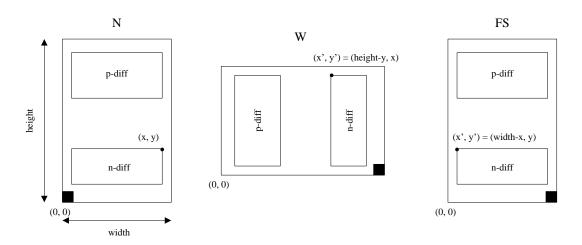

| 4-8 | Mapping of the diffusion areas depending on the standard cell orientation.                                                           | 48 |

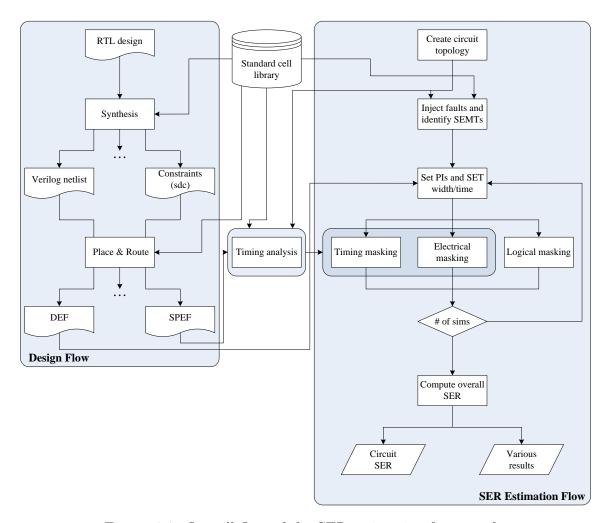

| 4-9 | Overall flow of the SER estimation framework                                                                                         | 52 |

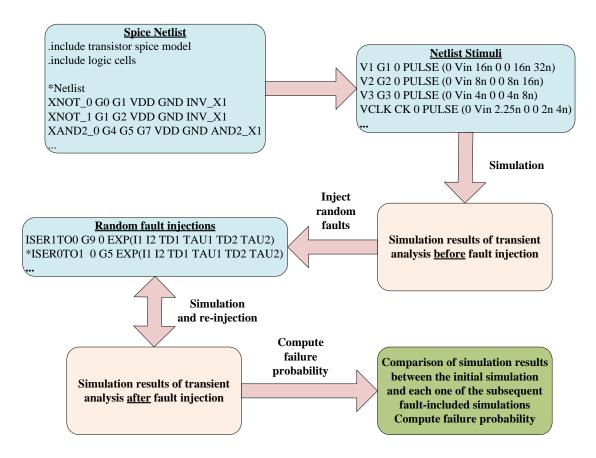

| 5-1 | HSPICE simulation flow for verification                                                                                              | 57 |

|     |                                                                                                                                      | 51 |

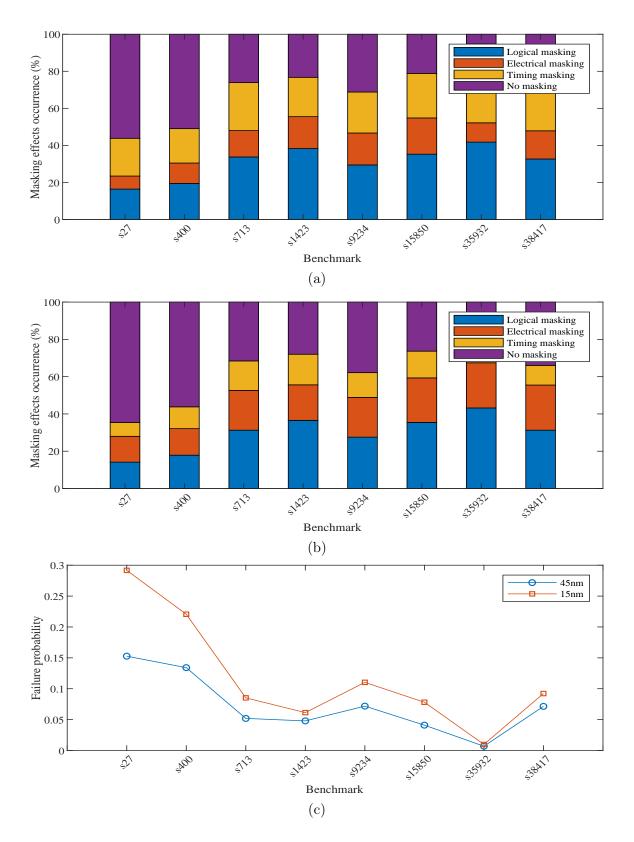

| 5-2 | Impact of the masking effects on the propagation of radiation-induced SETs through some benchmark circuits for (a) 45nm and (b) 15nm |    |

|     | technologies, and (c) the corresponding failure probabilities                                                                        | 63 |

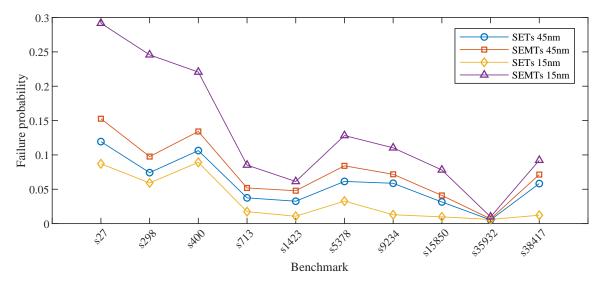

| 5-3 | Failure probabilities of the benchmarks considering SETs and SEMTs                                                                   | 00 |

| J-J | for both 45nm and 15nm technologies                                                                                                  | 64 |

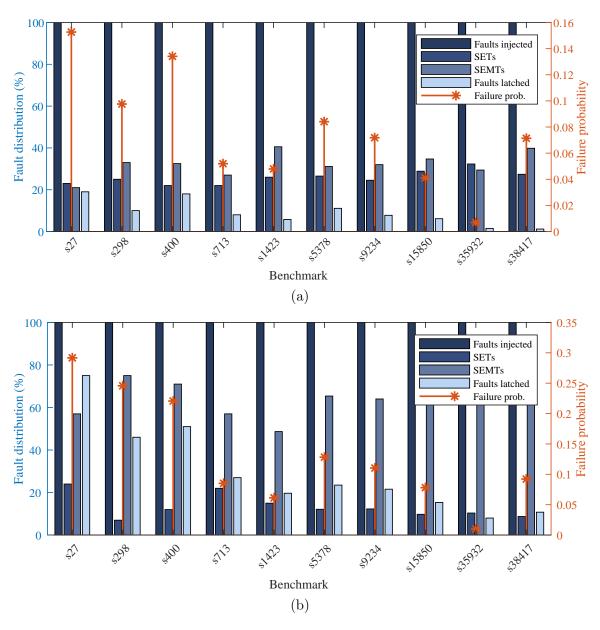

| 5 1 | Percentage of injected faults inducing SETs or SEMTs and being latched                                                               | 04 |

| 5-4 | by a FF, and the corresponding failure probability of some benchmarks                                                                |    |

|     | for (a) 45nm and (b) 15nm technology                                                                                                 | 65 |

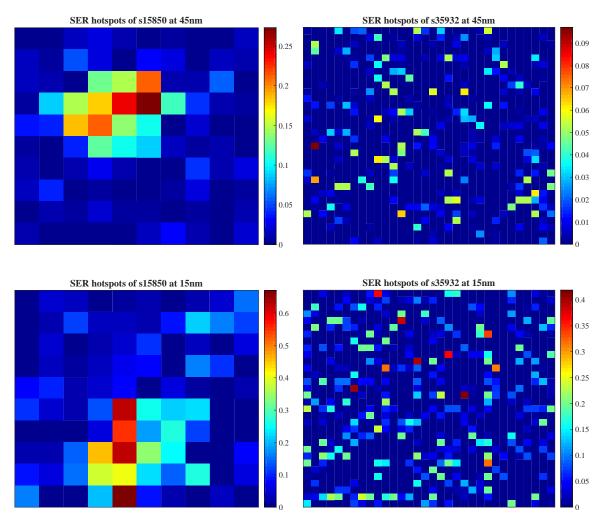

| 5-5 | Illustration of the SER hotspot circuit regions of s15850 and s35932                                                                 | 00 |

| 0-0 | benchmarks for both 45nm and 15nm technologies                                                                                       | 67 |

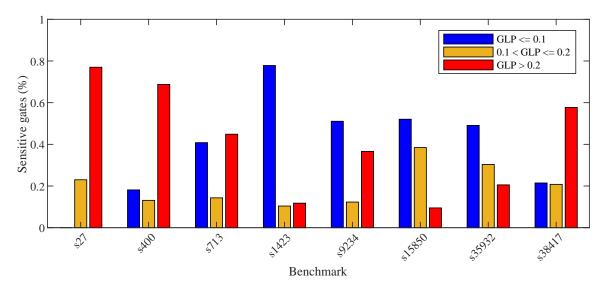

| 5-6 | Distribution of the gates depending on their sensitivity (GLP values)                                                                | 01 |

| 9-0 | for some benchmarks                                                                                                                  | 68 |

| 57  |                                                                                                                                      | 00 |

| 5-7 | Impact of operating temperature on the failure probabilities of some benchmarks                                                      | 69 |

| ۲O  |                                                                                                                                      |    |

| 5-8 | Failure probability convergence                                                                                                      | 73 |

| 6-1 | Structure of a typical bulk nMOSFET device                            | 76 |

|-----|-----------------------------------------------------------------------|----|

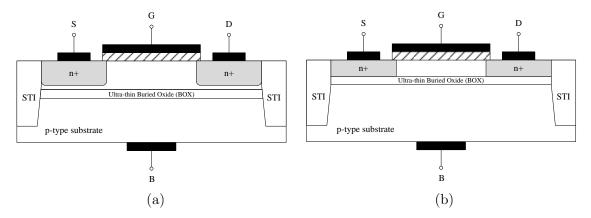

| 6-2 | Structure of typical (a) PDSOI and (b) FDSOI nMOSFET devices          | 77 |

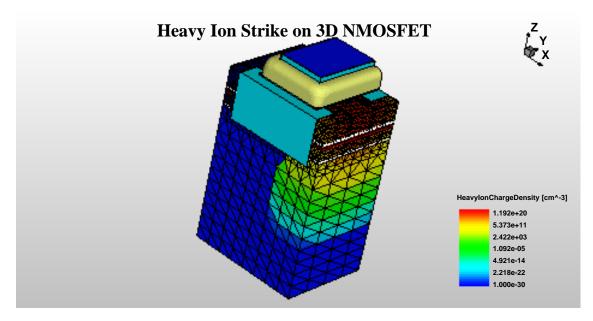

| 6-3 | 3D illustration of a heavy ion strike on the drain of nMOSFET and     |    |

|     | the induced charge generation along its track                         | 81 |

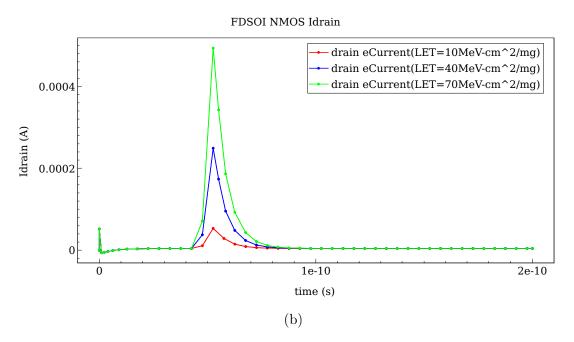

| 6-4 | SET drain current for various LETs and both Bulk and FDSOI tech-      |    |

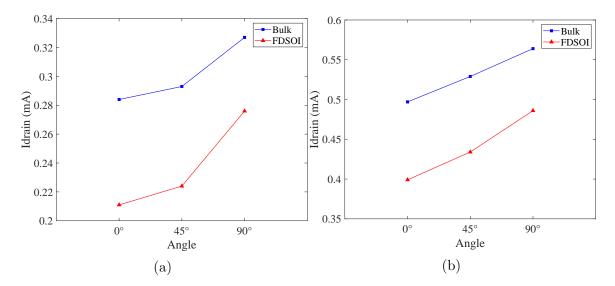

|     | nologies when (a) nMOSFET and (b) pMOSFET are affected                | 82 |

| 6-5 | nMOS drain current pulses for various LETs of (a) Bulk and (b) FDSOI  |    |

|     | technologies                                                          | 83 |

| 6-6 | SET drain current for three different strike angles and both Bulk and |    |

|     | FDSOI technologies when (a) nMOSFET and (b) pMOSFET are affected.     | 84 |

| 6-7 | Transient plot of a CMOS Inverter when two heavy ions strike the      |    |

|     | nMOS and pMOS transistor at different time moments                    | 84 |

# List of Tables

| 4.1 | Propagation delays and output pulse widths for a NAND2 gate and for                                                                                                                       |    |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | both transitions considering 100ps, 300ps, and 500ps input pulse widths                                                                                                                   | 34 |

| 4.2 | Average affected area                                                                                                                                                                     | 47 |

| 5.1 | Number of faults injected for each benchmark                                                                                                                                              | 56 |

| 5.2 | Verification results of failure probability                                                                                                                                               | 58 |

| 5.3 | Comparison of the proposed electrical and timing masking models with HSPICE on various SET pulse propagation paths                                                                        | 58 |

| 5.4 | Failure probabilities considering the closed-form approach and the NLDM-based approach for electrical masking and for both 45nm and 15nm technologies on a subset of ISCAS '89 benchmarks | 60 |

| 5.5 | Failure probabilities considering LE, NLDM and RC Interconnection approaches for both 45nm and 15nm technologies on a subset of ISCAS '89 benchmarks                                      | 61 |

| 5.6 | Qualitative comparison of the proposed tool with other state-of-the-art SER estimation approaches                                                                                         | 70 |

| 5.7 | Runtimes and speed-up of SER estimation execution on some ISCAS '89 benchmarks                                                                                                            | 74 |

| 6.1 | Physical parameters of nMOS devices                                                                                                                                                       | 79 |

A.1 SER evaluation results, obtained from the proposed tool, for the IS-CAS '89 benchmarks and 45nm technology. The number of nodes, primary inputs, gates and D-FFs indicate the benchmark complexity, Fail. Rate and FIT denote the SER as failure probability and in terms of FIT, respectively, whereas Ex. Time is the average execution time.

90

A.2 SER evaluation results, obtained from the proposed tool, for the IS-CAS '89 benchmarks and 15nm technology. The number of nodes, primary inputs, gates and D-FFs indicate the benchmark complexity, Fail. Rate and FIT denote the SER as failure probability and in terms of FIT, respectively, whereas Ex. Time is the average execution time.

91

### List of Abbreviations

BPSG BoroPhosphoSilicate Glass

CMOS Complementary Metal-Oxide-Semiconductor

DEF Design Exchange Format

EDA Electronic Design Automation

FDSOI Fully Depleted Silicon On Insulator

FF Flip-Flop

FinFET Fin Field-Effect Transistor

FIT Failures In Time

GDSII Graphic Design System II

GLP Glitch Latching Probability

IC Integrated Circuit

LEF Library Exchange Format

LET Linear Energy Transfer

LUT Look-Up Table

MSET Multiple Single Event Transient

MOSFET Metal-Oxide-Semiconductor Field-Effect Transistor

MTTF Mean Time To Failure

NLDM Non-Linear Delay Model

SEE Single Event Effect

SEMT Single Event Multiple Transient

SER Soft Error Rate

SET Single Event Transient

SEU Single Event Upset

SOI Silicon On Insulator

TCAD Technology Computer-Aided Design

VLSI Very Large-Scale Integration

# Chapter 1

### Introduction

### 1.1 Motivation

The motivation behind this dissertation derives primarily from the constant reliability concerns in the VLSI field regarding the radiation-induced Soft Errors. Besides, due to the technology shrinking, which entails higher operating frequencies and lower supply voltages, cell capacitances and critical charges (the minimum required charge to induce a node upset,  $Q_{crit}$ ), rendering the modern chips more susceptible to such hazards, the need for a comprehensive analysis of the soft errors and their impact on IC's operation becomes even more imperative and the contribution of simulation tools to the development of robust and error-tolerant chips tends to be significant. It has been shown that the atmospheric neutron Soft Error Rate (SER) in SRAM cells increases with the decreasing of device feature sizes [1], whereas an increasing susceptibility of sequential and static combinational devices to alpha particles and an accretion of multi-bit upset probabilities have been observed with technology scaling [2], despite the fact that the reduction in charge collection area has been reported to compensate for the critical charge scaling trend. Also, the technology trends are expected to result in a considerable increase in the soft error rates in combinational logic, compared to sequential logic [3, 4]. The significant reduction in the critical charge of the logic circuits, as device feature size decreases, has a massive impact on the SER of the combinational logic, as shown in Figure 1-1. Several error correction

Figure 1-1: CMOS technology generation trend of (a) critical charge  $(Q_{crit})$  and (b) Soft Error Rate (SER) of SRAM cells, latches, and combinational logic [3].

schemes that have emerged are able to protect the memories from soft errors, although it has been reported that there is a saturation in the soft error mitigation [5]. Thus, an accurate and effective framework for the evaluation of circuit vulnerability in combinational logic, through the integration of EDA tools that simulate sufficiently the soft error radiation-inducing mechanisms, may be further exploited in the design process of error-resistant deep submicron and nanoscale systems through the development and employment of radiation-hardening techniques. At the same time, the emergence and evolution of unconventional silicon semiconductor technologies and devices (e.g., PDSOI or FDSOI wafers, FinFETs, etc.), which are utilized from the state-of-the-art microelectronic ICs, may differentiate both the reliability evaluation process—constituting a challenge and an open field of research—and the outcomes.

### 1.2 Author Contribution

#### 1.2.1 Contribution

In this dissertation, we have dealt with the radiation-induced soft errors in the combinational logic of ICs. An integrated algorithm for SER estimation accounting for multiple transient faults is developed. The implemented tool, which is based on Monte Carlo simulations, models and incorporates the fundamental parts of a SER estimation in combinational logic, that is the three masking mechanisms. We exploit the results of a Single Event Transient (SET) pulse characterization process and the detailed layout information of the designs to achieve an accurate reliability assessment. Note that the terms SET and transient fault are equivalent, and thus they are used interchangeably in this dissertation.

A significant part of this research is the results regarding the SER of various benchmarks. In particular, the whole suite of ISCAS '89 benchmark circuits are used to demonstrate their susceptibility to ionizing radiation. Also, we perform a topological analysis of the circuit physical layout to obtain the most vulnerable circuit sites, allowing for selective slight modifications of the logic cells' placement to combat the high soft error rates. Moreover, the gate sensitivity is identified through a metric, called Glitch Latching Probability (GLP), which represents the impact of masking mechanisms on SET pulse propagation. Finally, a comparison of our work with other similar works with respect to the factors that are taken into consideration for SER evaluation from each one of them is reported. The verification of the results is conducted with HSPICE demonstrating a quite close convergence.

While our main work focuses on the analysis of soft errors in the conventional Bulk CMOS technologies, the emergence of cutting-edge technologies, such as SOI, FDSOI and FinFET, has raised the interest in examining the impact of ionizing radiation on such technologies. Thus, we conclude this work presenting various results of mixed-mode and 3D TCAD simulations, which characterize the behavior of FDSOI devices when a heavy-ion strike occurs. The results are compared with those of the Bulk technology indicating which of them are more susceptible to such hazards.

#### 1.2.2 Publications

Throughout the doctoral studies the author has submitted, published and presented his work in various international conferences and proceedings as listed below.

• G. I. Paliaroutis, P. Tsoumanis, G. Dimitriou and G. I. Stamoulis, "SER Analysis for Multiple Affected Gates". International Conference on Computer Science,

Computer Engineering, and Social Media (CSCESM), Special Session on High-Level Synthesis, CAD and Applications, December 12–14, 2014, Thessaloniki, Greece.

- G. I. Paliaroutis, P. Tsoumanis, G. Dimitriou and G. I. Stamoulis, "SER Analysis of Multiple Transient Faults in Combinational Logic". ACM SouthEast European Design Automation, Computer Engineering, Computer Networks and Social Media Conference (SEEDA-CECNSM), September 25–27, 2016, Kastoria, Greece.

- G. I. Paliaroutis, P. Tsoumanis, G. Dimitriou and G. I. Stamoulis, "Placement-aware Simulation of Multiple Transient Faults in Combinational Logic". Accepted for publication at North Atlantic Test Workshop (NATW) 2017.

- G. I. Paliaroutis, P. Tsoumanis, N. Evmorfopoulos, G. Dimitriou and G. I. Stamoulis, "Placement-based SER estimation in the presence of multiple faults in combinational logic". 27th International Symposium on Power and Timing Modeling, Optimization and Simulation (PATMOS), September 25–27, 2017, Thessaloniki, Greece.

- G. I. Paliaroutis, P. Tsoumanis, N. Evmorfopoulos, G. Dimitriou and G. I. Stamoulis, "A Placement-Aware Soft Error Rate Estimation of Combinational Circuits for Multiple Transient Faults in CMOS Technology". IEEE International Symposium on Defect and Fault Tolerance in VLSI and Nanotechnology Systems (DFT), October 8–10, 2018, Chicago, IL, USA.

- G. I. Paliaroutis, P. Tsoumanis, N. Evmorfopoulos, G. Dimitriou and G. I. Stamoulis, "Multiple Transient Faults in Combinational Logic with Placement Considerations". 8th International Conference on Modern Circuits and Systems Technologies (MOCAST), May 13–15, 2019, Thessaloniki, Greece. (Best Paper Award nominee)

- C. Georgakidis, G. I. Paliaroutis, N. Sketopoulos, P. Tsoumanis, C. Sotiriou, N. Evmorfopoulos and G. Stamoulis, "A Layout-Based Soft Error Rate Estimation

and Mitigation in the Presence of Multiple Transient Faults in Combinational Logic". 21st International Symposium on Quality Electronic Design (ISQED), March 25–26, 2020, Santa Clara, CA, USA. (Virtual)

G. I. Paliaroutis, P. Tsoumanis, N. Evmorfopoulos, and G. Stamoulis, "On the Impact of Electrical Masking and Timing Analysis on Soft Error Rate Estimation in Deep Submicron Technologies". Accepted in Work-in-Progress Poster Session of Design Automation Conference (DAC), December 5–9, 2021, San Francisco, CA, USA.

His publication history includes as well a journal.

G. I. Paliaroutis, P. Tsoumanis, N. Evmorfopoulos, G. Dimitriou, and G. Stamoulis, "SET Pulse Characterization and SER Estimation in Combinational Logic with Placement and Multiple Transient Faults Considerations". Technologies 2020, 8, 5.

### 1.3 Outline

This PhD dissertation is organized as follows. Firstly, Chapter 1 introduces the motivation for this work and highlights the main author's contributions. Chapter 2 presents the background regarding the radiation-induced soft errors. Chapter 3 presents the relevant work that exists in the literature so far. Chapter 4 introduces the SER estimation methodology elaborating the algorithms and models that are implemented and incorporated into the proposed tool. Chapter 5 presents various simulation results performed on the ISCAS '89 benchmark suite as well as the verification framework with SPICE. A SET pulse characterization of FDSOI technology with a TCAD simulation software is presented in Chapter 6, and finally, Chapter 7 concludes this dissertation indicating some useful remarks.

## Chapter 2

## Background

In the past few decades, the radiation-induced soft errors have become one of the major issues regarding ICs reliability. Nowadays, this concern still remains in the spotlight as the semiconductor industry progress into the deep sub-micron technologies has rendered the chips more vulnerable to such hazards. This chapter presents an overview of the radiation-induced soft errors. First, the prevalent causes of soft errors in submicron devices are highlighted. Then, the radiation-induced SET generation mechanism in silicon is presented, indicating some critical aspects of the ionization and modeling such incidents in logic level. Finally, some of the well-known mitigation techniques to cope with the soft errors are outlined.

### 2.1 Main Causes of Soft Errors

The soft errors, which are also known as Single Event Upsets (SEU), constitute a subcategory of a wide classification called Single Event Effects (SEE), that is, upsets caused by an event, such as a single energetic particle [6]. The emergence of SEUs in spacial applications was initially observed in the middle of the 70s, when the authors in [7] reported anomalies in communication satellite operation, which resulted from the interaction of the galactic cosmic rays with the digital circuits causing the triggering of the Flip-Flops (FFs). However, the first tangible studies regarding soft errors occurring in terrestrial electronics emerged a few years later. Such errors, which

constitute a temporary, non-destructive effect that differs from the permanent of the hard errors, are mainly caused by alpha particles, energetic neutrons produced from cosmic radiation, and thermal neutrons.

### 2.1.1 Alpha particles

The authors in [8] introduced the alpha-particle-induced soft errors in dynamic memories. Particularly, they showed that the alpha particle emissions due to the radioactive decay (or alpha decay) of low concentrated impurities in the packaging materials of ICs, such as uranium and thorium, are able to penetrate the silicon creating enough electron-hole pairs that eventually cause single-bit flips. An alpha particle consisting of two protons and two neutrons bound together is identical to that of an Helium-4 nucleus and is symbolized as  $\alpha$ ,  $^4_2\alpha$  or  $^4_2$ He. The energy of the emitted alpha particles varies from 3 MeV to 7 MeV (average kinetic energy of 5 MeV), which is sufficient enough to provoke a disturbance, given that the minimum required energy to generate an elementary charge (electron-hole pair) is 3.6 eV in silicon. Thus, a single alpha particle is capable of generating about a million of electron-hole pairs across a path of just a few microns (2 to 3 microns) in length, resulting in the corruption of stored information, or else a soft error. Moreover, it should be noted that the emission rate of such particles depends on the purity of the materials used in fabrication process. In [9], the collected and critical charges due to alpha particle strikes were modeled, and the charge limits alteration as technology downscales indicated that the soft failure probability increases.

#### 2.1.2 Cosmic radiation

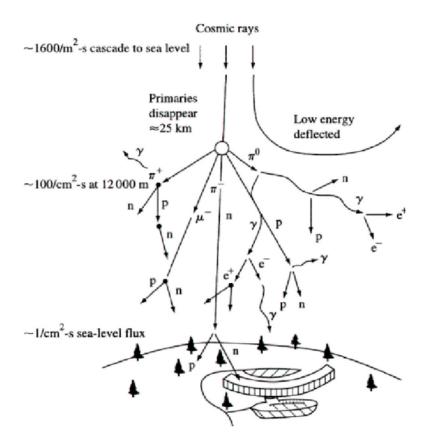

A prominent work presented in [10, 11] and followed by [12] some years later, revealed that cosmic radiation constitutes a significant threat for terrestrial electronic devices. In particular, the high-energy cosmic rays that bombard the earth interact with earth's atmosphere particles and a number of secondary particle cascades are produced, which, in turn, create further cascades, as shown in Figure 2-1.

Figure 2-1: Representation of various particle cascades as high-energy cosmic rays interact with earth's atmosphere particles [13].

In fact, due to the intensity of the collision between the cosmic rays and the atmospheric atoms, less than 1% of the primary particles eventually reach the sea level. Therefore, the terrestrial cosmic rays, that is the rays that are capable of reaching the earth, are primarily the cascade particles of third generation and above. The cascade particles consist of electrons, protons, photons, pions, muons and energetic neutrons. The last, which prevail at sea level (about 95% of the terrestrial particles, with the rest being protons and pions), may cause significant soft fails in electronics. Even if they are not charged, their interaction with the silicon nuclei in a chip may induce their fission producing several secondary fast heavy particles, which are able to generate, in the vicinity, electrical charges of more than four times as much as that of alpha particles. Such charge bursts are sufficient to upset a semiconductor device resulting in soft errors eventually. At high terrestrial altitudes, the percentage of protons and pions increases significantly and, as the cosmic ray intensity is greater, the

soft fails are more probable to occur in comparison with sea level. In addition, it has been reported that the extensive shielding of electronic devices with concrete is able to eliminate such soft fails, as the cosmic ray intensity approaches zero in such a case. The outcomes of this extensive research allow for SER evaluation in any location on earth, since the particle flux is known with high accuracy both at high altitudes and sea levels.

#### 2.1.3 Other sources

Except for the alpha particles and the energetic neutrons from cosmic rays, there are some further sources of soft errors. The cosmic ray thermal neutrons, that is the free neutrons—those that are not bounded in an atomic nucleus—having a low kinetic energy after reaching thermal equilibrium with the surrounding materials, may potentially pose a significant threat to the proper operation of semiconductor devices. Thermal neutrons feature higher cross-section in fission of certain materials, compared to high-energy neutrons, thus resulting in the emission of reaction products. The study presented in [14] showed that the interaction of thermal neutrons with isotopes of Boron <sup>10</sup>B is a significant source of soft errors. The <sup>10</sup>B nucleus is extremely unstable and when it captures a thermal neutron the resultant fission releases an excited <sup>7</sup>Li nucleus, an alpha particle and a gamma photon, which may subsequently generate a charge in the silicon and provoke a soft error. In semiconductor device fabrication, boron serves as a p-type dopant and is used in borophosphosilicate glass (BPSG) as well. BPSG layers are widely utilized as top passivation layers of semiconductor devices and as intermetal dielectric insulating layers. The <sup>10</sup>B fission in the BPSG is reported to be a significant source of soft errors in BPSG-based electronic devices [15, 16], as the <sup>10</sup>B concentration is higher compared to the other implant layers. Thus, the utilization of the alternative <sup>11</sup>B isotope—which has a lower capture cross-section that contributes less to soft errors—for the BPSG of the critical designs can be a drastic radiation-hardening technique to mitigate SER. In advanced CMOS technologies, however, the copper interconnects that have superseded the aluminum interconnects are subject to a different fabrication process, rendering the use of BPSG obsolete, and thus such sources of soft errors are regarded insignificant.

Finally, a minor source of soft errors originates from signal integrity issues, such as crosstalk between neighboring nets due to the cross coupling capacitance. Nevertheless, the contribution of such sources to the overall SER is rather insignificant when compared to radiation hazards.

### 2.2 Soft Errors on Silicon

#### 2.2.1 Radiation interaction with silicon

To proceed further in the analysis of the radiation-induced soft errors in the combinational logic of ICs, it is important to comprehend the basic mechanism of ionizing particles striking the silicon, regarding their interaction with the material and the immediate consequences on the proper device operation. The fundamental structural components of modern electronics are the transistors and, particularly, the MOSFETs which have been the dominant semiconductor devices since the 1960s. Nowadays, an IC chip, such as a microprocessor, consists of some billions of transistors which is a result of the device scaling and miniaturization, and the rapid growth of semiconductor technology in general. Thus, a potentially harmful ionizing particle may strike one or more of these transistors and affect the proper operation of the chip.

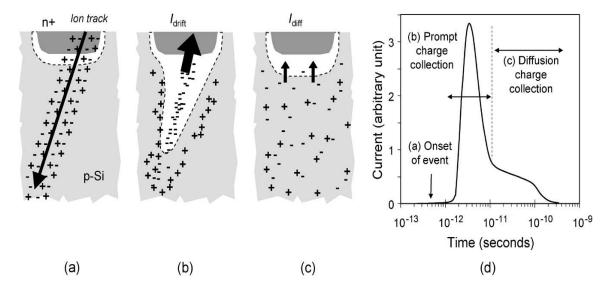

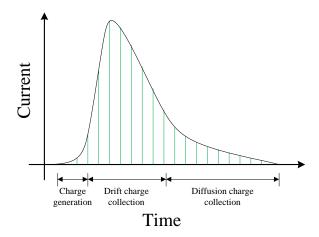

Suppose the MOSFET device (in particular NMOS transistor) of Figure 2-2 being stricken by a high-energy particle at the p-n junction area [17]. As the particle traverses through the silicon, a cylindrical track of electron-hole pairs is created and a series of physical processes take place contributing to the overall charge collection process. Upon the particle strike, a drift current, i.e. a movement of the deposited charge carriers, towards the p-n junction instantaneously emerges due to the electric field of the depletion region. At the same time, due to the IR drop in the substrate, being a result of the high current density, the charge potential, i.e. the depletion region, extends into the substrate forming a funnel, and thus enhancing the collection of the generated electrons in the well. Therefore, a substantial current emerges on the

Figure 2-2: Charge generation and collection due to a particle strike on a reverse-biased p-n junction. (a) Generation of electron-hole pairs along the ion traversal, (b) quick drift charge collection and extension of the depletion region towards the substrate forming a funnel, (c) slow diffusion charge collection, and (d) the generated current pulse on the transistor contact throughout this process [17].

particular device node. Afterwards, a slower diffusion collection process supersedes the fast and predominant drift collection. Due to the spatially varying charge concentration in the silicon between electrons and holes, the excess electrons diffuse and are collected from the depletion region. The overall current collected from the transistor's internal contact, throughout the whole process, is presented in Figure 2-2(d).

Additionally, there is another mechanism that contributes substantially to the overall charge collection. In the context of the previous illustration of charge collection process, while the electrons are collected rapidly from the drain (drift phase), excess holes in the well raise the well potential and lower the source/well potential barrier resulting in the injection of electrons from the source into the p-well. Thus, the electrons may be collected from the drain causing an increase in the total collected charge. This mechanism is the well-known parasitic bipolar effect (or amplification) due to the injection of the electrons over the source/well barrier acting like a transistor, where the source is the emitter, the channel is the base, and the drain is the collector of the transistor [18]. The parasitic bipolar effect has been found that contributes about 30% to the total collected charge in both 130-nm and 90-nm technologies,

whereas increases with rising temperature [19]. This indicates the significance of the parasitic bipolar effect to the radiation-induced generated current pulse, let alone with the continuous technology downscaling.

### 2.2.2 Linear Energy Transfer

Another problem of technology downscaling is that radiation particles of smaller energy, which usually have low penetration depth, may potentially cause transient faults by ionizing the atoms or molecules of the matter that they strike. The Linear Energy Transfer (LET) is an energy loss metric and, particular, the amount of energy per unit distance that a particle deposits, through ionization, to the material (i.e., semiconductor in this case) along its track. In other words, it is the retarding force that the ionizing particle gets as it penetrates the matter, and equals:

$$LET = \frac{dE}{dl} \tag{2.1}$$

where dE is the average energy locally imparted to the medium by a charged particle of specified energy when traversing a distance dl. LET is a positive quantity and is generally expressed in MeV/cm or  $MeV \cdot cm^2/mg$ , which results from the division with the material density  $mg/cm^3$ , whereas it depends mostly on the type of radiation particle, the traversed material and the angle of the strike. Also note that it is convenient to convert LET into charge per unit length (i.e., pC/mm) so as to be compared with the device physical dimensions and critical node charge stored.

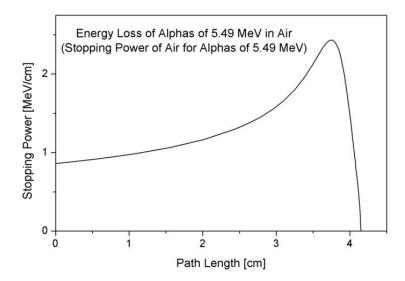

The ion energy, the energy loss (LET), and the depth (range) that the ion traverses are closely related. In particular, LET increases with increasing energy until reaching a maximum value, called Bragg peak, and then decreases with increasing energy. A Bragg peak is observed also in the plot of the energy loss of ionizing radiation during its travel through matter. In particular, the energy loss increases with the distance that the particle travels and reaches a maximum immediately before the end of the particle's path, as shown in Figure 2-3. The ion range is an important parameter as it should be sufficient to provoke charge collection into the silicon and depends on

Figure 2-3: Energy loss for alpha particles of 5.49 MeV moving through air.

the energy of the particle. As the energy increases, which means lower LET, Bragg peak moves deeper into the material and broadens and decreases. Therefore, this analysis demonstrates the interdependence of the individual factors and, mainly, the significance of LET in radiation effects.

## 2.2.3 Modeling of the ionizing particle strike

The overall collected charge, as a result of an ionizing particle striking the silicon p-n junction of a submicron device, corresponds to a current that emerges on the respective device contact. The charge collection current is sufficiently modeled with a widely-known approximation model, which utilizes a double exponential waveform and can be expressed as follows [20, 21]:

$$I_{particle}(t) = \frac{Q_{coll}}{\tau_{\alpha} - \tau_{\beta}} (e^{-t/\tau_{\alpha}} - e^{-t/\tau_{\beta}})$$

(2.2)

where  $Q_{coll}$  denotes the total collected charge from the p-n junction,  $\tau_{\alpha}$  is the time constant for the electron-hole pairs deposition in the p-n junction, and  $\tau_{\beta}$  is the time moment of the ion-track establishment, being just a few picoseconds and much less than  $\tau_{\alpha}$ . Generally,  $Q_{coll}$  depends on the type and energy of the particle that strikes the silicon, the angle of the strike, the proximity of the strike to the p-n junction, the

Figure 2-4: Generated double exponential current pulse.

temperature, the bias conditions, and the semiconductor device characteristics, such as the technology node, the supply voltage, the doping concentration, etc. The total  $Q_{coll}$  is equal to the area under the current curve, as shown in Figure 2-4. Therefore, given the generated current pulse,  $Q_{coll}$  can be obtained from the integral of the  $I_{particle}$  with respect to time, as follows:

$$Q_{coll} = \int_0^t I_{particle}(t)dt \tag{2.3}$$

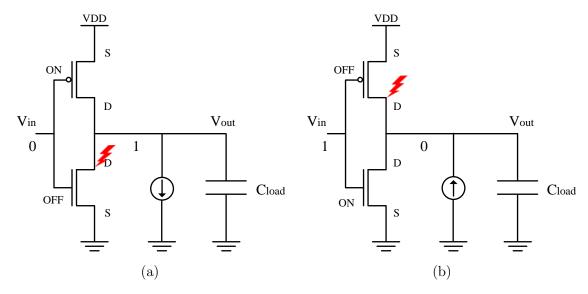

Moving from the device level to a higher abstraction level, i.e., transistor level, the incident of an ionizing particle strike can be simply modeled by connecting the double exponential independent current source, shown in Equation 2.2, to a particular transistor contact. Depending on the transistor that the particle strikes, the contact that the current source is attached to, and its direction vary. Note also that an ionizing particle may potentially affect a transistor solely when the transistor is inactive (or in cut-off state), which depends on the logic input state. Figure 2-5 presents the schematics of an inverter while a radiation particle strikes (a) the inactive nMOS and (b) the inactive pMOS transistor. To be more specific, an ionizing particle striking the inactive nMOS transistor is modeled with a current source attached to its drain with the direction being from the drain contact to the body contact (Figure 2-5(a)). Similarly, a particle striking the inactive pMOS transistor is modeled with the current source attached to its drain, but with the direction being from the body contact to

the drain contact (Figure 2-5(b)).

Figure 2-5: Modeling of the radiation particle strike with a current source when the strike occurs on (a) nMOS transistor and (b) pMOS transistor of an Inverter.

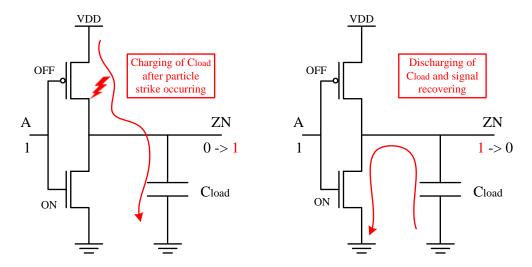

The double exponential current source model is used for the electrical simulation of transient faults with SPICE due to radiation particle strikes on sensitive circuit nodes, allowing for the circuit susceptibility evaluation to such hazards and the characterization of the transient faults, accounting for various factors, such as supply voltage, temperature, load capacitance, etc. In combinational logic, the injected current pulse may appear at the output of the logic gate as a voltage pulse or glitch (i.e., a prompt change of the logic state). The generated pulse may exceed the threshold level, that is the half of supply voltage, and temporarily settle to logic 1 or logic 0. Figure 2-6 shows an ionizing particle that strikes the inactive pMOS transistor of a CMOS Inverter. A glitch will emerge at the output of the gate as a result of the capacitor charging that succeeds the charge generation. Upon the ending of charge collection, the signal recovers to logic 0 through the discharging of the capacitor, indicating the end of the phenomenon.

However, there is a condition that should be met, that is, the resultant collected charge exceeds the minimum amount of charge required for a particle to induce the change of the output logic state. This charge is called critical  $(Q_{crit})$  and is mostly related to the device characteristics (e.g., manufacturing technology, doping level,

Figure 2-6: Particle striking the off pMOS of a CMOS Inverter.

device size, transistor capacitance, etc.), whereas can be estimated as follows:

$$Q_{crit} = C_{node} \cdot V_{dd}/2 \tag{2.4}$$

where  $C_{node}$  is the capacitance node and  $V_{dd}$  the supply voltage. A more accurate approximation of  $Q_{crit}$  can be obtained from electrical simulations with SPICE or device-level simulations with TCAD tools.

The value of  $Q_{crit}$  is significant and decisive for the emergence of transient faults and soft errors potentially. Thus, it may be associated with the technology nodes acting as an indicator of the device susceptibility to radiation hazards. However, the continuous shrinking of transistor geometries along with the supply voltage scaling result in decreasing values of  $Q_{crit}$ , which increases the soft error susceptibility of modern ICs raising the concerns regarding the reliability of future submicron technologies [22].

Generally, a radiation particle striking a sensitive silicon node induces different results depending on the circuit that this event emerges. In memories, a soft error emerges when the read operation occurs after the storage state value is modified. In SRAM memories, the particle strike may result in flipping the logic state of the cell, whereas in DRAM memories, the generated charge may affect the read or write operations due to the upset of the cell's logic and control circuits. On the other hand,

in combinational logic, the generated pulse at the gate output, called SET, may propagate along the forward cone paths of the circuit and be eventually captured by the storage elements, such as latches and FFs, inducing a soft error. However, the soft error inducing mechanism in combinational logic is much more complicated as there are individual mechanisms, i.e., masking effects, that occur and determine the emergence of soft errors.

# 2.3 Soft Error Rate Mitigation

Since the reliability of modern ICs is non-negotiable, constituting a major concern in the semiconductor industry, the development of methods and techniques to deal with the radiation-induced soft errors is indispensable. Over the recent decades, many approaches have emerged attempting to mitigate the SER of ICs. In general, certain techniques exist in the bibliography and are divided into hardware-level (system-level, device-level and circuit-level) and software-level techniques [23]. Since the SEEs constitute a hazard that primarily affect the proper operation of the circuit, the hardware-level mitigation techniques are more effective and prevail in this field of research. However, in some cases, alternative software-level mitigation schemes are selected to cope with the excessive hardware cost and power dissipation that the former techniques entrain.

At system-level, the radiation-hardening techniques that dominate include the addition of redundancy either in logic or memory circuits. In logic circuits, the Triple Modular Redundancy (TMR) can be utilized by replicating the hardware three times and filtering out any erroneous value with a majority voting logic. Usually, the area overhead is excessive, but this option is sometimes preferred to fully protect critical systems. As regards the memory circuits, a traditional technique to protect them against SEUs is to append a parity bit to the memory word, which is able to detect such upsets. Also, additional circuitry is needed to correct the detected errors, known as Error Correction Code (ECC). However, it may result in significant undesirable area cost and power penalties, especially when it comes to correction of multiple bit

errors, thus being difficult to be applied.

The purpose of the device-level mitigation techniques is to reduce the amount of collected charge due to a high-energy particle strike on the silicon by means of modifying the fabrication process. The most well-known approach is the Silicon-On-Insulator (SOI) technology, which is a variation of the conventional Bulk technology. In particular, the fabrication process differentiates by including an additional ultrathin insulating layer from silicon dioxide (SiO<sub>2</sub>), called Buried Oxide (BOX), within the substrate providing a different type of wafer. In this way, the silicon gap between the source and drain junctions decreases, preventing the development of high-collected charge values, and thus producing smaller SETs [24]. Nevertheless, this kind of mitigation technique is expensive in terms of time and cost, as it requires additional steps in the fabrication process.

Consequently, the interference in the hardware of the design constitutes the basic means of SER mitigation. At circuit-level, there are approaches that include the utilization of additional hardware to reduce the consequences of SEEs and harden the circuit. Several techniques that add spatial redundancy exist, such as the TMR method. The TMR module consists of three identical instances of the logic gate that need to be protected, utilizing a voting circuit (i.e., voter) that filters out the SET and propagates the correct logic value. Others, attempt to modify the delay of the SET through additional hardware (e.g., buffers and voting circuits) so as it cannot be latched from memory elements. There are also hybrid techniques that combine spatial and temporal redundancy methods to moderate the area overhead and operating frequency degradation. Finally, other radiation-hardening approaches increase the node capacitance or the driver's transistor sizes to avoid the excessive area and delay overheads.

In light of the overhead that such methods entrain, it is important that the radiation-hardening should be applied on just a small proportion of a circuit to avoid performance downgrading. Therefore, to selectively harden a circuit, a reliable and accurate evaluation of the vulnerability of ICs to radiation-induced hazards can be the determinant factor in the development of reliable electronic systems, through the

employment of radiation-hardening techniques.

# Chapter 3

# Related Work

Over the past years the ever-growing interest on the study and research of radiation-induced soft errors and their mechanisms has led to significant contribution and progress in this field. Since the relevant literature is vast, in the following paragraphs we will refer to the most representative studies that constitute a breakthrough and the works that have assisted in the further advancement of the academic research.

The first primitive approaches to estimate the SER in CMOS logic circuits emerged in the early 1990s [25, 26, 27]. In [25] the authors propose an algorithm to evaluate the propagation probabilities of single-event-induced errors modeled with closed-form equations. A method for predicting the SER due to  $\alpha$ -particle incidents of CMOS circuits with dynamic registers is presented in [26] and applied to a pipelined multiplier using data of future submicron technologies. In [27] a more advanced computer program, called SEMM, calculates the failure probabilities due to  $\alpha$ -particles and cosmic ionizing radiation, modeling the transient charge collection at the semiconductor junctions and contacts. A switch-level fault simulation algorithm of transients in CMOS is presented in [28]. The algorithm predicts the transient pulse widths, using a first order RC model, and models their propagation to subsequent logic blocks, setting appropriate propagation rules and eventually reducing fault simulation time.

Meanwhile, the gate-level simulation methodologies began gradually succeeding the old-fashioned and time-expensive electrical-level simulations. An intermediate approach of a transient fault simulator, using a PieceWise Quadratic approximation of the injected current pulse for the analytical solution of the MOS differential equations, is introduced in [29]. The authors in [30] present a sophisticated gate-level transient fault injection simulation environment, which uses logic-level and latching operation models to propagate the fault effects to the latch outputs. The majority of the works existing in the literature are based on the modeling and implementation of the three masking mechanisms that inherently mitigate the negative impact of radiationinduced faults on circuit reliability, i.e., logical, electrical, and timing masking [31, 32, 33, 34, 35, 36, 37, 38. Other works are based on probabilistic models to evaluate the SER [39, 40]. In [41] the authors perform a block-based SER analysis, based on an analytical expression for the electrical masking modeling. The authors in [42] evaluate the soft error circuit reliability through the development of a general computational framework, based on probabilistic transfer matrices (PTMs). In particular, matrix calculations are applied and Algebraic Decision Diagrams (ADDs) are utilized to form an overall circuit PTM, allowing for accurate reliability evaluation of large circuits. In [43] a balanced combination of probability and graph theory, circuit simulation, and fault simulation is employed, whereas a statistical method for SER estimation through closed-form models is presented in [44]. The statistical SER framework in [45] takes into consideration the full-spectrum of charge collection and achieves a fast result, exploiting SVM models for cell characterization, instead of LUT methods. The approach in [46] presents a statistical SER analysis, based on two frameworks—tablelookup and SVR-learning—to cope with the underestimation of SER due to the pulse width fluctuation after propagation. The authors in [47] propose a fast signaturebased SER framework that evaluates efficiently logical masking. The contribution of the particle striking time and multi-cycle effects to an accurate and efficient SER analysis, avoiding its underestimation, are discussed in [48].

However, the continuous process technology shrinking, resulting in the reduction of the distance among the logic cells, has made multiple transient faults, caused by single particle strikes, more prevalent, thus increasing circuit vulnerability [49, 50, 51]. Particularly, in [51] the authors perform a detailed characterization to quantify the likelihood of a SET to cause multiple bit-flips in logic circuits, proving that the

probability is quite significant, especially as technology scales, and therefore, such type of errors should be taken into account in order to obtain a realistic fault model for soft errors. Though none of the aforementioned works take into consideration this trend, a number of research studies on the evaluation of SER, considering Single Event Multiple Transients (SEMT), have emerged recently. Generally, there are two types of approaches that predominate in the literature: (i) the non-layout-aware [52, 53, 54] and (ii) the layout-aware [55, 56, 57, 58, 59, 60, 61]. The former works consider that SEMTs occur at the output of the physically adjacent gates, which are identified at the gate-level by examining fan-outs and fan-ins. Nevertheless, if only logic-level netlist is used for the determination of circuit error sites, neglecting the layout-level adjacency of the cells, may result in inaccurate estimation. Also, the authors in [54] assume that no more than three adjacent gates can be affected by a single event, which may eventually underestimate the SER evaluation. On the other hand, the latter provide a more realistic and reliable SER estimation analysis by taking into consideration the circuit layout. An intermediate approach that takes into account single and double transient faults on random nodes is presented in [62], focusing on the probabilistic logic simulation, albeit neglecting the electrical and timing masking effects, resulting in inaccuracies of the failure probability. The layout-aware approaches in [56, 57, 63] introduce the concept of sensitive regions of a cell that determines the fault generation. A recent unconventional approach, presented in [64], proposes a compact and fast SER estimation physical model in space environment, which relies solely on experimental cross-sectional data and LET spectrum of the ionizing particle.

Except for the methodologies that focus on the evaluation of SER, various approaches that combine the SER estimation and mitigation also exist in the bibliography. In [65] a combination of a sensitivity-based gate sizing algorithm and a slack-based FF selection are used to achieve SER reduction with reasonable costs. A symbolic framework for the circuit reliability analysis that is used for a selective gate resizing to succeed circuit hardening is presented in [66]. In [67] the authors propose a framework for adding and removing redundant wires to eliminate the gates that contribute most to the overall SER, which is enhanced with a gate resizing technique

to further optimize SER robustness. In [68] a sensitivity-based gate sizing methodology is presented, whereas a simulation-based approach in [69] aims at maximizing the logical masking potentiality by extracting sub-circuits and re-synthesizing them. A placement-based radiation hardening technique of removing whitespace between adjacent cells, which have common gates in their forward logic cones, and thus increasing the logical masking probability, is introduced in [70]. In [71] a Monte Carlo-based SER estimation method is presented along with two layout-aware approaches to mitigate SER: the first applies spacing among all the cells, whereas the second converts the most sensitive cells into a TMR structure, abiding by the minimum required distance among the TMR members to protect them against a potential SEMT occurence.

The research in this field is not confined to just simulation methodologies to evaluate the radiation-induced SER. On the contrary, a significant part of the bibliography conducts measurements through neutron beam testing setups that generate particles from a wide energy spectrum either to acquire important data to be used further in simulations, such as SET pulse widths, or to evaluate directly the vulnerability of a circuit.

The authors in [72] utilize the Oracle's neutron beam device for accelerated testing, highlighting the impact of technology scaling to the soft error rates. More specifically, the SEU rate per SRAM cell increases with the technology downscaling, whereas the multi-cell upsets are more prevalent due to the shrinking of the feature sizes. Finally, the negative impact of microprocessor energy reduction techniques on the SEU rate is noticed. In [73] the authors propose a SET pulse width measurement circuit, based on the propagation-induced pulse shrinking, whereas the simulation results of the neutron irradiation reveal the number of SETs, SEMTs, and MSETs (i.e., Multiple SETs) occurred. In [74] heavy ion experiments are conducted to characterize the SEMTs and provide measured results with respect to both cross-sections and pulse widths.

Although the real-time experiments constitute an important step to comprehend the behavior of modern chips into an environment of radiation fluxes, simulations are necessary to succeed scalability and obtain accurate results in a reasonable time. Besides, such simulation tools constitute the principal means of the assessment of an individual method. In [30, 75] the authors characterize the SET pulse generation and propagation under different design parameters through SPICE and TCAD simulations. In [76] the SET pulse width characterization results for 130nm and 90nm CMOS technologies through actual measurements are supported by 3D TCAD simulations, showing that pulse widths increase for the same radiation environment with technology scaling, whereas they are strongly related to the strike location. A built-in-self-test circuit implemented in a 45nm SOI technology is utilized for the heavy ion experiments to measure the SET pulse widths followed by mixed-mode 3D TCAD simulations to validate the results in [77].

# Chapter 4

# Soft Error Rate Estimation

# Framework

A comprehensive framework for SER estimation of modern ICs encompasses a considerable number of complex procedures that should be combined functionally. The subject of this chapter is to present all these necessary parameters and their incorporation to an integrated tool. First, the fundamental element of the proposed tool is presented, i.e., the natural masking mechanisms that are capable of mitigating soft errors. Second, the modeling of these factors and their integration for SER calculation regarding SETs follows. Third, the steps for an efficient and accurate consideration of multiple transients caused from a single particle strike are discussed. And, finally, the flow and the extensive algorithm of the implementation concludes this chapter.

# 4.1 Masking Mechanisms

To develop a reliable and accurate SER estimation framework, first and foremost, it is important to model sufficiently and accurately the masking mechanisms that inherently determine the capability of a circuit to absorb and eliminate soft errors. These factors, which hold a crucial role in the emergence of soft errors are logical, electrical and timing masking. The next subsections describe the masking mechanisms modeling and implementation as they are integrated into a SER estimation tool.

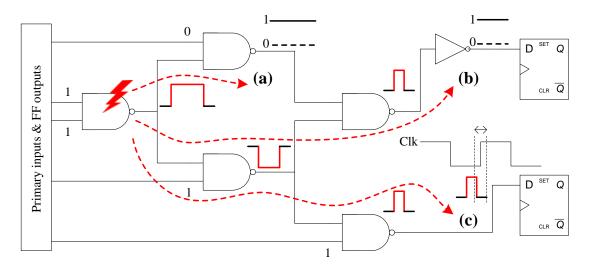

Figure 4-1: A SET resulted from an ionizing particle strike on a NAND2 gate is subjected to the three masking mechanisms, i.e., (a) logical, (b) electrical, and (c) timing, as it propagates through the circuit.

#### 4.1.1 Logical masking

The first factor that prevents a transient fault from propagating through the circuit is Logical Masking and its name is due to the circuit logic, that is the logic gates that are used for the implementation. In particular, as a transient pulse at the output of a gate propagates through the forward cone it may arrives at a gate whose other input is in a controlling value. The controlling value is the value at a gate input that is sufficient to determine the gate output. As a result, the transient fault cannot propagate through this gate, and thus is masked. Depending on the type of the logic gate, the controlling value differs. A NAND gate has a controlling value of 0, which means that whenever this value emerges at its input, the output is at logic 1 regardless of the other inputs. For instance, in Figure 4-1(a), the transient fault at the output of the first NAND2 gate is logically masked at a subsequent NAND2 gate due to a controlling value of the other input, that is, logic 0.

# 4.1.2 Electrical masking

As mentioned, as soon as an ionizing particle strikes a gate, the glitch that emerges at the output propagates through the logic gates of the forward cone. However, the nonlinear electrical properties of the CMOS gates might impede it from its propagation. On one side, the pulse itself might not be sufficiently strong, in terms of width and amplitude, i.e., its duration is small, to charge or discharge the output capacitor, thus settling the output voltage level to logic 1 and logic 0, respectively. On the other side, the shape, and thus the width of a glitch is modified due to the difference in rise and fall transition delays. Therefore, the attenuation of the generated glitch that generally occurs as it propagates through the subsequent gates is called Electrical Masking. Obviously, a slow gate has a greater contribution to electrical masking than a fast. In Figure 4-1(b) a pulse generated at the output of NAND2 gate, after a few logic stages, is completely eliminated.

### 4.1.3 Timing masking