### MASTER THESIS

### Electronic Design Automation Algorithms for Radiation-Hardening Standard Cell Legalisation with Respect to Circuit Performance

Student: Christos Georgakidis cgeorgakidis@uth.gr Supervisor: Christos Sotiriou chsotiriou@e-ce.uth.gr Committee: Georgios Stamoulis georges@e-ce.uth.gr Fotios Plessas fplessas@e-ce.uth.gr

A thesis submitted in fulfillment of the requirements for the degree of Master

in the

Circuits & Systems Laboratory (CASlab) Department of Electrical and Computer Engineering

October 18, 2019

#### Abstract

Faults caused by ionising radiation have become a significant reliability issue in modern Integrated Circuits (ICs). The solution to this problem is to apply Radiation-Hardening techniques. However, the Radiation-Hardening design flow differs from the standard design flow. Thus, there is not sufficient support from industrial Electronic-Design-Automation (EDA) tools. In current master thesis, we present a Triple-Modular-Redundancy (TMR) Radiation-Hardening approach, based on (i) replacement of Flip-Flops (FFs) to a TMR structure, consisting of a FFs triplet and a majority voter, as well as (ii) a custom Legalisation algorithm, able to satisfy user-specified, minimum distances among the FFs of each triplet. Our Radiation-Hardening Legaliser is fully compatible with existing industrial EDA tools. By ensuring a minimum spacing among triplet FFs of each TMR structure, we reduce the probability of a particle strike affecting more than one triplet instances. Comparing our customised legalisation algorithm with an industrial EDA tool supporting spacing constraints, the latter provides slightly better results. It is worth to mention that the industrial tool failed to terminate successfully for large designs due to lack of enough memory. Finally, we implemented a series of optimisations (MinMax-Bounded, HPWL-driven, Timing-driven). In some cases, these optimisations result in slightly worse results compared to the industrial tool, while in other cases, it provides better results. Thus, our Radiation-Hardening flow can be attractive for reducing radiation faults.

#### Περίληψη

Σφάλματα που προκαλούνται από ιονίζουσα ραδιενέργεια έχουν καταλήξει να αποτελούν ένα σημαντικό πρόβλημα στα σύγχρονα ολοκληρωμένα κυκλώματα (ICs). Η λύση σε αυτό το πρόβλημα είναι η εφαρμογή Ραδιατιον-Ηαρδενινγ τεχνικών. Ωστόσο, η Radiation-Hardening ροή σχεδίασης ολοκληρωμένων κυκλωμάτων διαφέρει από την συμβατική ροή σχεδίασης. Αυτό έχει ως αποτέλεσμα να μην υπάρχει επαρκής υποστήριξη από τα βιομηχανικά Electronic-Design-Automation (EDA) εργαλεία. Στην παρούσα διπλωματική εργασία παρουσιάζουμε μία Triple-Modular-Redundancy (TMR) Radiation-Hardening προσέγγιση, που βασίζεται (α) στην αντικατάσταση όλων των Flip-Flops (FFs) του κυκλώματος με TMR δομές, αποτελούμενες από μία τριπλέτα από FFs και έναν voter, ο οποίος επιστέφει την πλειοψηφία της τριπλέτας, καθώς επίσης και (β) ενός τροποποιημένου αλγορίθμου εγκυροποίησης κυκλώματος, ο οποίος ικανοποιεί μία ελάχιστη απόσταση μεταξύ των FFs κάθε τριπλέτας, η οποία ορίζεται από το χρήστη. Ο Radiation-Hardening αλγόριθμός μας είναι πλήρως συμβατός με τα υπάρχοντα βιομηχανικά ΕDA εργαλεία. Εγγυώντας μία ελάχιστη απόσταση μεταξύ των FFs μίας τριπλέτας, μειώνουμε την πιθανότητα ένα φορτισμένο σωματίδιο να επηρεάσει περισσότερα από ένα μέλη της τριπλέτας. Συγκρίνοντας τα αποτελέσματα για Ισχύ, Απόδοση και Εμβαδό του κυκλώματος (PPA) του δικού μας αλγορίθμου και ενός βιομηχανικού EDA εργαλείου, ακολουθώντας την ροή του για την ικανοποίηση περιορισμών απόστασης μεταξύ στοιχείων του κυκλώματος, το τελευταίο οδηγεί σε οριακά καλύτερα αποτελέσματα αλλά είναι συγκρίσιμα με τα αποτελέσματα του δικής μας προσέγγισης, ενώ αξίζει να σημειωθεί ότι το βιομηχανικό εργαλείο απέτυχε να τελειώσει επιτυχώς σε μεγάλα κυκλώματα εξαιτίας της έλλειψης μνήμης. Τέλος, υλοποιήσαμε μία σειρά από βελτιστοποιήσεις (MinMax-Bounded, HPWL-driven, Timing-driven) οδηγώντας είτε σε οριακά χειρότερα αλλά συγκρίσιμα ή ακόμη και καλύτερα αποτελέσματα από το βιομηχανικό εργαλείο, κάνοντας τη Radiation-Hardening ροή που ακολουθήσαμε ελκυστική για την μείωση των σφαλμάτων που προκαλούνται από ακτινοβολία.

## Acknowledgements

I would like to thank my thesis supervisor Prof. Christos Sotiriou, who was always available and willing to help whenever I ran into trouble or had a question about my research and guided me in the right direction whenever he thought I needed it. I would also like to thank Prof. Georgios Stamoulis and Prof. Fotios Plessas for the confidence they showed in my face.

I would like also to thank the members of the CASlab, who created a friendly environment, and especially Nikos Sketopoulos and Stavros Simoglou, who helped me in my thesis research.

Finally, I would like to express my acknowledgements to my parents and my friends supporting me throughout my years of study at the University of Thessaly.

Christos Georgakidis Volos, 2019

## Electronic Design Automation Algorithms for Radiation-Hardening Standard Cell Legalisation with Respect to Circuit Performance

Christos Georgakidis cgeorgakidis@uth.gr

Copyright © Christos Georgakidis 2019

Με επιφύλαξη παντός δικαιώματος. All rights reserved.

Αλγόριθμοι Ηλεκτρονικού Αυτοματισμού Σχεδίασης Κυκλωμάτων για την Ανθεκτική σε Ακτινοβολία Εγκυροποίηση Στοιχείων Δεδομένου της Απόδοσης του Κυκλώματος

> Χρήστος Γεωργακίδης cgeorgakidis@uth.gr

Copyright © Χρήστος Γεωργακίδης 2019

Με επιφύλαξη παντός δικαιώματος. All rights reserved.

## Contents

| 1 | Intr | oduction                                         | 6  |

|---|------|--------------------------------------------------|----|

| 2 | The  | oretical Background                              | 8  |

|   | 2.1  | Introduction to EDA                              | 8  |

|   |      | 2.1.1 Placement                                  | 9  |

|   | 2.2  | RADHARD Background                               | 12 |

|   |      | 2.2.1 Types of Radiation in Space                | 12 |

|   |      | 2.2.2 Radiation Effects in electronics           | 13 |

|   |      | 2.2.3 Radiation Hardening Techniques             | 17 |

| 3 | Exis | sting Works                                      | 20 |

|   |      | Existing Works in the Literature                 | 20 |

|   |      | 3.1.1 Radiation Hardening in the Literature      | 21 |

|   |      | 3.1.2 Industry Approach                          | 22 |

|   | 3.2  | Thesis' Used Tool                                | 23 |

|   |      | 3.2.1 Abax Legaliser                             | 23 |

| 4 | RAI  | OHARD Legalisation                               | 29 |

| - |      | Min-bounded RADHARD Legalisation                 | 29 |

|   |      | 4.1.1 Create TMR Netlist                         | 30 |

|   |      | 4.1.2 TMR Groups and Minimum Spacing Constraints | 31 |

|   |      | 4.1.3 Abax Modification                          | 32 |

|   |      | 4.1.4 Satisfy Spacing Constraints                | 33 |

|   |      | 4.1.5 Create the list of the RADHARD Components  | 34 |

|   |      | 4.1.6 RADHARD Legalisation Algorithm             | 35 |

|   | 4.2  | MinMax-bounded RADHARD Legalisation              | 40 |

|   |      | 4.2.1 Maximum Spacing Constraint Handling        | 40 |

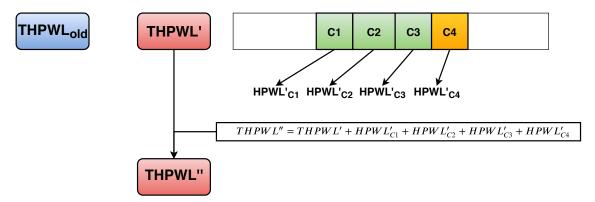

|   | 4.3  | HPWL-driven Legalisation                         | 43 |

|   |      | 4.3.1 Total Wirelength Calculation               | 43 |

|   |      | 4.3.2 Updated Cost Function                      | 43 |

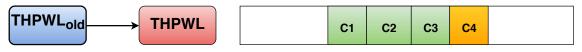

|   |      | 4.3.3 Update of THPWL                            | 44 |

|   | 4.4  | Timing-driven Legalisation                       | 47 |

|   |      | 4.4.1 Static Time Analysis Background            | 48 |

|   |      | 4.4.2 Cost Function                              | 52 |

| 5 | Exp  | erimental Results                                | 53 |

|   | 5.1  | Flow                                             | 54 |

|   |      | Min-bounded RADHARD Legalisation                 | 55 |

|   |      | Industrial RADHARD Legalisation                  | 56 |

| <ul> <li>5.4 Min-bounded VS Industrial RADHARD Legalisation</li></ul> | 58<br>59                    |

|-----------------------------------------------------------------------|-----------------------------|

| Conclusion and Future Work                                            | 61                          |

| Acronyms                                                              | 63                          |

| Designs Layouts                                                       | 65                          |

| B.1 lpffir                                                            | 65                          |

| B.2 pid                                                               | 66                          |

| B.3 aes                                                               | 66                          |

| B.4 aes192                                                            | 67                          |

| B.5 aes_ip                                                            | 68                          |

| B.6 ldpc                                                              | 68                          |

| B.7 jpegencode                                                        | 69                          |

|                                                                       | 5.5 Impact of Optimisations |

# **List of Figures**

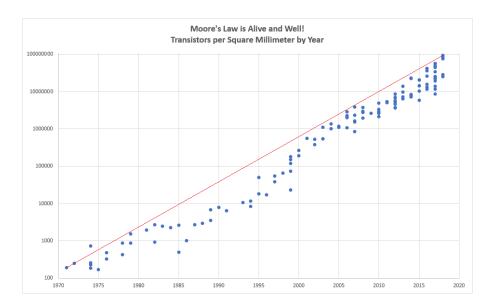

| 2.1        | Moore's Law from 1970 till 2020                                                                                                       | 8   |

|------------|---------------------------------------------------------------------------------------------------------------------------------------|-----|

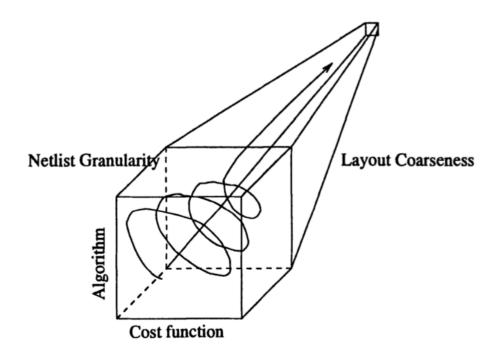

| 2.2        | Placement cube with four dimensions representing the placement ele-                                                                   |     |

|            | ments interaction                                                                                                                     | 9   |

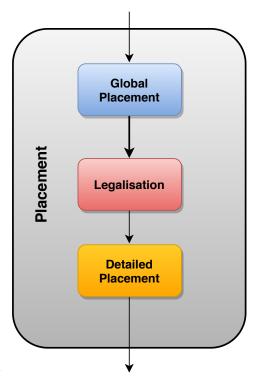

| 2.3        | Placement Flow Steps                                                                                                                  | 10  |

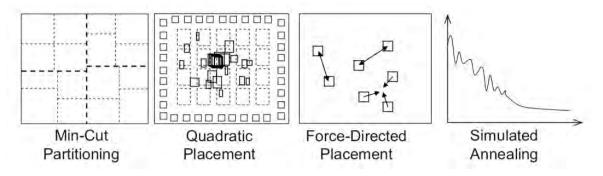

| <b>2.4</b> | Most common global placement techniques                                                                                               | 11  |

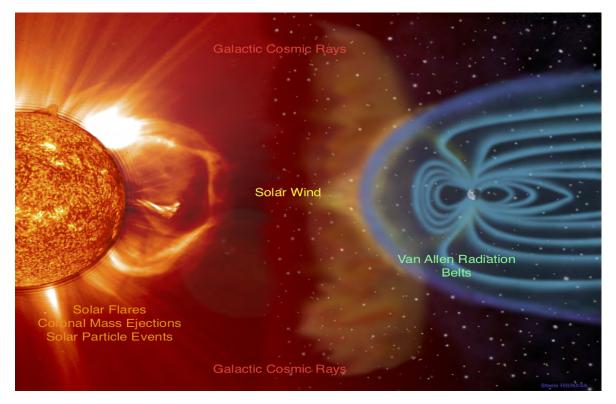

| 2.5        | Major radiation sources in space                                                                                                      | 13  |

| 2.6<br>2.7 | Displacement Damage occurs by an incoming radiation particle<br>The different masking mechanisms that can affect the propagation of a | 14  |

|            | transient fault                                                                                                                       | 16  |

| 2.8        | Two common system-level radiation hardening techniques                                                                                | 17  |

| 2.9        | Two widely device-level radiation hardening techniques                                                                                | 18  |

| 2.10       | OCommon circuit-level radiation hardening techniques                                                                                  | 18  |

|            | Standard Digital Design Flow                                                                                                          | 20  |

| 3.2        |                                                                                                                                       | 24  |

|            | Abax's supported cost functions                                                                                                       | 25  |

| 3.4        | SRA: Allows already legalised cells to be shifted into the subrows they                                                               |     |

| ~ -        | are assigned to                                                                                                                       | 26  |

| 3.5        | SRR: The legalisation of a cell can cause a cell wave to previous subrows                                                             |     |

|            | in order to maintain GP's cell order                                                                                                  | 26  |

| 3.6        | MRHC Legalisation Example: Initial Global Placement solution with                                                                     | ~ - |

| ~ -        | pre-placed blockages                                                                                                                  | 27  |

| 3.7        |                                                                                                                                       | 27  |

| 3.8        | MRHC Legalisation Example: Top-Down Subrow Scan                                                                                       | 28  |

| 4.1        | TMR Conversion of a sequential element                                                                                                | 30  |

| 4.2        | <b>j</b> , 8 8                                                                                                                        | 31  |

| 4.3        | Applying Minimum Spacing Constraint reduces the probability a parti-                                                                  |     |

|            | cle strike affect more than one TMR members                                                                                           | 32  |

|            | Radiation Hardening Legalisation Stages                                                                                               | 32  |

| 4.5        | Subrows Fill Cases                                                                                                                    | 34  |

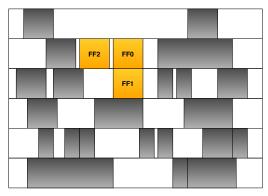

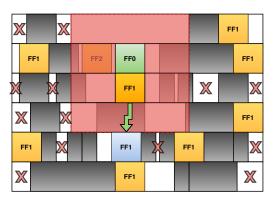

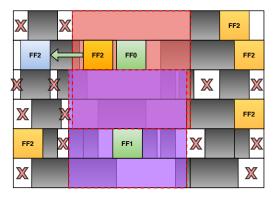

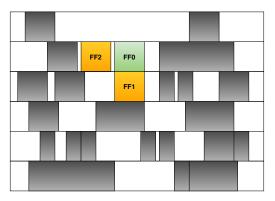

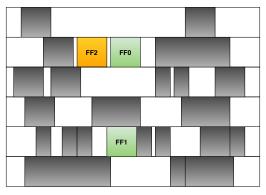

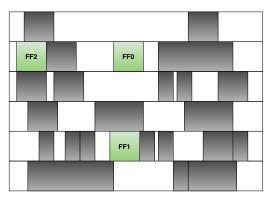

| 4.6        | TMR group legalisation mock-up example                                                                                                | 39  |

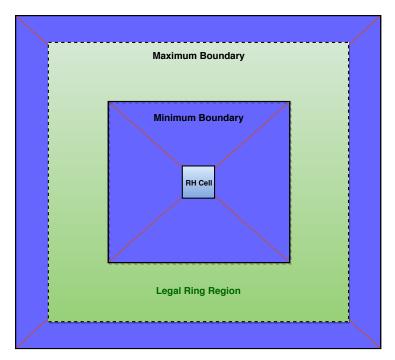

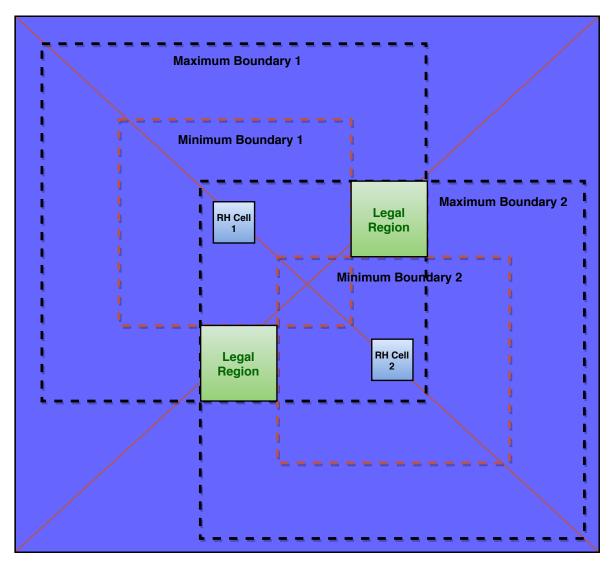

| 4.7        | Minimum and Maximum Spacing Constraints create a ring region legal                                                                    |     |

|            | for the legalisation of next member                                                                                                   | 40  |

| 4.8        | Multiple Cells Inflation: The final boundary is the union of the mini-                                                                |     |

|            | mum spacing constraints and the intersection of the maximum spacing                                                                   |     |

|            | constraints                                                                                                                           | 42  |

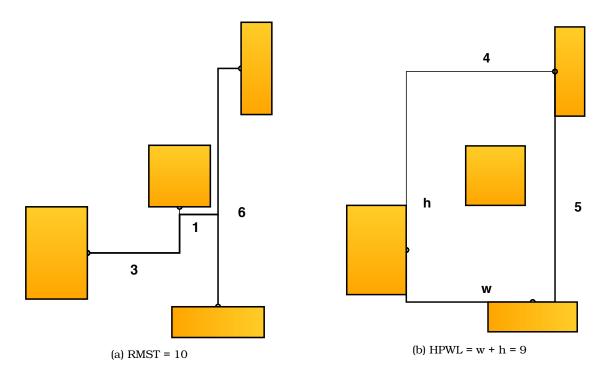

| 4.9        | 1                                                                                                                                     |     |

|            | Perimeter WireLength (HPWL)                                                                                                           | 44  |

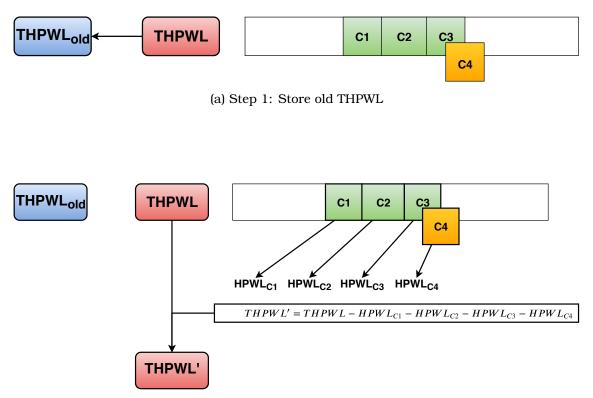

| 4.10 Steps of incremental THPWL update                                                                  | 45 |

|---------------------------------------------------------------------------------------------------------|----|

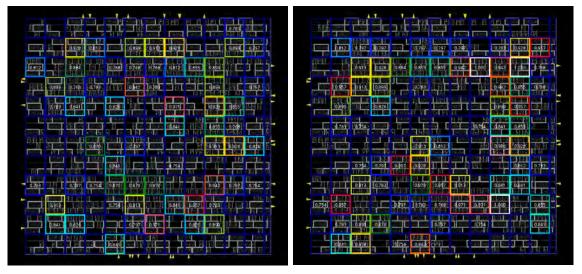

| 4.11 Density comparison between Displacement-driven and HPWL-driven                                     |    |

| RADHARD Legalisation                                                                                    | 47 |

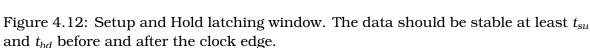

| 4.12 Setup and Hold latching window. The data should be stable at least $t_{su}$                        |    |

| and $t_{hd}$ before and after the clock edge. $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 48 |

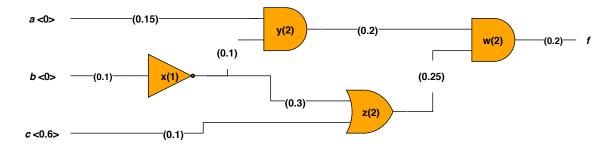

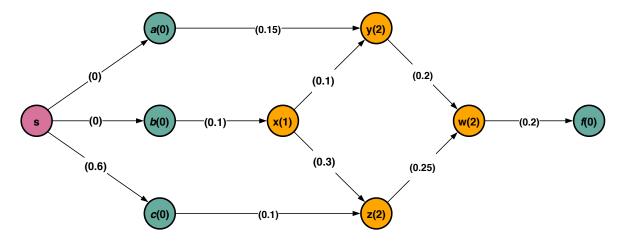

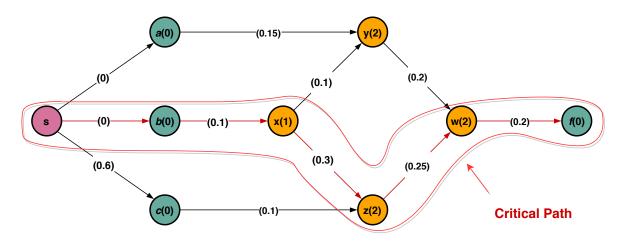

| 4.13Combinational logic circuit with three inputs a, b, c, annotated with                               |    |

| the times at which the signal transition occurs in brackets, and four                                   |    |

| logic gates, whose delays are presented in parentheses. Wire delays are                                 |    |

| also given in parentheses                                                                               | 49 |

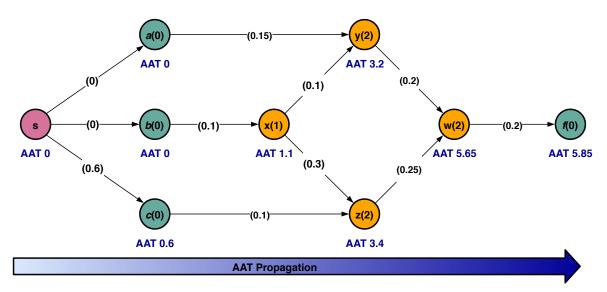

| 4.14 DAG representation of circuit in Fig. 4.13 using node convention                                   | 49 |

| 4.15 Forward propagation of actual arrival times (AATs) across the DAG for                              |    |

| each node                                                                                               | 50 |

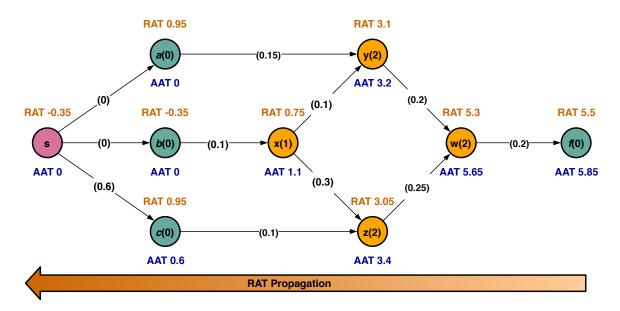

| 4.16Backward propagation of required arrival times (RATs) across the DAG                                |    |

| for each node                                                                                           | 51 |

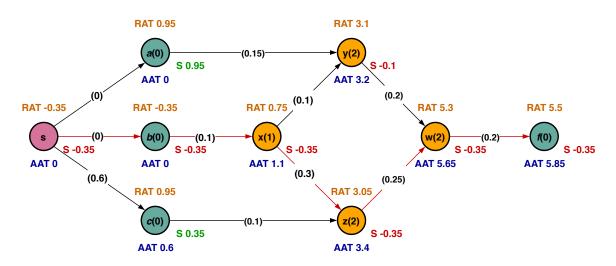

| 4.17 Slack computation for each node of the DAG using the Eq. 4.3 $\ldots$                              | 51 |

| 4.18The nodes with the worst negative slack form the critical path                                      | 52 |

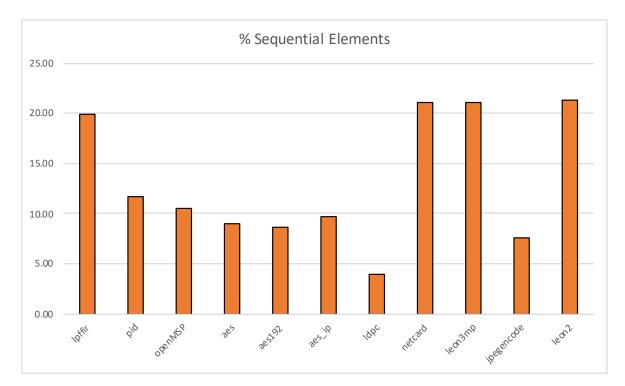

| 5.1 Percentage of sequential elements for each design                                                   | 54 |

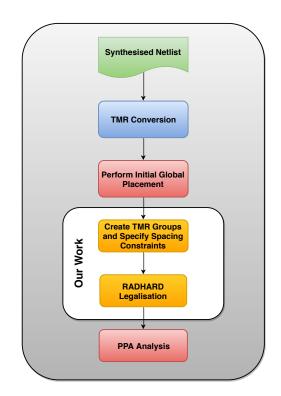

| 5.2 Experiments Flow                                                                                    | 54 |

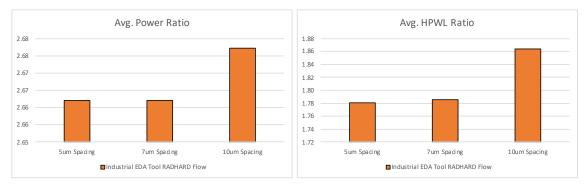

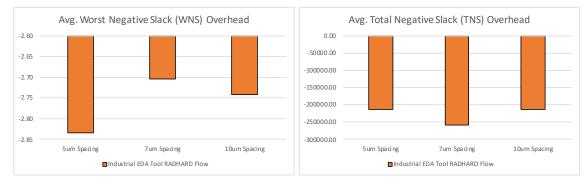

| 5.3 Impact of different spacing constraints in Power and HPWL: As the                                   | 01 |

| spacing constraint increases, both power and HPWL increase                                              | 56 |

| 5.4 Impact of different spacing constraints in WNS and TNS: No monotonic                                |    |

| behaviour                                                                                               | 56 |

| 5.5 Impact of Industrial RADHARD Legalisation in Power and HPWL: As                                     |    |

| the spacing constraint increases, both power and HPWL increase                                          | 58 |

| 5.6 Impact of Industrial RADHARD Legalisation in WNS and TNS: No mono-                                  |    |

| tonic behaviour                                                                                         | 58 |

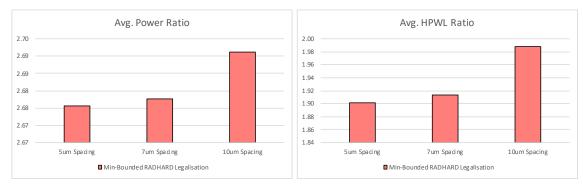

| 5.7 Min-bounded VS Industrial RADHARD Legalisation: Average Power and                                   |    |

| HPWL ratio                                                                                              | 59 |

| 5.8 Min-bounded VS Industrial RADHARD Legalisation: Average WNS and                                     |    |

| TNS overhead                                                                                            | 59 |

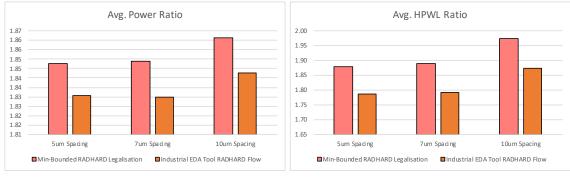

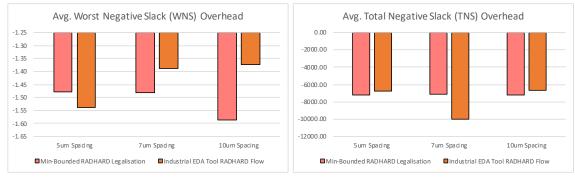

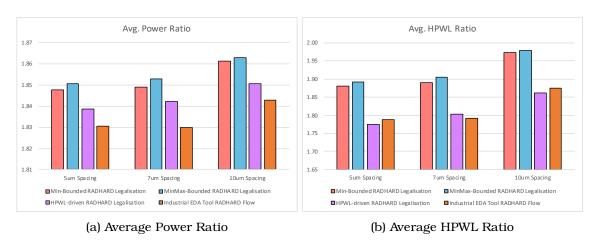

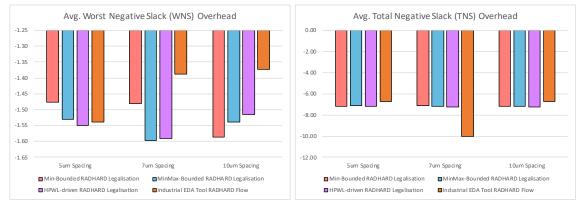

| 5.9 Impact of Optimisations on average Power and HPWL                                                   | 60 |

| 5.10 Impact of Optimisations on average WNS and TNS overhead                                            | 60 |

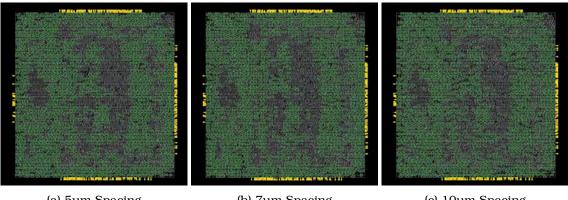

| B.1 lpffir: Non-RADHARD Legalisation Layout                                                             | 65 |

| B.2 lpffir: Min-bounded RADHARD Legalisation                                                            | 65 |

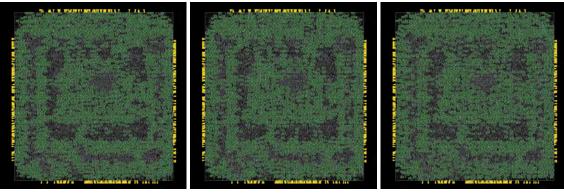

| B.3 pid: Non-RADHARD Legalisation Layout                                                                | 66 |

| B.4 pid: Min-bounded RADHARD Legalisation                                                               | 66 |

| B.5 aes: Non-RADHARD Legalisation Layout                                                                | 66 |

| B.6 aes: Min-bounded RADHARD Legalisation                                                               | 67 |

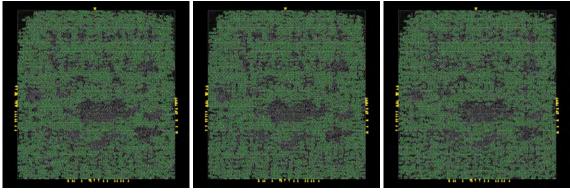

| B.7 aes192: Non-RADHARD Legalisation Layout                                                             | 67 |

| B.8 aes192: Min-bounded RADHARD Legalisation                                                            | 67 |

| B.9 aes_ip: Non-RADHARD Legalisation Layout                                                             | 68 |

| B.10aes_ip: Min-bounded RADHARD Legalisation                                                            | 68 |

| B.111dpc: Non-RADHARD Legalisation Layout                                                               | 68 |

| B.121dpc: Min-bounded RADHARD Legalisation                                                              | 69 |

| B.13 jpegencode: Non-RADHARD Legalisation Layout                                                        | 69 |

| B.14 jpegencode: Min-bounded RADHARD Legalisation                                                       | 69 |

| 8                                                                                                       |    |

# List of Algorithms

| 1 | RADHARD Legalisation Algorithm | 36 |

|---|--------------------------------|----|

| 2 | legalise_RH_cell()             | 36 |

| 3 | check_neighbouring_row()       | 37 |

## **Chapter 1**

## Introduction

Due to technology downscaling, the modern integrated circuits (ICs) have become more susceptible to errors caused by ionising radiation and radiation particle strikes. The effects of these faults can be destructive or not. In the first case, permanent damage is caused to the device, while in the second case, we can notice only a temporary malfunction of the circuit.

To increase the resistance of the circuits to errors caused by radiation, we have to apply a radiation-hardening method. There are various radiation-hardening techniques in the literature. These techniques perform changes either to the fabrication process of the circuit or to the design of the circuit.

The radiation-hardening design flow differs from the standard design flow. Thus, there is not sufficient support from the industrial Electronic-Design-Automation (EDA) tools.

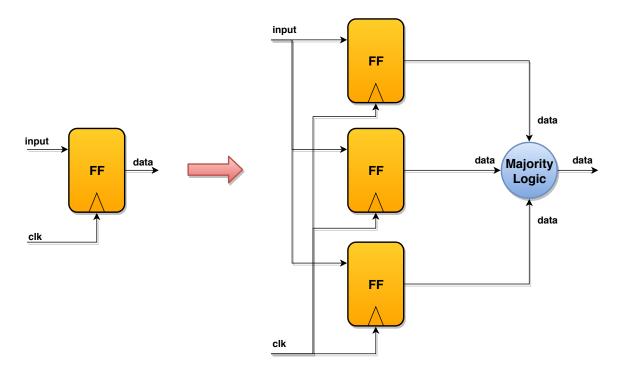

In our thesis, we present a Radiation-Hardening Legalisation Algorithm, utilising the technique of Triple-Modular (TMR) technique. In our approach, we triplicate each sequential element of the circuit and add a voter, which returns the majority of the three instances. Moreover, to reduce the probability of a particle strike affecting more than one member of the same TMR triplet, we apply a spacing constraint among them. A sufficient way to satisfy the spacing constraints is during the placement stage of the ICs design flow, and more specifically during the legalisation process. The most significant benefit of our approach is the freedom of using standard cell libraries instead of radiation-hardened, reducing the cost of fabrication.

In the first approach, our legalisation algorithm is displacement-driven, legalising each cell to its nearest legal position, satisfying at the same time the spacing constraints. Next step was the exploration of the effect of various optimisation techniques to the Power, Performance and Area (PPA) of the circuit. Specifically, we tried the following optimisation:

- Insert a bound avoiding Legaliser to place cells far away from the other members of the TMR triplet

- Place each cell to the position which leads to the minimum total wire length overhead

• Place the cells in a way it improves the timing of the circuit

Finally, to evaluate the quality of work, we compared our radiation-hardening legalisation approach with a flow of an industrial EDA tool, which supports spacing constraints among specified cells.

## **Chapter 2**

## **Theoretical Background**

### 2.1 Introduction to EDA

Integrated circuits (ICs) have contributed significantly towards the development of all the technological wonders that populate the world today. The ICs have found various applications from cars, televisions, computers, cell phones, music players to ship, aeroplane and spacecraft equipment. Integration density and performance of ICs have gone through an outstanding revolution in the last few decades. According to Moore's law, as shown in Fig. 2.1, integration complexity doubles approximately every 1 to 2 years. The above has led to ICs comprised of hundreds of millions of transistors. The design and the optimisation of ICs are essential to the production of new semiconductor chips. So the design process of very large-scale integrated (VLSI) circuits is highly complex and strongly depends on electronic design automation (EDA) tools.

Figure 2.1: Moore's Law from 1970 till 2020

The EDA industry develops such specialised software to support engineers in

the creation of new IC designs. The high complexity of modern ICs established EDA almost in all stages of ICs' design flow, from high-level system design to fabrication. That is, EDA tools are used to mostly automate design steps like logic design, simulation, physical design and verification. EDA tools have always targeted on automating the entire design process and linking the various design steps into a complete design flow. However, this integration is challenging since some design steps need additional freedom degrees, while scalability requires tackling some design steps independently. On the other hand, technology downscaling has made the boundaries of the different design steps fuzzy [1].

#### 2.1.1 Placement

Circuit placement is one of the most significant steps of EDA flow. After partitioning the circuit into finer modules and floorplanning the layout to determine block outlines and pin locations, placement consists of assigning a physical location to each standard cell or logic element with each block. The main objective of the placement process is to determine cells locations and orientations within a layout, specifying solution constraints and optimisation goals, such as wire length optimisations, timing optimisation, e.t.c [1]. Placement algorithms treat logic cells as rectangles and, in general, their size is not identical. So, the physical size of each cell must be known so that placement does not overlap cells in the layout. Some standard cell systems support the use of large array macros, such as RAMs. Although, the automated placement of these cells is challenging, and they might have to be placed manually [2].

Figure 2.2: Placement cube with four dimensions representing the placement elements interaction

Modern placement problem is very complex and involves several cost functions at the same time, such as cut, wire length, timing and congestion. As shown in Fig. 2.2, the placement problem consists of four essential elements: cost function, algorithm, netlist granularity and layout coarseness. Thus it is critical to discover a practical methodology which understands the interactions between these placement elements and picks the right combination at the right The placement process for largetime [2]. scale circuits, as shown in Fig. 2.3 is separated into three subsequent steps: global placement (GP), legalisation and detailed placement. Global placement emphasises on proper global cell positioning and overall density distribution, allowing at the same time cell overlaps or other constraint violations. These overlaps and violations are then resolved during the legalisation step, while detailed placement improves the quality of the legal placement performing local optimisations. Following we describe the different stages of the placement procedure [1].

Figure 2.3: Placement Flow Steps

#### **Global Placement**

Global placement is the first step of the placement process. It focuses on finding an initial placement of the logic cells. Global placement often ignores cells' specific shapes and sizes and does not attempt to align their location with valid grid rows and columns. Since it ignores the dimensions of the cells, it treats them as points allowing some overlaps among them. Performance optimisations can also take place during global placement. However, timing estimation can be inaccurate during the early stages of global placement. Also, other optimisations, such as total wire length, may restrict the placement algorithm from spreading the logic cells across the layout and achieving density distribution. Thus, it is more common to perform optimisations during the last stages of, or after, global placement. There are many placement algorithms used during global placement, with the most common of them to be shown in Fig. 2.4.

In partitioning-based algorithms, the netlist and the layout are divided into finer sub-netlists and sub-sections respectively, according to a cut-based cost function. It is an iterative process and is repeated until each sub-netlist and sub-section is small enough to be handled optimally. An example of this method is min-cut partitioning placement, which aims to minimise the number of cuts among each layout subsection.

Analytical placement algorithms minimise a given cost function, like total wire length or circuit delay, using mathematical techniques such as numerical analysis or linear programming. Such methods often require certain assumptions, such as to

Figure 2.4: Most common global placement techniques

know if the objective is convex or not or to treat the placeable cells as dimensionless points. Examples of analytic techniques include quadratic placement and forcedirected placement.

In stochastic algorithms, randomised moves are used to optimise the cost function. An example of this approach is simulated annealing. Simulated annealing is an iterative optimisation method that was inspired by the metal cooling process. The main objective is to achieve a better placement solution via a set of predefined moves and a cost function. A move that results in a better solution is always accepted regardless of the temperature. When a move leads to a worse solution, the algorithm depends on randomly accepting moves during the initial phases of the algorithm, where the temperature is high. As the algorithm proceeds, the temperature decreases and the algorithm accepts fewer worse moves. The acceptance of worse move is essential for the placement algorithm to be able to escape from local minimums of cost function and overall achieve the global optimum solution.

#### Legalisation

Global placement produces a placement solution trying to optimise a defined cost function. Since many of the placement techniques treat the placeable cells as dimensionless points, the global placement positions do not align with the power rails. Also, some overlaps among the cells may exist. Therefore, global placement must be legal. Legalisation seeks to align placeable cells with rows and columns and remove overlaps. During the overlap elimination, legalisation aims to minimise displacement from global placement locations as well as the impact on wire length and circuit delay. Legalisation step is necessary not only after global placement but also after incremental changes, such as cell resizing and buffering. Unlike global placement algorithms, legalisation requires the cells to be distributed enough across the layout region and have small overlap. From the above, it is noticeable that the legalisation process strongly depends on the initial global placement solution quality.

#### **Detailed Placement**

Once the legalisation solution is produced, it can be improved, during detailed placement, concerning a given objective. Detailed placement incrementally improves the location of each cell by local operations, such as swapping neighbouring cells to reduce total wire length, or shifting several cells in a row to create room for another object when whitespace is available.

### 2.2 RADHARD Background

Earth's atmosphere acts as a semipermeable filter allowing light and heat to get through while blocking most of the radiation existing in space. Outside the protective shield of Earth's atmosphere, there is a universe full of radiation. Space radiation is different from those experienced on Earth, such as X-rays or Gamma rays. It is comprised of atoms accelerated to speeds equivalent to the speed of light, causing their electrons to strip away and only their nucleus to remain [3].

Modern electronic circuits due to transistor downscaling became very sensitive to the radiative space environment. Some particle radiation is so energetic that it can penetrate the device and interact with its electronic circuit. This interaction can cause a wide variety of effects that range from the degradation of performance to functional disruptions affecting any system operations. Radiation effects, depending on their consequence to electronic circuits, are often divided into two general categories: Hard Errors and Soft Errors. Hard Errors cause permanent damage to the electronic device, while Soft Errors lead to a circuit malfunction without damaging it.

#### **2.2.1** Types of Radiation in Space

The radiation profile beyond Earth's atmosphere comprises of 4 major radiation sources:

- Galactic Cosmic Rays

- Solar Wind

- Van Allen Radiation Belts

- Solar Flares and Coronal Mass Ejections

Cosmic rays are a form of high-energy radiation, originating in outer space, that travels at nearly the speed of light and strike the Earth from random directions. These high-energy charged particles consist of mainly (89%) protons but also nuclei of helium (10%) and heavier nuclei (1%). Upon impact with the nuclei of atoms in the upper layers of Earth's atmosphere, cosmic rays can produce showers of secondary particles, mainly pions, that sometimes reach the surface [4].

The solar wind is a stream of charged particles released from the Sun's upper atmosphere, called corona. This plasma mainly consists of electrons, protons and alpha particle with kinetic energy between 0.5 and 10KeV. Its density and speed may vary over time and solar latitude and longitude [5].

A Van Allen radiation belt is a zone of radiation particles trapped by and held around Earth by its magnetic field. Earth has two such radiation belts, and sometimes others may temporarily be created. The belts trap mostly energetic electrons and protons, with other nuclei like alpha particles being less prevalent. The outer belt is made up of billions of high-energy particles that originate from the Solar Wind while the inner belt results from the interactions of cosmic with the Earth's atmosphere [6].

A Solar Flare is associated with the ejection of plasmas and particles from the solar corona into outer space. Powerful flares are often, but not always accompanied by a Coronal Mass Ejection, which is a significant release of plasma and magnetic field. The ejected plasma is released into the solar wind and the particles, associated with it, can penetrate the upper atmosphere [7].

Figure 2.5: Major radiation sources in space

### **2.2.2 Radiation Effects in electronics**

The rapid evolution in the field of VLSI technology over the past decades has brought the emergence of Integrated Circuits (ICs) that operate at high frequencies and with low power requirements. Although modern chips become more and more efficient, their susceptibility to cosmic radiation, due to the reduction in device feature sizes and supply voltage, constitutes a constant concern. A charged particle can strike the electronic device and cause non-destructive or destructive effects depending on the particle's energy, type and the strike location. The radiation effects in microelectronics can be divided into two general categories: the Cumulative Effects and the Single-Event Effects (SEEs).

Cumulative effects are long-term effects and produce gradual changes in the operational parameters of the device. They require the device to operate under continuous levels of radiation before device malfunction becomes obvious. The most major cumulative effects in electronics are Total Ionising Dose (TID) and Displacement Damage (DD):

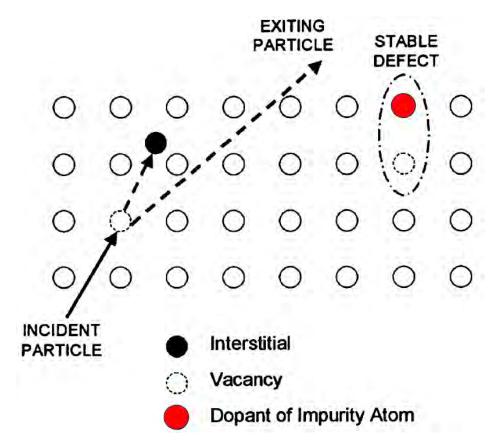

Figure 2.6: Displacement Damage occurs by an incoming radiation particle

- **Total Ionising Dose (TID)** effects occur when electrons and protons create an excess charge in the dielectric layers used for electronic devices' insulation. Extended exposure of a device to TID radiation can shift the threshold voltages, making transistors easier or harder to alternate. It can also increase leakage current, causing the on and off states of the transistors to become less distinguishable.

- **Displacement Damage (DD)** is the result of nuclear interactions, typically scattering, which cause lattice defects. The collision between an incoming radiative particle and a lattice atom subsequently displaces the latter from its original lattice position creating the same time a vacancy, as shown in Fig. 2.6. Displacement Damage is caused by long-term non-ionising damage from protons of all energies, high-energy electrons (above 150KeV) and neutrons. However, Displacement Damage is not such a major effect as Total Ionising Dose or Single-Event Effects.

Both of the above cumulative radiation effects are hard errors since they cause permanent damage to the electronic device, but they cause it long term.

Other significant effects caused by radiative particles are the Single-Event Effects (SEEs). As an event is called a particle strike caused in an electronic device. SEEs cause instantaneous changes or transient behaviour in circuits, leading to erroneous performance. They are classified into two types of errors: Hard Errors and Soft Errors. Hard errors are a type of errors causing permanent damage to the device, and most of the time to memory chips.

On the other hand, soft errors are events in which data are corrupted, but the device itself is not permanently damaged. Soft errors can affect a device in different ways. In some cases, they may result in data corruption, detectable or not, at the system level, while in other cases, they can cause a circuit's malfunctioning or even a system crash.

Soft errors can be classified into the following categories:

- **Single-Event Transient (SET)**: The event causes a voltage in the circuit's logic, which becomes a bit error when captured in a storage element. In case a particle strike hit more than one combinational elements of the circuit, the fault caused is called **Single-Event Multiple-Transient (SEMT)**.

- Single-Event Upset (SEU): The particle strike affects node's charge and causes a logical upset in sequential elements of the circuit. When the event causes a bit-flip (upset) in a memory cell or a latch, it is called **Single-Bit Upset (SBU)**. Mainly, using the term SEU, we are referring to SBU. When the particle strike causes the upset of two or more bit in the same word, the upset is called **Multiple-Bit Upset (MBU)**. Finally, when the event causes the upset of two or more sequential elements, it is called **Multiple-Cell Upset (MCU)**.

- **Single-Event Functional Interrupt (SEFI)**: The event causes loss of functionality due to the perturbation of control circuits, like state machines, placing the device into an undefined state.

- **Single-Event Latchup (SEL)**: The particle strike causes loss of device functionality due to a single-event induced current state. A SEL may cause permanent damage to the device, in which case the result is a hard error. The SEL results in high operating current, above device specifications. The latched condition can destroy the device, drag down the bus voltage, or damage the power supply.

- **Single-Event induced Burnout (SEB)**: It can cause the device's destruction due to a high current state in a power transistor, resulting in a permanent device failure (hard error).

The failure rate of a device induced by soft errors is called Soft Error Rate (SER). SER usually is measured for a given environment in FIT units (Failures In Time), where 1FIT denotes one failure per billion device operation hours. Typical SER values for electronic devices can range between 100 and 100000FIT, *i.e.* one soft error per year. The FIT value is either predicted by simulation or is the result of a series of experimental error measurements. SER monitoring shows that the hard error failure rate, due to external events, such as electrical latchup, is at maximum 10FIT, but commonly is much less. For the modern process technologies, the SER of 1Mbit of SRAM, one of the most susceptible components to soft errors, is in the order of 1000FIT. Depending on the number of Mbits of SRAM in a device, the above SER can be escalated enough, in a way, that for a device containing multiple Mbits of SRAM it can be higher than the total failure rate due to all other mechanisms.

The occurrences of random particle strikes are distributed fairly uniformly in space and time. The probability of a particle strike in a circuit node is thus roughly proportional to its active area. Each particle strike is not able to cause a transient fault (TF) in a circuit node. The particle strike affects a circuit's node only in the

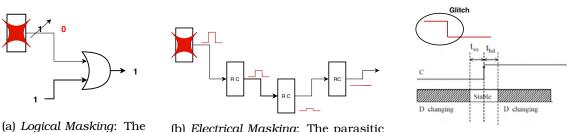

case it causes a charge which is greater than a critical charge ( $Q_{crit}$ ), specific for each circuit node. The characteristics of a transient pulse at a node strongly depend on the incident particle's energy distribution and node's  $Q_{crit}$ . However, various masking mechanisms determine whether a transient pulse will propagate to primary outputs, latches or flip-flops (*fault catching points*) and cause a soft error or not. The three major masking mechanisms, Fig. 2.7, are the following:

- **Logical Masking**: occurs when there is no sensitised path from the incident node to any of the *fault catching points*. This phenomenon appears when a transient fault arrives at an input of a subsequent cell, which prevents its propagation because at least one of the other cell's input is at a controlling logic value. For example, the controlling value of an AND gate is logic 0, whereas logic 1 is the controlling value of an OR gate.

- **Electrical Masking**: occurs due to transient pulse's width attenuation in a sensitised path from its occurrence node to any of the *fault catching points* until it is eliminated. Thus, electrical masking strongly depends on the electrical properties of the gates in the sensitised path.

- **Timing-window Masking**: occurs when the transient pulse, even though logical and electrical masking did not prevent its propagation to fault catching points, it does not cause a soft error because its arrival point is sufficiently separated in time from the arrival of clock edge. Parameters which determine the occurrence of the timing masking include the arrival time of the pulse at a sequential element, as well as its SETUP and HOLD times. The last two variables define its latching window, during which the sequential element samples its inputs. As the transient pulse is momentary, if the fault arrives outside the latching window, it is masked and does not cause a soft error.

The above masking mechanisms thus lead various circuit nodes to be quite different in their soft errors susceptibility.

(b) *Electrical Masking*: The parasitic capacitance and resistance of the following gates in the sensitised path attenuate the particle strike's glitch

OR gate does not let the

fault to propagate since

it is in its controlling

value

(c) *Timing-window Masking*: The fault arrives at the FF outside the [SETUP HOLD] window, during which the FF catches the input data

Figure 2.7: The different masking mechanisms that can affect the propagation of a transient fault

### 2.2.3 Radiation Hardening Techniques

Radiation Hardening is the process of making electronic components and circuits resistant to damage or malfunction caused by ionising radiation [8]. The radiation hardening techniques can be applied at different levels and categorised as

- System-level techniques

- Device-level techniques

- Circuit-level techniques

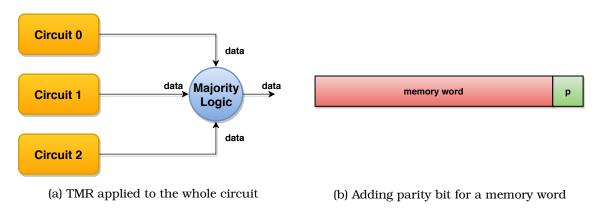

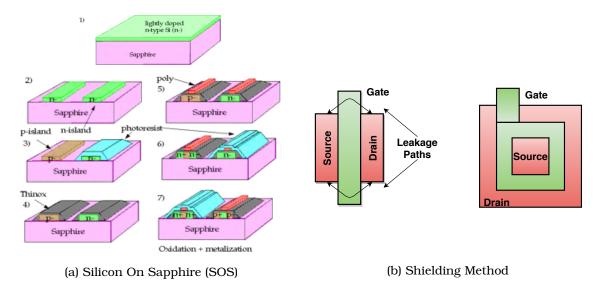

Figure 2.8: Two common system-level radiation hardening techniques

System-level hardening techniques aim to achieve error detection/tolerance ability in the design. To accomplish that, system designers mainly apply redundancy techniques, with the most common one, the Triple-Modular Redundancy (TMR). In TMR technique the whole circuit is replicated three times, and a majority voter is added to filter the corrupted value propagated by one of the TMR replicas, Fig. 2.8a. For memory circuits, the system-level hardening technique is applied by adding a parity bit to the memory word, Fig. 2.8b. Each time a word is written to the memory, a parity bit is generated and appended to the data. Upon data retrieval, the parity of the obtained data is calculated, and a check compares the later one with the stored parity bit. In case a single error has occurred, the data parity won't match with the parity bit. In that case, an additional circuit is needed to correct the data. Although there are various methods to correct the errors, like hamming codes, their use may result in significant area and power overhead. Even though a single error can be detected, the parity check is not able to reveal a double fault because the data parity will match with the parity bit.

Figure 2.9: Two widely device-level radiation hardening techniques

Device-level hardening techniques aim to reduce and mitigate the charge collection at the region of the particle strike. These methods require a change to the fabrication process. One technique is to manufacture the chips on insulating substrates instead of the known semiconductor wafers. Silicon-On-Insulator (SOI) and Silicon-On-Sapphire (SOS), Fig. 2.9a, are assumed to provide radiation-hardened chips. Another device-level hardening technique is either the shielding of the entire package against radiation, to reduce the exposure of the device, Fig. 2.9b. Although these methods protect the devices against radiation sufficiently, they increase a lot the fabrication cost.

Figure 2.10: Common circuit-level radiation hardening techniques

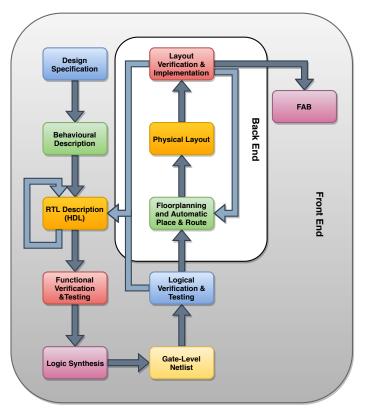

Circuit-level hardening techniques focus on changing the circuit design to achieve SEEs mitigation. Typically, circuit-level mitigation techniques must either filter or dissipate the collected charge or provide some form of redundancy to prevent the corrupted data propagation. A method to reduce the soft error rate is to increase the node capacitance, Fig. 2.10a. A particle strike can cause a fault only if the produced charge is larger than the node's critical-charge, which is defined as  $Q_{crit} = C_{node} * V_{DD}/2$ . From the above equation, we can see than increasing the node capacitance can make the specific node more resistant to radiation. To achieve the above, we can either add a capacitor or increase the wire length of the node connectivity. Although, this method imposes a significant area and power penalty due to the added capacitor. Spatial redundancy techniques such as TMR triplicate the critical circuit/cell and add a majority voter to filter the transient fault, as shown in Fig. 2.10b. TMR can mask a single error happening among the three logic replicas. This fault can be masked thanks to the existence of the other two TMR instances. However, this method results in a large area overhead due to triplication.

## **Chapter 3**

## **Existing Works**

### **3.1** Existing Works in the Literature

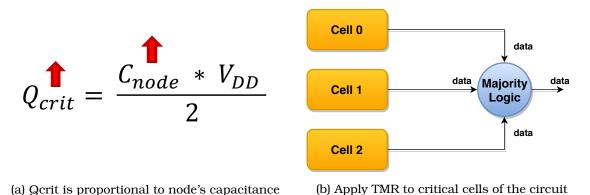

The IC design flow for harsh environment differs from standard digital design flow. The latter one is shown in Fig. 3.1. Mainly, space applications impose additional requirements on the designs and tools. The main challenges are related to the resistance to the ageing and radiation effects, where the latter includes Total Ionising Dose (TID) and Single-Event Effects (SEEs).

The ageing of transistors and TID effects result in similar outer effects, such as increased leakage and reduced performance. As mentioned in Chapter 2.2.2, TID effects are caused after prolonged exposure of a device to electrons and protons, creating an excess charge in its dielectric insulation layers. On the other hand, SEEs are generally induced by a particle hit on the die surface. They can be observed as Single-Event Transients (SETs), in case of temporary value change of the Boolean gates, Single-Event Upsets (SEUs), in case of a bit-flip of the register, or even destructive, such as Single-Event Latchup (SEL), in case of induced short in the circuit due to the temporary forming of parasitic bipolar structures or Single-Event Burnout (SEB), in case a power transistor is affected.

Various radiation hardening methods have been proposed in the literature to mitigate those effects. Most of them take place in physical and device level,

Figure 3.1: Standard Digital Design Flow

while others in the circuit level, and more specifically in placement stage. On the

other hand, in industrial EDA tools, there is no significant contribution to radiation hardening. Although, one of the most robust EDA tools, supports a radiation hardening flow during the placement phase.

#### **3.1.1 Radiation Hardening in the Literature**

Many works exist in the literature proposing methods to mitigate radiating effects. The methods to address those effects are mainly on the layout level, such as the use of Enclosed Layout Transistors (ELT) against TID effects [9]. Considering SEEs, the SELs could be addressed by the technology, *i.e.* Silicon-On-Insulator (SOI) or Silicon-On-Sapphire (SOS), which are immune in this effect, or careful contacting and introduction of guard rings [10].

For the radiation hardening against SETs and SEUs, different methods could be used. One significant method includes the transistors up-sizing, *i.e.* increase in the relation between width and length of used transistors [11]. Nevertheless, this method is also quite expensive in terms of area, performance and power consumption. The alternative is the use of specific flip-flop architectures that are tolerant against SEUs. An example of such architecture includes the use of Dual-Interlocked CEll (DICE) architecture, where the storing structure of the latch has been made as a ring of 4 inverter pairs [12]. In this case, if one node is affected by the particle hit the other three nodes will keep the latch stable. This structure has also been further improved to LEAP-DICE [13] by taking into consideration the layout effects. Similar approaches have been provided in the know DARE library with Heavy Ion Tolerant storage cell (HIT) architecture [14]. Such radiation-tolerant latches are usually extended with some glitch filter at the data input, to accommodate the SETs efficiently.

With transistor scaling it is very difficult to implement the capable radiationtolerant architecture of the flip-flop. The small transistor dimensions, reduced critical charges ( $Q_{CR}$ ) and high integration lead to the increased susceptibility to the SEUs. As a consequence, at the higher Linear Energy Transfer (LETs) there is a high probability that more than one nodes of the latch will be affected by the particle hit. In this case, increasing the distance between the transistors is not such an efficient measure since it is leading to performance drop and unnecessary cell size increase.

Meanwhile, the reduction of Soft Error Rate (SER) can also be achieved by selectively optimising wire length for soft error critical nets. The larger the wire lengths for nets can act as larger RC ladders and can efficiently filter out the transient glitches cause by particle strikes. Based on the above, in [15] a simulated annealing placement algorithm is proposed, aiming to reduce the SER of logic circuits. The SER capture is based on the *logical observability* metric, which is inversely proportional to each node's logical masking effect. So, nodes with lower logical masking ability have high logical observability, since a fault caused in these node has a substantial probability of being captured at a sequential element. As mentioned in Chapter 2.1.1 simulated annealing is a placement algorithm inspired by the metal cooling process, and the acceptance of a move depends on the current temperature. In this work, the cost of simulated annealing is the summation of the logical observability weighted with the wire length of each net, while taking into account at the same time total area and wire length constraints. Considering that, soft error critical nets are assigned longer wire length for glitches filtering, while delay critical nets are assigned shorter wire length for minimising circuit delay. Although, simulated annealing placement algorithms are not sufficient because they strongly depend on their global variables, *i.e.* temperature, initialisation.

As a consequence, it would be better to apply some radiation hardening method at the RTL level. The principles of N-Modular Redundancy (NMR), and especially Triple-Modular Redundancy (TMR) have been used in the space applications for years. In TMR, the fault tolerance is achieved by triplication of the original module, and the single fault can be filtered out through a majority voting [16]. As for addressing SEUs, TMR method could be applied at the level of flip-flops, where single unprotected flip-flop can be replaced by a fault-tolerant structure, including three replicas of the original flip-flop and a majority voter. Regarding addressing SETs, two strategies are possible:

- 1. generation of three clock trees with a timing offset between them, or

- 2. adding a temporal filter at the input of TMR-structure

The latter is of significantly lower complexity and area cost. TMR approach has higher potential for the radiation hardness compared to the flip-flop architectural approaches. It is more unlikely that a single particle can influence at the same time two flip-flops that are in some distance to each other. As for the TMR approach to be reliable, it is imperative to guarantee that the FFs of each TMR structure are at a minimum distance from each other so that they are not going to be affected by a single particle hit. This strategy has been shown to provide excellent radiation tolerance. In case a SET is caused in combinational logic near active clock edge, the fault can be propagated to the TMR FF triplet resulting in SEU. In this case, the SETs can be masked using different delay elements in data input among the TMR triplicated FFs [17]. Thus, it is more worthwhile to aim to the SEUs mitigation instead of SETs.

### 3.1.2 Industry Approach

As mentioned in the previous section, to achieve radiation hardness in the circuit, we have to modify the standard design flow. Modern standard CAD tools are trying to optimise and reduce the routing distance between the connected standard cells aiming to achieve better area, power and performance. To accomplish that, for most of the industrial tools is impossible to add custom constraints into their cost function and thus are unable to achieve fault mitigation. However, an existed robust industrial CAD tool started to support spacing constraints among cells in its newer version, which can be utilised for radiation hardening. Specifically, it supports commands to create spacing groups and set the spacing constraints to be applied both in x-axis and y-axis.

After creating the spacing groups and setting their spacing constraints, the tool's placer is enforced to take into consideration any specified spacing constraints. To ensure that a particle strike will not affect more than one of the specified instances, it places each member of a group into a position with a minimum distance from the other members, at least as much the spacing constraint specifies, both horizontally

and vertically. Nevertheless, this approach leads to spread the critical cells further apart, possibly affecting the area, power and circuit delay. On the other hand, ensuring that the Euclidean distance among the TMR members is greater than or equal to the specified spacing constraint is a suitable alternative approach. The latter not only guarantees that a single particle strike will not affect multiple critical cells but also doesn't affect the Power-Performance-Area (PPA) results significantly.

### 3.2 Thesis' Used Tool

The freedom of using existing standard cell libraries make the radiation hardening during the placement stage of ICs' design flow very appealing. The radiation hardening process can be applied during the legalisation process. As mentioned before, legalisation aims to eliminate any circuit's violations removing cells' overlaps and aligning them to grids. Thus, in addition to these legalisation rules, we can introduce a constraint which aims to radiation hardening.

Our goal is to render the designs resistant to radiation maintaining as much as possible the original design's solution. Various legalisation algorithms are proposed in the literature, aiming to minimise the impact of legalisation as much as possible. The existing algorithms can be categorised to (i) global approaches, where multiple cells are legalised simultaneously, and (ii) local, where cells are legalised one at a time [18]. In the former case, legalisation approaches aim to exploit the global view of the cells' positions and legalise them into positions finding the global optima. In the latter case, cells are legalised trying to place each one into its best available location. Local Legalisers, such as Tetris [19] and Abacus [20], legalise cells one-by-one trying to find their optimal position in a greedy way. Mainly, Tetris handles mixed cells, *i.e.* standard cells and macroblocks, and greedily assigns each cell to its nearest legal position, respecting at the same time the row capacity, and fixes it before continuing with the next cell. However, Tetris has several drawbacks [1], with the most crucial being that (i) it doesn't maintain the cells' relative GP order leading to higher total displacement and wire length, and (ii) fixing each legalised cell into its new positions it subsequently preserves large amounts of whitespace.

These main drawbacks are solved by other improved approaches based on Tetris, like Abacus. The latter legalises only standard cells with the same height and different width, in contrast with Tetris, trying to minimise their displacement from their GP positions. In contrast to Tetris, Abacus, to achieve the minimum displacement, allows already legalised cells to be shifted through its placement row trying to minimise the total cells' displacement maintaining at the same time their GP cell order. A drawback of Abacus legaliser is the fact that supports only standard same-height cells. A variation of Abacus legaliser, called Abax [21,22], extended Abacus to support mixed height cells and also handles blockages. Thus, Abax used in our work, since it is a suitable legaliser trying to minimise the impact of legalisation to GP solution. In the next section, Abax is presented in more details.

#### 3.2.1 Abax Legaliser

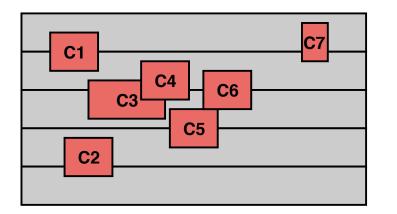

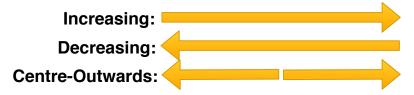

Abax is a modification of the classical Abacus Legaliser. It is a sequential legaliser, legalising one cell at a time in legal positions in a specified order. Cell order, according to the goal of the legalisation, depends on various factors, like the cell's initial GP position, cell's area or even the influence of the cells on the circuit's timing. Abax is a greedy displacement-driven legaliser aiming to minimise the influence of legalisation on the GP solution. To achieve this goal, Abax assigns each cell to its nearest row, that fits in, achieving minimum displacement from its GP position. In this way, cells are sorted either by the cell's GP x-coordinate or the cell's area. Thus, Abax supports three cell orders, *i.e.* (i) increasing, (ii) decreasing, and (iii) centre-outwards orders.

Sorted List by x-coordinate: { C1, C2, C3, C4, C5, C6, C7 }

Figure 3.2: Abax's supported cell orderings

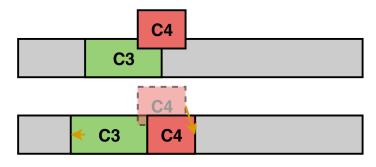

As mentioned, Abacus, and subsequently Abax, tries to minimise the cells' displacement from their initial GP positions. Thus, the chosen legal position of each cell is based on its displacement cost. One modification of Abax Legaliser is associated with the cost function evaluating each cell's tentative move. Abax supports Abacus' single-cell displacement cost function. However, this cost function has a local overview of the legalisation effect on GP's solution, since it considers only the displacement of the current legalising cell. Thus, Abax introduces two additional cost functions, the (i) multi-cell total displacement cost function, and (ii) multi-cell mean displacement cost function. The legalisation of a cell can cause the displacement of already legalised adjacent cells. Thus, multi-cell total displacement takes into account the total displacement of all moved cells during this tentative move, while the multi-cell mean displacement cost function takes into account the average displacement of the moved cells. Thus, these two cost functions have a global overview of the legalisation influence in GP solution.

$$C_{single} = D_{C4} \qquad \qquad C_{total} = D_{C4} + D_{C3}$$

$$C_{mean} = \frac{D_{C4} + D_{C3}}{2}$$

Figure 3.3: Abax's supported cost functions

Abax legalises each cell, by checking first the displacement cost assigning it to its nearest row and then examines a set of rows above and below the nearest row, which reside inside a row search bound. The latter is decreased each time a new best cost is found. Although the row search bound reduces the number of examined legal positions avoiding legaliser to check all the core rows exhaustively, it ensures that it does not influence the quality of the solution.

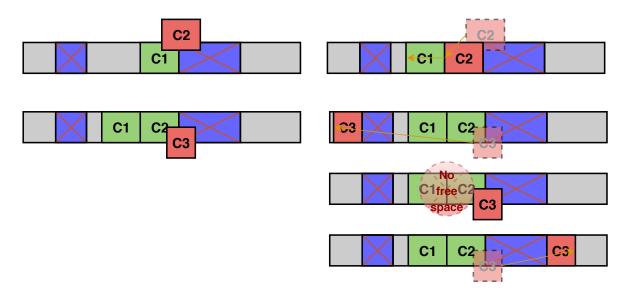

Another important feature of Abax legaliser is the handling of hard macros and blockages. The placement of the latter divides the core rows into a set of row segments, called subrows. Its starting x-coordinate and its width determine each subrow. Thus, the legalisation of each cell depends on the available subrows that the corresponding cell fits in. Abax supports two approaches for handling hard macros and blockages:

- **Sub-Row Assignment (SRA**): This approach, Fig. 3.4 as originally proposed in the Abacus, preserves the initial GP's cell order only within the boundaries of each subrow. After a cell is legalised in a subrow, it can be shifted inside the current subrow. However, moving cells to adjacent subrows are not allowed.

- **Sub-Row Re-assignment (SRR)**: This is an alternative approach of handling macros and blockages. In contrast to SRA, SRR allows moving cells to adjacent subrows, Fig. 3.5. When placing a cell into a subrow causes a subrow overflow, some cells are shifted to adjacent subrows to be able to place the current cell into this subrow. This way, SRR preserves GP's global cell order.

Figure 3.4: SRA: Allows already legalised cells to be shifted into the subrows they are assigned to

Figure 3.5: *SRR*: The legalisation of a cell can cause a cell wave to previous subrows in order to maintain GP's cell order

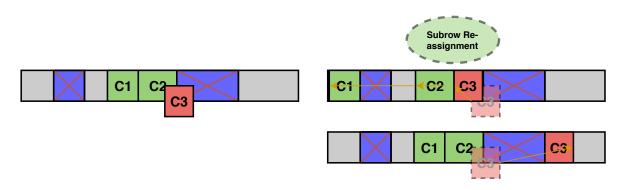

Moreover, Abax extended Abacus also to support cells with different heights, *i.e.* Multi-Row-Height-Cells (MRHCs). The height of MRHCs must be an integral multiple of row height. Since the size of MRHCs is larger than the size of Single-Row-Height-Cells (SRHCs), the impact of their legalisation to metrics, such as Total Wirelength (TWL), is much larger. So the MRHCs must be legalised in a way the influence to TWL to be minimised. Abax supports MRHCs legalisation implementing a Tetris-like algorithm, by fixing MRHCs to the legal position with the minimum displacement from the GP position and they can not move again during the legalisation procedure. The MRHC legalisation approach will be presented with a contrived example.

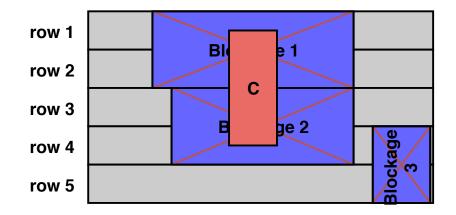

The algorithm starts with an initial placement produced during Global Placement with blockages already placed, as shown in Fig. 3.6. The algorithm finds for each cell the legal position with the minimum displacement finding the corresponding subrows by scanning the core area into two opposite directions, *i.e.* bottom-up and top-down.

Figure 3.6: MRHC Legalisation Example: Initial Global Placement solution with pre-placed blockages

First, Abax searches the subrows in the bottom-up direction. In this phase, the algorithm finds the nearest subrow considering the lowest y-coordinate of the MRHC. Then, considering the new x-coordinate of the cell, the algorithm checks from the current subrow to the height of MRHC, if the cell doesn't cause any overlap with preplaced blockages or MRHCs. For example, in Fig. 3.7, the nearest subrow from the bottom of cell *C* is in row 4 and on the left of *Blockage 2*. Starting from this subrow, the algorithm checks if placing *C* into this subrow causes any overlap to the above rows. In case a legal position is found, the displacement cost is determined.

Figure 3.7: MRHC Legalisation Example: Bottom-Up Subrow Scan

However, the bottom-up scan is not enough to find the position with the minimum displacement from the original location. So, then the algorithm continues with the top-down scanning direction. The combination of bottom-up and top-down scans gives the whole set of legal positions. In Fig. 3.8 the top-down scanning phase is presented, starting from the nearest subrow of the upper y-coordinate and scans the rest subrows the same way as in bottom-up, but in the opposite direction.

Figure 3.8: MRHC Legalisation Example: Top-Down Subrow Scan

Finally, the entire set of the legal positions for the MRHC is retrieved with their displacement from the initial GP position. Since the algorithm legalises the cell into the position with the minimum displacement, it places the cell into the subrow with the minimum displacement cost from the above set of legal positions. The lowest left figure in Fig. 3.8 highlights the position the cell *C* is finally legalised.

After the legalisation of MRHCs, the latter become fixed into their updated legal positions, to avoid any overlaps being caused during the next step, *i.e.* SRHCs legalisation.

All the above characteristics of Abax Legaliser, make the latter a suitable legalisation algorithm able to be modified to support RADHARD cells, by applying a minimum spacing constraint among the TMR triplet members. Mainly, MRHCs legalisation and blockages handling are two Abax's features that are utilised to achieve the spacing constraints satisfaction. In the next chapter, we are presenting the way the above two features are used to satisfy the spacing constraints.

## **Chapter 4**

## **RADHARD** Legalisation

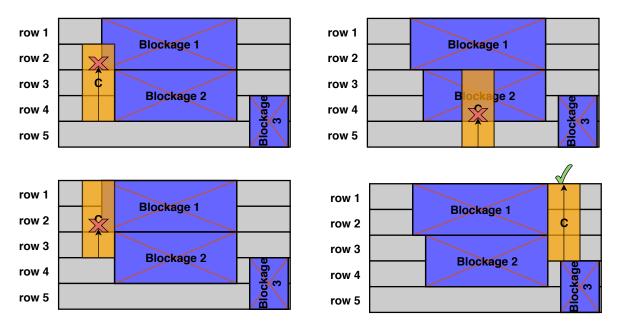

Modern electronic circuits due to technology shrinking became very sensitive to radiation, leading to apply radiation hardening techniques to mitigation radiation effects. In our work, we focus on the mitigation of SEUs, converting each sequential element to TMR structures and applying a spacing constraint to reduce the probability a particle strike affecting more than one members of the TMR triplet. An efficient way to satisfy the spacing constraint is during the placement stage of the ICs design flow and specifically during the legalisation process. Thus, in our work, we implemented a Radiation-Hardening (RADHARD) Legalisation algorithm, developing four approaches to achieve better PPA results. The first approach was to extend Abax to support RADHARD cells satisfying their minimum spacing constraint. However, legalisation strongly depends on the GP solution, which can place cells of the same TMR triplet far away. To improve the results, we also supported a maximum spacing constraint forcing legaliser to place the triplet cells inside a region. However, a more efficient way to achieve better results is by modifying Abax to consider the total wire length during the evaluation of each cell's move. Finally, another approach which can have a significant impact on PPA results is taking into account the slack during the legalisation of each cell. The rest of this chapter describes in more details the above approaches we followed during the implementation of our RADHARD Legalisation Algorithm.

## 4.1 Min-bounded RADHARD Legalisation

The technology shrinking the last few years leads electronic devices to be more and more susceptible to SEUs. The small transistor dimensions and the reduced critical charges result in a higher probability that a sequential element will be affected by a particle strike. To alleviate this problem, we used a widely used technique called N-Modular Redundancy (NMR). NMR is a hardware redundancy method which uses N replicas of the same module and a majority voter which compares the outputs of the N replicas and outputs the correct value.

In general, NMR technique can mask at most (N - 1)/2 faults happening at the same time to some of the replicas, since the remaining unaffected NMR instances can mask them. The higher the grade of NMR, the higher the module is protected against transient faults, although the higher negative impact on the area, power and timing

of the circuit. There is a tradeoff between Quality-of-Results (QoR) and the circuit resistance to transient faults. So, in most practical applications, a commonly used grade of redundancy is Triple-Modular-Redundancy (TMR). TMR is a redundancy method with the lowest impact on PPA and can mask a single fault happening among the triplet members.

In TMR, fault tolerance is achieved by triplication of the original module and usage of a two out of three majority voting, referred to as *TMR structure* for the rest of the thesis. For Single-Event Upsets (SEUs), this method may be applied at the FF level, replacing the original ones by the triplet and the voter. For SETs, two approaches are possible, using three, separate clock trees, with timing offset between them, or adding a temporal filter at the TMR circuit section. The latter is of significantly lower complexity and area cost. As for the TMR approach to be reliable, it is imperative to guarantee that the FFs of each TMR structure are placed at a minimum distance from each other so that they are not going to be affected by a particle strike.

In this work, we propose a TMR Radiation Hardening (RADHARD) methodology, including a custom Post-Placement Legalisation algorithm, able to satisfy userspecific, minimum distances among the FFs of each TMR structure. Our algorithm is fully compatible with industrial EDA flow and can easily be integrated into the standard design flows.

Figure 4.1: TMR Conversion of a sequential element

#### 4.1.1 Create TMR Netlist

As mentioned before, TMR is a redundancy method which uses three identical instances of the desired circuit logic and a voter which outputs the majority of the three replicas. TMR can mask a single fault happening among the triplet members at the same time. This fault can be masked thanks to the existence of the other two TMR instances.

Our spatial TMR RADHARD flow starts by converting the original netlist into a TMR one. Fig. 4.1 presents the TMR structure conversion in our flow, which exploits the TMR technique only for FFs, and not for the entire circuit. Each FF of the original design is converted into a TMR structure. This structure consists of three FFs replicas and a majority voter. FFs' inputs are tied together, as they must receive the same input and the clock signal, while their outputs are connected to the voter. The latter (Fig. 4.2) compares their result and returns the majority of them to the rest of the circuit logic.

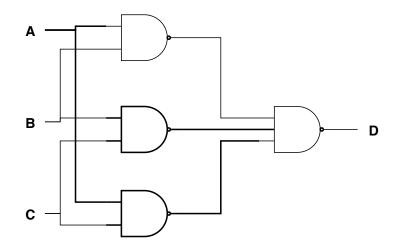

Figure 4.2: Schematic of majority gate using NAND2 gates

#### 4.1.2 TMR Groups and Minimum Spacing Constraints

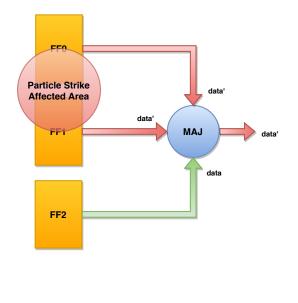

A key element in the RADHARD Legalisation process is the notion of the TMR group. A TMR group consists of the FFs of a TMR structure. When a radiation particle strikes the integrated circuit (IC), it creates a charge which can affect an area containing multiple circuit components. In recent technologies, this phenomenon has been inflamed by the components shrinking. Moreover, state-of-the-art industrial EDA tools tend to place interconnected cells near each other to achieve better PPA results. However, for a TMR group, this would be disastrous. Placing the members of a TMR group near each other will significantly increase the probability of a fault being induced, as more than one members being affected by the same particle strike, as shown in Fig. 4.3a.

In order to make the TMR group resistant to particle hits, the individual FFs of a TMR group must be spatially distributed, based on a user-specified spacing constraint, signifying that all group members should be spaced from each other by a given minimum distance, as shown in Fig. 4.3b. The value of the spacing depends on the charged area range, which is highly related to the radiation particle expected diameter, its Linear Energy Transfer (LET) and the speed and angle under which it hits the chips.

(a) Particle strike affecting multiple members of a TMR triplet

(b) Particle strike affecting only one TMR member since they are distributed

Figure 4.3: Applying Minimum Spacing Constraint reduces the probability a particle strike affect more than one TMR members

#### 4.1.3 Abax Modification

As mentioned in Section 3.2.1, Abax is a greedy, sequential Displacement-driven Legaliser based on Abacus, performing multiple legalisation runs for multiple cells orders, based on cells' x-coordinate, *i.e.* increasing, decreasing and centre-outwards, resulting in a legal placement with the best cost across the orders. Moreover, Abax supports both SRHC and MRHCs and works in stages, legalising first the MRHCs, whose legalisation is harder compared to SRHCs, and continues with the legalisation of SRHCs.

The Abax legaliser also support blockages, the positions of which create core row cuts and divide core area rows into subrows, which represent the legal placement cell positions. Thus, each core area row contains a set of subrows, represented by their leftmost x-coordinate and width.

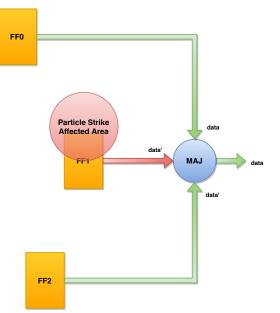

Figure 4.4: Radiation Hardening Legalisation Stages

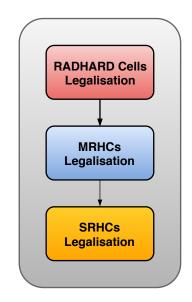

In our RADHARD version of Abax, we have added one more stage prior to the MRHCs and SRHCs legalisation stages, the RADHARD cells legalisation stage, which aims to place triplet FFs in positions which satisfy their spacing constraints. Therefore, the RADHARD Legalisation algorithm consists of a total of three stages, as shown in Fig. 4.4:

- 1. **RADHARD Cells Legalisation**, finding the best, in terms of displacement, legal position for each RH cell, satisfying user-specified minimum spacing constraints among the TMR FFs triplet, and fixing it to this position to guarantee no spacing violations,

- 2. MRHCs legalisation, and fixing them after its completion,

- 3. SRHCs legalisation

#### 4.1.4 Satisfy Spacing Constraints

As mentioned before, the goal of Min-bounded RADHARD Legalisation is to satisfy a minimum spacing constraint among the TMR replicas. Each member of a TMR group must be placed with a distance, at least equal to the specified minimum spacing constraint, among the other members of this group.

One way to ensure the minimum distance among the TMR FFs triplet is to "bloat" or "inflate" the already legalised member of a TMR group. Cell Inflation is a technique used to reduce whitespace or even routing congestions. During inflation, we temporarily increase the size of the cell, making it occupy more area than before (cell upscaling). In our context, cell inflation can be used to inflate the already legalised members of a TMR group that way their new width and height will be increased by current TMR group's minimum spacing constraint in both directions (left and right, top and bottom respectively).

However, cell inflation for RADHARD presents several drawbacks. It has to be performed prior to legalisation leading to space all FFs, instead of only the FFs consisting each TMR group. Hence, a lot of area would be wasted, leading to worse placement and thus worse PPA results. Further on, before the next step, *i.e.* MRHC legalisation, the previously inflated TMR group cells would have to be deflated. Due to these difficulties, instead of directly bloating TMR group cells, we implemented an indirect cell inflation approach.

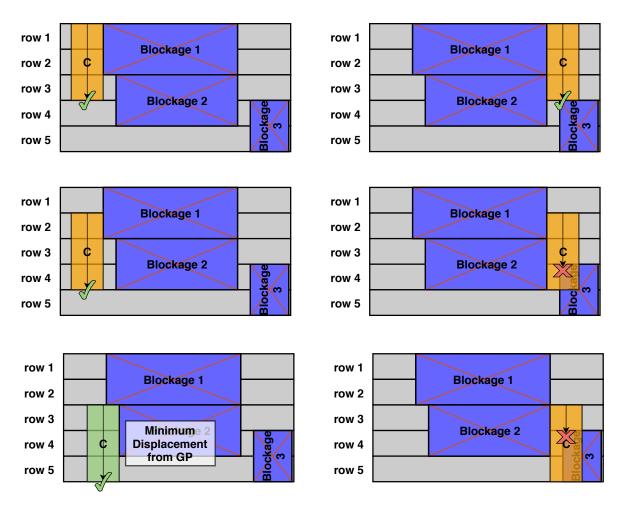

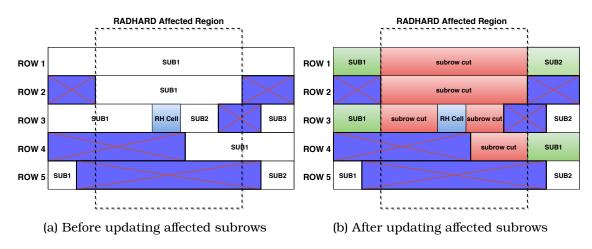

The indirect way we achieve cell inflation exploits the Abax's feature of diving the core area into a set of rows and subrows, where their x-coordinates and width represent the latter. Thus, instead of changing cell size, we perform cell inflation by changing the x-coordinate and width of the subrows affected by the inflated cell. This method fills the parts of the affected subrows, which lie inside a region around the inflated cell, called RADHARD Affected Region. The latter spreads around the inflated cell in a distance equal to the minimum spacing constraint specified for the TMR group that the inflated cell belongs. The update of the affected subrows creates white space, where other cells within the same group cannot be placed. This process is performed during the legalisation of each RADHARD cell to the already legalised members of the same TMR group, preventing the legaliser from placing another cell of the same group within the spacing constraint range, *i.e.* within the RADHARD Affected Region, as these positions are presented as not available. When a RADHARD cell is placed, the subrow fills are reverted, to place the next one.

Fig. 4.5 presents a mock-up example, including all the possible cases, of updating the subrows of the affected rows. In Fig. 4.5a is presented the subrows state before updating the subrows affected by the RADHARD inflation, while their up-

Figure 4.5: Subrows Fill Cases

dated state is presented in Fig. 4.5b. The black rectangle represents the RADHARD Affected Region, *i.e.* the area influenced by the cell inflation defining the minimum spacing constraint and the purplish crossed rectangles represent already placed blockages or fixed cells. With blue colour is the cell that must be inflated and in pinkish is the white space area which will be affected by the inflation, while in green colour are the subrows that their x-coordinate or width have been updated due to the inflation.

There are five cases to update the subrows, *i.e.*

- 1. A subrow may be divided into smaller subrows (ROW1 SUB1 and SUB2)

- 2. A subrow may be removed, as it is occupied entirely by the RADHARD Affected Region (ROW2 SUB1)

- 3. The width of a subrow may be decreased (ROW3 SUB1)

- 4. The width and the x-coordinate of a subrow may be changed (ROW4 SUB1)

- 5. The inflation may not perform any change to the subrows (ROW5 SUB1 and SUB2)