## University of Thessaly

#### PhD Thesis

# System software techniques to enhance reliability of modern platforms.

Author: Supervisor: Nikolaos Bellas

Advising committee:

Nikolaos BELLAS,

Spyros LALIS,

Christos D. ANTONOPOULOS

A thesis submitted in fulfillment of the requirements for the degree of Doctor of Philosophy

in the

Department of Electrical and Computer Engineering

October 17, 2018

"Optimism is the faith that leads to achievement. Nothing can be done without hope and confidence."

"Helen Keller"

# **Abstract**

#### Konstantinos Parasyris

System software techniques to enhance reliability of modern platforms.

Chip manufacturers introduce redundancy at various levels of CPU design to guarantee correct operation even for worst-case combinations of non-idealities in process variation and system operating conditions. This redundancy is implemented partly in the form of wide voltage margins.

This PhD dissertation is based on the concept that these conservative design runes are mostly excessive, as they account for execution scenarios that rarely appear during the lifetime of the systems. If the faults are ignored the system will result to application crashes or even system-wide failures. Our software based approach treats these faults to enable execution in such conditions.

The approach is based on the concept that many applications domains it is not the exact output that matters but a rough estimation of the output. Therefore, we propose a programming model in which the developer can define which parts of the application are more significant than others. The programming model extends a widely used parallel programming model, called OpenMP. The developer provides information about the *significance* of computations and the programming model exposes a parameter, called *ratio*, which can control the extend of quality degradation and energy efficiency.

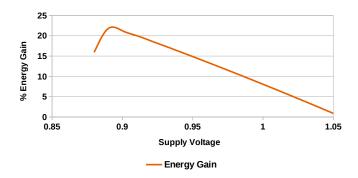

The idea of significance-aware computing is ported into two different computing paradigms, the fault tolerant one and the approximate. In the case of fault tolerant computing we implement a significance-centric programming model and runtime support which sets the supply voltage in a multicore CPU to sub-nominal values to reduce the energy footprint and provide mechanisms to control output quality. The developers specify the *significance* of application tasks respecting their contribution to the output quality and provide check and repair functions for handling faults. On a multicore system we evaluate our approach using an energy model which quantifies the energy reduction. When executing the least significant tasks unreliably, our approach leads to 20% CPU energy reduction with respect to a reliable execution and has minimal quality degradation.

In the case of approximate computing, we implement a similar programming model that promotes the combination of the *significance* and *ratio* features. The approach using analytical models of the energy consumption of the application can

efficiently decide the degree of approximation to meet certain user defined energy requirements.

There are many application domains which require their computations to be performed without any errors. Our study on the x86-64 Haswell and Skylake multicore microarchitectures reveals wide voltage which can be removed without observing any errors. These margins can reach up to 22% and 13% of the nominal supply voltage for the Skylake and Haswell architectures respectively. The margins vary across different microarchitectures, different chip parts of the same microarchitecture, and across different workloads.

We introduce a model which can be used dynamically to adjust the supply voltage of modern multicore x86-64 CPUs to just above the minimum required for safe operation. We identify a set of performance metrics – directly measurable via performance monitoring counters – with high predictive value for the minimum tolerable supply voltage ( $V_{min}$ ). We use benchmarks that vary in terms of application domain, resource utilization and pressure, and software/hardware interaction characteristics to train a  $V_{min}$  prediction model. Finally, at execution time those metrics are monitored and serve as input to the model, in order to predict and apply the appropriate  $V_{min}$  for the workload. Compared to the conventional approaches, our methodology achieves up to 42% energy savings for the Skylake family and 34% for the Haswell family for complex, real-world applications.

Last but not least, during the course of the thesis we implemented the infrastructure to observe accurately the application resiliency of faults as well as to identify voltage and frequency margins of modern processors. GemFI is a fault injection tool based on the cycle accurate full system simulator Gem5. GemFI provides fault injection methods and is easily extensible to support future fault models. It also supports multiple processor models and ISAs and allows fault injection in both functional and cycle-accurate simulations. GemFI offers fast-forwarding of simulation campaigns via checkpointing. Moreover, it facilitates the parallel execution of campaign experiments on a network of workstations.  $XM^2$  enables the evaluation of software on systems operating outside their nominal margins. It supports both bare-metal and OS-controlled execution using an API to control the fault injection procedure and provides automatic management of experimental campaigns.

# Περίληψη

Κωνσταντίνος Παρασύρης

Αύξηση ανθεκτικότητας των εφαρμογών σε σφάλματα σε σύγχρονες πλατφόρμες

Η βιομηχανία των ημιαγωγών έχει βασιστεί τις τελευταίες δεκαετίες στο νόμο του Moore, ο οποίος προβλέπει κάθε 18 μήνες τον διπλασιασμό του αριθμού των transistors ανά μονάδα επιφάνειας σε ολοκληρωμένα κυκλώματα βασισμένα σε τεχνολογία CMOS. Σε αντιδιαστολή με το παρελθόν (πριν από το 2004), όπου οι σχεδιαστές επεξεργαστικών συστημάτων, μέσω της αύξησης του αριθμού των transistor, είχαν ως στόχο την αντίστοιχη αύξηση της απόδοσης, η νέα πραγματικότητα θέτει την μείωση της κατανάλωσης ισχύος (και ενέργειας) ως την μεγαλύτερη πρόκληση στην σχεδίαση επεξεργαστών.

Ταυτόχρονα, η μεγάλη πυχνότητα τοποθέτησης των transistors οδηγούν στην αναξιόπιστη λειτουργία των σύγχρονων επεξεργαστών. Η αναξιοπιστία αυτή οφείλεται εν μέρει στις δυναμιχές διαχυμάνσεις ρεύματος και τάσης (supply voltage) οι οποίες είναι πιο πιθανό να δημιουργήσουν λάθη χρονισμού σε μιχρές γεωμετρίες τεχνολογίας CMOS. Επίσης είναι πιο πιθανά τα κατασκευαστικά λάθη (fabrication faults) λόγω ατελειών της διαδικασίας φωτολιθογραφίας. Επιπλέον, παροδικά λάθη (transient faults) που οφείλονται σε εξωγενείς παράγοντες, όπως alpha particles, έχουν μεγαλύτερη επίδραση σε μιχρότερες γεωμετρίες τεχνολογίας CMOS. Για να επιτευχθεί αξιόπιστη λειτουργία υπό αυτές τις συνθήκες, οι σχεδιαστές σύγχρονων επεξεργαστικών συστημάτων χρησιμοποιούν συντηρητικές σχεδιαστικές τεχνικές, όπως υψηλά περιθώρια τάσης τροφοδοσίας (Vdd) και συχνότητας ρολογιού έτσι ώστε ο επεξεργαστής να προστατεύεται από κάθε πιθανότητα λαθών χρονισμού. Οι συντηρητικές αυτές τεχνικές μπορεί μεν να προστατεύουν την αξιόπιστη λειτουργία του επεξεργαστή, έχουν όμως ως αποτέλεσμα μεγάλη σπατάλη σε ισχύ και ενέργεια η οποία φτάνει μέχρι και το 35% σε αρκετές περιπτώσεις.

Η βασιχή ιδέα της παρούσας διδαχτοριχής διατριβής βασίζεται στο ότι αυτές οι συντηρητιχές τεχνιχές σχεδιασμού είναι σχεδόν πάντα περιττές και αντιστοιχούν σε περιπτώσεις λειτουργίας που σχεδόν ποτέ δεν πρόχειται να συμβούν ταυτόχρονα κατά την διάρχεια της λειτουργίας του επεξεργαστή. Χρησιμοποιώντας τεχνιχές χυρίως στο επίπεδο λογισμιχού συστήματος και εφαρμογών, η διατριβή προτείνει την λειτουργία του επεξεργαστή πολύ κοντά στις αχραίες καταστάσεις λειτουργίας του και την εξάλειψη του μεγαλύτερου μέρους του σχεδιαστιχού περιθωρίου. Για παράδειγμα, η δυναμιχή μείωση της τάσης τροφοδοσίας ενός επεξεργαστή κατά την διάρχεια λειτουργίας του μπορεί να επιφέρει μεγάλες βελτιώσεις στην κατανάλωση ισχύος του, αλλά, εφόσον δεν ελεγχθεί, είναι δυνατόν να δημιουργήσει λανθασμένα αποτελέσματα ή και να διαχόψει απότομα την

λειτουργία του. Από την άλλη, η αύξηση της συχνότητας του ρολογιού ενός επεξεργαστή, μπορεί μεν να βελτιώσει την απόδοση και να επιφέρει μείωση του χρόνου εκτέλεσης, αλλά, μπορεί να δημιουργήσει προβλήματα στην αξιοπιστία της λειτουργίας του.

Η διατριβή βασίζεται στην ιδέα ότι σε πολλές εφαρμογές (ή επιμέρους φάσεις εφαρμογών) το ακριβές αποτέλεσμα είτε δεν μας ενδιαφέρει, είτε είναι πολύ απαιτητικό σε κύκλους μηχανής και κατανάλωση ενέργειας για να μας συμφέρει να υπολογιστεί. Προτείνουμε ένα νέο προγραμματιστικό μοντέλο στο οποίο ο προγραμματιστής μπορεί να χαρακτηρίσει την σημαντικότητα των διαφορετικών τμημάτων μιάς εφαρμογής και την συνεισφορά τους στην ποιότητα του τελικού αποτελέσματος. Το προγραμματιστικό μοντέλο επεκτείνει το γνωστό μοντέλο OpenMP που χρησιμοποιείται ευρέως στον παράλληλο προγραμματισμό. Μέσω της πληροφορίας της σημαντικότητας που παρέχει ο προγραμματιστής σε επίπεδο πηγαίου κώδικα (source code) και μιας επιπλέον παραμέτρου, που ονομάζεται ratio ο προγραμματιστής μπορεί και ελέγχει την αναλογία της μείωσης της ενέργειας προς την μείωση της ποιότητας του αποτελέσματος.

Η διατριβή υλοποιεί την παραπάνω ιδέα σε δύο διαφορετιχούς τομείς υπολογισμών, τον προσεγγιστιχό (approximate) τομέα και στον τομέα των ανθεχτιχών υπολογισμών σε σφάλματα (fault tolerant). Στον τομέα τον ανθεχτιχών υπολογισμών, υλοποιείται η υποδομή του λογισμιχού συστήματος (προγραμματιστιχό μοντέλο και σύστημα χρόνου εχτέλεσης) για να καλύψει περιβάλλοντα αναξιόπιστης υπολογιστιχής. Η υλοποιήση αυτή αναφέρεται χυρίως στο ότι σε αναξιόπιστα περιβάλλοντα που μπορεί να προχαλούνται απο χαμηλότερη τάση τροφοδοσίας ή/και υψηλότερη συχνότητα ρολογιού μπορεί να συμβεί οποιοδήποτε λάθος στο υλιχό το οποίο είναι πέρα από τον έλεγχο του προγραμματιστή. Αυτό επιβάλλει την ύπαρξη μηχανισμών αναγνώρισης και διόρθωσης λαθών καθώς και μηχανισμούς απομόνωσης λαθών ώστε αυτά να μην επεχταθούν σε σημεία του χώδιχα που μπορεί να είναι χρίσιμα για την σωστότητα της εφαρμογής. Οι μηχανισμοί αυτοί θα πρέπει να έχουν όσο το δυνατόν υψηλότερο ποσοστό ανίχνευσης λαθών, αλλά και μιχρή επιβάρυνση στην απόδοση της εφαρμογής.

Η διατριβή προτείνει και υλοποιεί αναλυτικά μοντέλα απόδοσης και κατανάλωσης ενέργειας σε πολυπύρηνους επεξεργαστές. Πολύ σημαντική επίσης είναι και η αναλυτική μοντελοποίηση των λαθών χρονισμού (fault modeling) που συμβαίνουν σε έναν επεξεργαστή σε συνάρτηση με την τάση τροφοδοσίας του επεξεργαστή αυτού. Το πλήρες σύστημα λογισμικού αξιόπιστης υπολογιστικής, μαζί με τα μοντέλα αυτά, χρησιμοποιούνται σε εκτεταμένες προσομοιώσεις εφαρμογών στον προσομοιωτή GemFI για την εκτίμηση της βελτίωσης κατανάλωση ενέργειας (λόγω μειωμένης τάσης τροφοδοσίας) χωρίς αλλοίωση των τελικών αποτελεσμάτων του υπολογισμού και χωρίς διακοπή της λειτουργίας του επεξεργαστή. Τα πειράματα έδειξαν ότι μπορούμε να μειώσουμε την τάση τροφοδοσίας ενός επεξεργαστή κατά μέσο όρο 15% μέχρι να φτάσουμε στο Point of First Failure (PoFF), κάτω από το οποίο ο επεξεργαστής εκτίθεται σε μαζικά λάθη χρονισμού και είναι αδύνατη (ή ασύμφορη) κάθε προσπάθεια λειτουργίας του. Το σύστημα λογισμικού αξιόπιστης υπολογιστικής επιτρέπει την μείωση της τάσης τροφοδοσίας μέχρι το PoFF (αλλά όχι πιο χαμηλά) αντιμετωπίζοντας επιτυχώς τα λάθη που εμφανίζονται στην περιοχή αυτή και επιτυγχάνοντας μεγάλη μείωση της κατανάλωσης ισχύος/ενέργειας χωρίς

επίπτωση στην ταχύτητα του επεξεργαστή.

Όσον αφορά τον προσεγγιστικό τομέα, προτείνουμε και υλοποιούμε ένα παρόμοιο προγραμματιστικό μοντέλο και ενα σύστημα χρόνου εκτέλεσης (run time system), το οποίο χρησιμοποιώντας αναλυτικά μοντέλα της απόδοσης και κατανάλωσης ισχύος του επεξεργαστή παίρνει ενημερωμένες αποφάσεις για τη ροή και το συντονισμό της εκτέλεσης του προγράμματος. Ο μηχανισμός αυτός επιτρέπει στον προγραμματιστή να προσαρμόσει δυναμικά την ποιότητα των αποτελεσμάτων μιας εφαρμογής με την απόδοση του συστήματος και την κατανάλωση ισχύος/ενέργειας.

Για πολλες εφαρμογές όμως, είναι απαραίτητοι οι αχριβείς υπολογισμοί καθώς δεν ανέχονται μείωση της ποιότητας του αποτελέσματος. Επομένως, μέσω μιάς σειράς πειραμάτων σε Intel x86-64 επεξεργαστές αναγνωρίσαμε την μέγιστη μείωση της τάσης τροφοδοσίας έτσι ώστε ο επεξεργαστής να παραμένει σε ασφαλή ζώνη λειτουργίας (χωρίς σφάλματα). Τα πειράματα αυτά φανέρωσαν ότι τα περιθώρια μείωσης της τάσης φτάνουν μέχρι 22% για επεξεργαστές Skylake και 13% για Haswell.

Η παραπάνω ανάλυση των περιθωρίων τάσης έδωσαν την δυνατότητα να δημιουργηθεί ένα μοντέλο μηχανικής μάθησης που χρησιμοποιήθηκε για την πρόβλεψη μελλοντικών περιθωρίων τάσης τροφοδοσίας. Το μοντέλο αυτό δέχεται σαν είσοδο τιμές των performance counters του επεξεργαστή (ενώ το πρόγραμμα εκτελείται) και προβλέπει το περιθώριο τάσης για το επόμενο χρονικό διάστημα. Με άλλα λόγια, η διατριβή αυτή έχει δείξει πειραματικά την συσχέτιση μεταξύ γεγονότων σε επίπεδο μικροαρχιτεκτονικής (όπως αυτά περιγράφονται από τους performance counters του επεξεργαστή) και του μέγιστου περιθωρίου τάσης τροφοδοσίας. Το μοντέλο αυτό χρησιμοποιείται από έναν εξελιγμένο governor τάσης/συχνότητας που ορίζει κάθε φορά την τάση του επεξεργαστή ώστε να επιτυγχάνουμε μεγάλη μείωση στην κατανάλωση ισχύος χωρίς τον κίνδυνο μειωμένης αξιοπιστίας. Σε σύγκριση με τον συμβατικό Intel DVFS (Dynamic Voltage Frequency Scaling) governor, η μέθοδός μας επιτυγχάνει μείωση ενέργειας κατά 42% σε επεξεργαστές Skylake και 34% σε επεξεργαστές Haswell.

Η διατριβή αυτή επίσης μελέτησε την επίδραση που έχουν στα περιθώρια τάσης τροφοδοσίας οι βελτιστοποιήσεις που κάνουν οι μεταγλωττιστές στον κώδικα μιας εφαρμογής. Με τη χρήση του εργαλείου ΧΜ2 διαπιστώθηκε ότι οι μετασχηματισμοί που μειώνουν τις προσπελάσεις στην κύρια μνήμη έχουν μεγάλη επίδραση στα περιθώρια της τάση τροφοδοσίας. Σε γενικές γραμμές όμως, η τάση τροφοδοσίας είναι περισσότερο συνάρτηση της μικροαρχιτεκτονικής του επεξεργαστή παρά των βελτιστοποίησεων στον κώδικα που επιφέρει ο compiler.

Η διδακτορική διατριβή δημιούργησε επίσης την ερευνητική υποδομή για τα πειράματα που διεξήχθησαν στα πλαίσια της αξιολόγησης των τεχνικών που περιγράφησαν στις προηγούμενες παραγράφους. Το GemFI είναι ένα εργαλείο δημιουργίας και προσομοίωσης λογικών λαθών σε ένα πολυπύρηνο επεξεργαστικό σύστημα. Δίνει την δυνατότητα στο χρήστη να εισάγει διάφορους τύπους λαθών, σε οποιαδήποτε χρονική στιγμή κατά τη διάρκεια εκτέλεσης του προγράμματος, και σε οποιοδήποτε τμήμα της αρχιτεκτονικής του επεξεργαστή. Το GemFI, το οποίο βασίζεται στο γνωστό προσομοιωτή Gem5, μπορεί να εκτελέσει πλήρως το λογισμικό εφαρμογών και συστήματος για μεγάλη γκάμα

διαφορετικών αρχιτεκτονικών, δίνοντας έτσι τη δυνατότητα μελέτης της αξιοπιστίας του συστήματος κάτω απο διαφορετικές συνθήκες.

Επίσης δημιουργήθηκε ένα δεύτερο εργαλείο, ο eXtended Margins eXperiment Manager (XM2) που αυτοματοποιεί τη δημιουργία πειραμάτων σε πραγματικούς επεξεργαστές που μπορούν να τίθενται σε μη-αξιόπιστες καταστάσεις τάσης και συχνότητας. Το εργαλείο χρησιμοποιήθηκε για την δημιουργία τέτοιων πειραμάτων για τον χαρακτηρισμό της αξιοπιστίας του υλικού και για τον προσδιορισμό της ανοχής σε λάθη λογισμικού εφαρμογών που εκτελούνται σε επεξεργαστές x86-64 (Skylake, Haswell) και ARM.

# Acknowledgements

This thesis is the result of research work conducted while I was pursuing my PHD degree in the Department of Electrical and Computing Engineering of University of Thessaly in Greece. I acknowledge the funding agencies which made this research possible through financial means. These include the European Commission through the SCoRPiO EU project as well as the Center for Research & Technology Hellas (CERTH).

First and foremost I would like to thank my mentors, professors Nikolaos Bellas, Spyros Lalis, and Christos D. Antonopoulos from the University of Thessaly. They have been exceptionally good at guiding me during my initial steps, throughout my Master's and PHD, and have molded me as a researcher. Without their guidance and mentoring none of this work would be possible. They were always available to discuss and provide constructive criticism.

I would also like to thank my colleagues who provided me with help, as well as stress relief with their wit and humor to ease the burden of research. Special thanks to my friend and colleague Vassilis Vassiliadis with whom I shared, pretty much all of my research career thus far. Our joined research efforts, stimulating, and often heated, discussions were very educating and most of the time relaxing.

Last but not least, I owe great many thanks to my friends and family. Especially, I owe to my parents, Wyanda And Antonis, for their unconditional love and support all along my academic pursuits. My friends will always have a special place in my heart because they were always there during good times, and bad times to support me with patience and love. The least I can do is dedicate this thesis to them all.

# **Contents**

| A  | bstra  | ct       |                                                                | ii   |

|----|--------|----------|----------------------------------------------------------------|------|

| Па | ερίληψ | νη       |                                                                | iv   |

| A  | cknov  | wledge   | ments                                                          | viii |

| 1  | Intr   | oductio  | on                                                             | 1    |

|    | 1.1    | The re   | eality of power consumption                                    | 1    |

|    | 1.2    | Reliab   | oility and Power                                               | 2    |

|    | 1.3    | Desig    | n Space exploration                                            | 3    |

|    |        | 1.3.1    | Hardware Level                                                 | 3    |

|    |        | 1.3.2    | Software level                                                 | 4    |

|    |        | 1.3.3    | Significance Definition                                        | 6    |

|    | 1.4    | Contr    | ibutions                                                       | 6    |

|    |        | 1.4.1    | Significance Aware Computing                                   | 8    |

|    |        |          | Significance aware fault tolerant programming model            | 9    |

|    |        |          | Significance aware Runtime system for fault tolerant computing | 9    |

|    |        |          | Power/energy and fault modeling of the <i>unsafe</i> region    | 10   |

|    |        |          | Significance-aware programming model for approximate com-      |      |

|    |        |          | puting                                                         | 10   |

|    |        |          | Significance aware Runtime system for approximate computing    | 10   |

|    |        | 1.4.2    | Exploiting Voltage Margins for Energy Efficiency               | 10   |

|    |        | 1.4.3    | Experimental Frameworks for Reliability Analysis               | 11   |

|    | 1.5    | Outlin   | ne                                                             | 12   |

| 2  | Sign   | nificano | ce Aware Fault Tolerant Computing                              | 14   |

|    | 2.1    | Contr    | ibutions                                                       | 15   |

|    | 2.2    | Progra   | amming Model Objectives & Properties                           | 16   |

|    |        | 2.2.1    | Significance Characterization                                  | 16   |

|    |        | 2.2.2    | Safety Isolation                                               | 16   |

|    |        | 2.2.3    | Architecture Neutrality                                        | 16   |

|    |        | 2.2.4    | Parallelism Expression                                         | 17   |

|    |        | 2.2.5    | Relaxed Synchronization                                        | 17   |

|    |        | 2.2.6    | User Friendliness                                              | 17   |

|    | 2.3    | High     | Level Description                                              | 17   |

|    |        | 2.3.1    | Task-Based Programming model                                   | 17   |

|   |            | Pragmas for the Expression of Parallelism and Significance    | 18           |

|---|------------|---------------------------------------------------------------|--------------|

|   |            | Early Error Detection To minimize Fault Propagation           | 19           |

|   |            | Elastic Synchronization                                       | 20           |

|   |            | Significance of Data                                          | 20           |

|   | 2.4        | Syntax                                                        | 21           |

|   |            | 2.4.1 Task Definition and Significance Characterization       | 21           |

|   |            | 2.4.2 Synchronization                                         | 22           |

|   | 2.5        | Example                                                       | 23           |

|   | 2.6        | Programmer Insight                                            | 23           |

|   | 2.7        | Significance-aware Runtime System                             | 24           |

|   |            | 2.7.1 Runtime Execution Management                            | 24           |

|   |            | 2.7.2 Memory Management                                       | 27           |

|   |            | 2.7.3 Life of a group-of-tasks                                | 27           |

|   | 2.8        | Evaluation                                                    | 29           |

|   |            | 2.8.1 Benchmarks                                              | 29           |

|   |            | 2.8.2 Evaluation of Programming model and Runtime System      | 29           |

|   |            | 2.8.3 Runtime Overhead                                        | 30           |

|   | 2.9        | Energy Reduction Evaluation methodology                       | 31           |

|   | 2.10       | Execution Time and Energy Consumption Model                   | 33           |

|   |            | 2.10.1 Execution time modeling                                | 33           |

|   |            | 2.10.2 Power and energy modeling                              | 34           |

|   |            | 2.10.3 Calibration and validation                             | 35           |

|   | 2.11       | Fault Model and Fault Injection Methodology                   | 36           |

|   |            | 2.11.1 Fault modeling                                         | 36           |

|   |            | 2.11.2 Simulation-based fault injection                       | 38           |

|   |            | 2.11.3 Software-based fault injection during native execution | 39           |

|   | 2.12       | Experimental Evaluation                                       | 39           |

| 2 | C:         | if an as Assess Assessinate Communica                         | 4 =          |

| 3 | 3.1        | Contributions                                                 | <b>45</b> 45 |

|   |            | Contributions                                                 | 46           |

|   | 3.2<br>3.3 | Programming Model                                             | 47           |

|   | 3.3        |                                                               | 48           |

|   |            | 0 1                                                           | 49           |

|   | 3.4        | 3.3.2 Approximate vs Fault Tolerant Runtime Support           | 49           |

|   | 3.4        | 3.4.1 Approach                                                | 50           |

|   |            | 3.4.2 Experimental Results                                    | 52           |

|   |            | 5.4.2 Experimental Results                                    | 92           |

| 4 | Mod        | leling and Prediction of Voltage Margins in Multicore CPUs    | 57           |

|   | 4.1        | Background                                                    | 57           |

|   | 4.2        | Contributions                                                 | 59           |

|   | 4.3        | Methodology                                                   | 60           |

|   | 4.4        | Offline Characterization Background                           | 60           |

|   |            |                                                               |              |

|   |     | 4.4.1  | Methodology to identify $maxV_{margin}$                          | 60       |

|---|-----|--------|------------------------------------------------------------------|----------|

|   |     | 4.4.2  | Results of offline $\max V_{\mathrm{margin}}$ Characterization   | 62       |

|   |     | 4.4.3  | Performance Counter Profiling                                    | 65       |

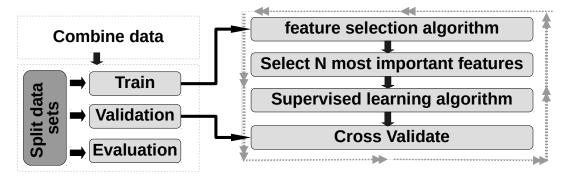

|   | 4.5 | Mode   | ling phase                                                       | 66       |

|   |     | 4.5.1  | Combine Offline Data                                             | 66       |

|   |     | 4.5.2  | Data Splitting                                                   | 67       |

|   |     | 4.5.3  | Model fitting                                                    | 68       |

|   |     |        | Feature Number                                                   | 68       |

|   |     |        | Feature Selection Algorithm                                      | 68       |

|   |     |        | Supervised Learning Algorithm                                    | 70       |

|   |     |        | Hyper-parameter selection                                        | 70       |

|   |     | 4.5.4  | Safety Margin                                                    | 70       |

|   | 4.6 | Evalu  | ation                                                            | 71       |

|   |     | 4.6.1  | Mixed Workload Long Run Evaluation                               | 74       |

|   | 4.7 | Voltag | ge Emergencies                                                   | 74       |

| 5 | T   |        | tal Engageannaulas fem Daliabilitas Amalanda                     | 76       |

| 3 | 5.1 |        | Ital Frameworks for Reliability Analysis ibutions                | 76<br>76 |

|   | 5.2 |        | T:Fault Injection Tool for Studying the Behavior of Applications | 70       |

|   | J.Z |        | areliable Substrates                                             | 77       |

|   |     | 5.2.1  | The Gem5 Simulator                                               | 77       |

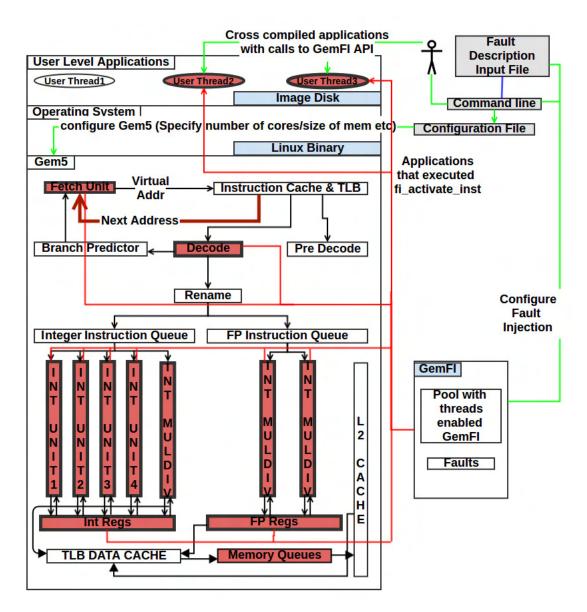

|   |     | 5.2.2  | GemFI Design and Implementation                                  | 77       |

|   |     | J.Z.Z  | GemFI User Interface                                             | 78       |

|   |     | 5.2.3  | Simple Example                                                   | 80       |

|   |     | 5.2.4  | GemFI Internals and Implementation                               | 80       |

|   |     | 5.2.5  | Simulation Checkpointing                                         |          |

|   |     | 5.2.6  | Simulation Campaigns on a Network Of Workstations                |          |

|   |     | 5.2.7  | Validation                                                       |          |

|   |     | 0.2.7  | Validation Methodology                                           | 84       |

|   |     |        | Experimental Results                                             | 85       |

|   |     | 5.2.8  | GemFI Performance Evaluation                                     | 88       |

|   | 5.3 |        | A Framework for Evaluating Software on Reduced Margins           |          |

|   |     |        | ware                                                             | 90       |

|   |     | 5.3.1  | Platform Requirements                                            | 90       |

|   |     | 5.3.2  | Tool Design and Configuration                                    | 90       |

|   |     | 5.3.3  | Configuration File                                               | 92       |

|   |     | 5.3.4  | Run-time Library API                                             | 93       |

|   |     | 5.3.5  | Example                                                          | 93       |

|   |     | 5.3.6  | Flow of a Fault Injection Campaign                               | 94       |

|   |     | 5.3.7  | Evaluation                                                       | 96       |

|   | 5.4 | Arm (  | Cortex A53 Vulnerability Analysis                                | 98       |

|   |     | 5.4.1  | Instruction Level Error Resiliency Analysis                      | 99       |

|    |                  | 5.4.2 Error Resiliency of Source Code and Algorithm Transform | ations 100 |

|----|------------------|---------------------------------------------------------------|------------|

|    |                  | 5.4.3 Compiler Optimizations VS Frequency Margins             | 101        |

|    |                  | Source Code Transformations                                   | 104        |

|    |                  | Memory Access Pattern Optimizations                           | 104        |

|    |                  | SIMD Optimizations                                            | 105        |

|    | 5.5              | GemFI versus XM <sup>2</sup>                                  | 106        |

| 6  | Rela             | ted work                                                      | 107        |

|    | 6.1              | Approximate computing                                         | 107        |

|    | 6.2              | Fault Tolerant computing                                      | 109        |

|    |                  | 6.2.1 Power and Energy-Aware Optimization                     | 112        |

|    | 6.3              | Voltage Margin Characterization and Prediction                | 113        |

|    | 6.4              | Fault Injection Tools                                         | 115        |

| 7  | Cor              | clusions                                                      | 117        |

|    | 7.1              | Future Work                                                   | 118        |

| Re | elated           | publications                                                  | 121        |

| Co | ontril           | ution to Joint Publications                                   | 123        |

| Bi | Sibliography 124 |                                                               |            |

# **List of Figures**

| 1.1  | Description of the reliability of a generic CPU for different operating        |    |

|------|--------------------------------------------------------------------------------|----|

|      | points in terms of supply voltage and frequency                                | 4  |

| 1.2  | Application domains with intrinsic error resiliency.                           | 5  |

| 1.3  | Vision of our approach. Applications should be categorized based               |    |

|      | on their contribution to the output quality. Using this information the        |    |

|      | applications should be scheduled in hardware with appropriate levels           |    |

|      | of reliability.                                                                | 7  |

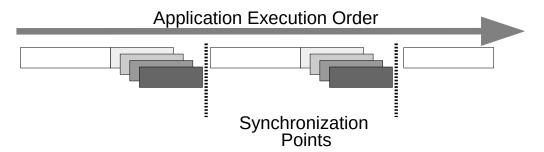

| 2.1  | A single threaded execution of an abstract application, dark rectangles        |    |

|      | correspond to parts of the application that can be parallelized                | 17 |

| 2.2  | Application tasks are created and tagged with significance information         | 19 |

| 2.3  | Non-reliable tasks may execute error identification and correction func-       | 10 |

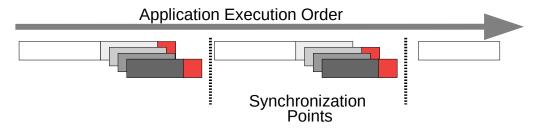

| 2.4  | tions after their termination                                                  | 19 |

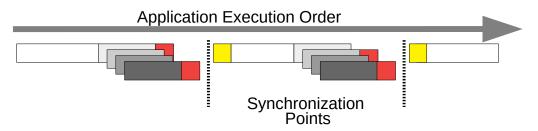

| 2.4  | Result-checks at the group-of-tasks granularity                                | 20 |

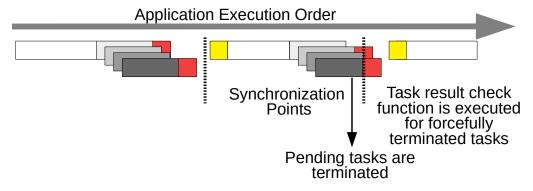

| 2.5  | A case of relaxed synchronization which results to termination of late tasks   | 20 |

| 2.6  | The configurations $FastRel$ , $SlowRel$ and $FastUnRel$ used by the           | _0 |

|      | runtime system, to reduce the energy footprint by exploiting the sig-          |    |

|      | nificance of computations. Our approach exploits non-nominal con-              |    |

|      | figurations within the <i>unsafe</i> region, that are energy-efficient but un- |    |

|      | reliable.                                                                      | 25 |

| 2.7  | The typical life of a group-of-tasks in the context of significance aware      |    |

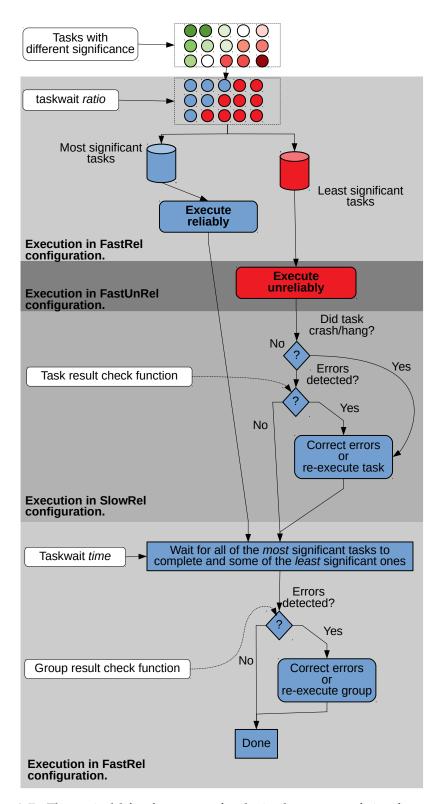

|      | unreliable computing                                                           | 28 |

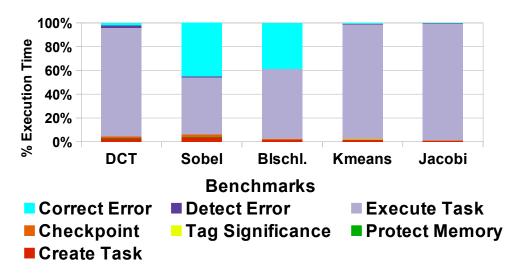

| 2.8  | Breakdown of task execution time, for each benchmark                           | 31 |

| 2.9  | Evaluation approach: we build the performance, energy and fault                |    |

|      | models (left), and use these models to drive experiments and estimate          |    |

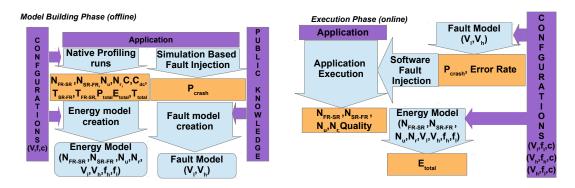

|      | energy consumption (right)                                                     | 32 |

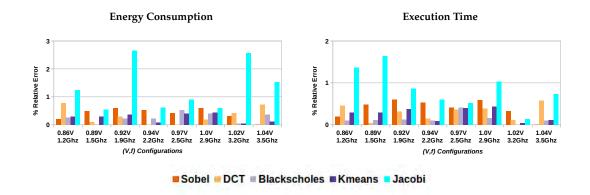

| 2.10 | Relative error for the execution time and energy as predicted by our           |    |

|      | model vs. a real execution, for our application benchmarks when                |    |

|      | half of the tasks execute in the $FastRel = (3.7Ghz, 1.06V)$ configu-          |    |

|      | ration and the other half in a lower-power $SlowRel$ configuration. All        |    |

|      | SlowRel configurations are shown in x-axis.                                    | 35 |

| 2.11 |                                                                                |    |

|      | chitectural CPU level, and the software-based approach during native           |    |

|      | execution.                                                                     | 38 |

|      |                                                                                |    |

| 2.12       | Energy gains of a single task for <i>Sobel</i> executed at voltages $V_l < V_h$ for constant frequency $f_h = 3.7GHz$                                                                                                                                                                                                                                                                               | 40         |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

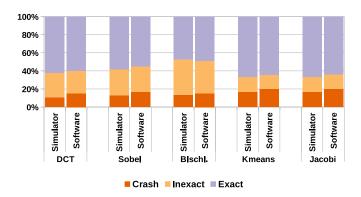

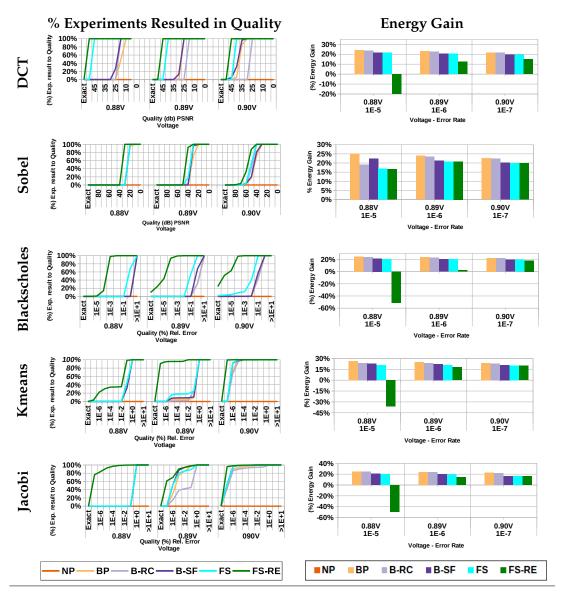

| 2.13       | Experimental results for different $V_l$ values for the $SlowRel$ and $FastUnRel$ configurations. Percentage of experiments which achieved a certain                                                                                                                                                                                                                                                | el         |

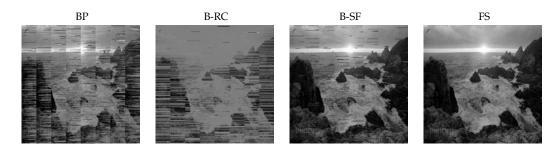

| 2.14       | quality (left), and energy gains with each protection scenario (right) <i>DCT</i> output at 0.89V, with one fault injected every 100,000 cycles. The images correspond (from left to right) to the <i>BP</i> , <i>B-RC</i> , <i>B-SF</i> and <i>FS</i> protection configurations, resulting to PSNRs of 12, 13, 15 and 37 dB respectively. A fault free execution leads results in a PSNR of 43 dB. | 41         |

| 2.15       | NP deterministically leads to crashes                                                                                                                                                                                                                                                                                                                                                               | 43         |

|            | figuration.                                                                                                                                                                                                                                                                                                                                                                                         | <b>4</b> 4 |

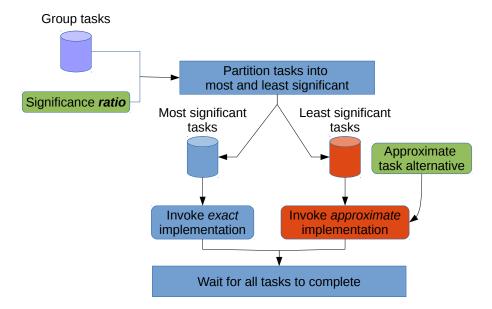

| 3.1        | The typical life of a group-of-tasks in the context of significance aware approximate computing                                                                                                                                                                                                                                                                                                     | 49         |

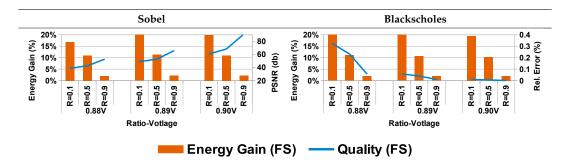

| 3.2<br>3.3 |                                                                                                                                                                                                                                                                                                                                                                                                     | 51         |

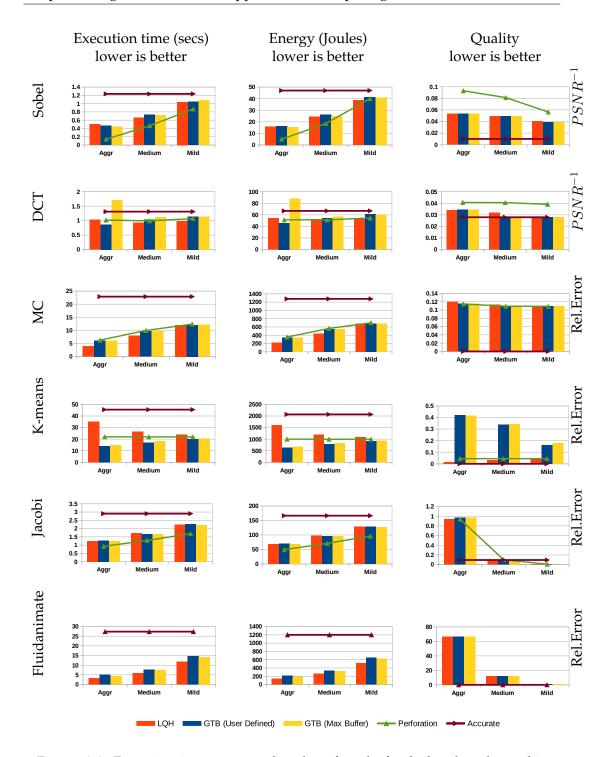

| 3.4        | was not applicable for Fluidanimate                                                                                                                                                                                                                                                                                                                                                                 | 53         |

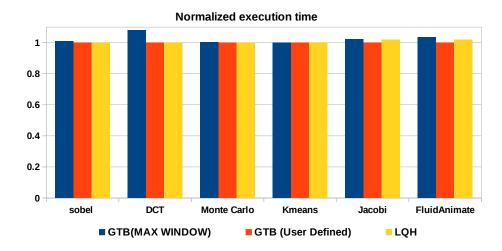

| 3.5        |                                                                                                                                                                                                                                                                                                                                                                                                     | 54<br>55   |

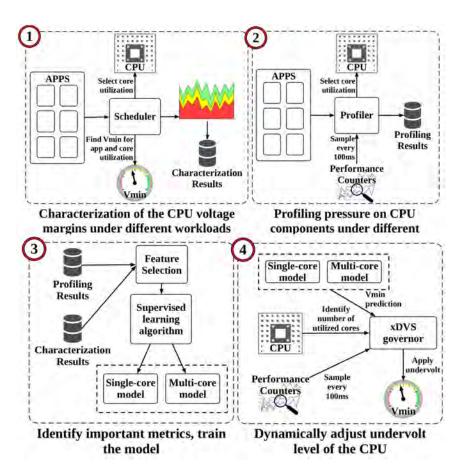

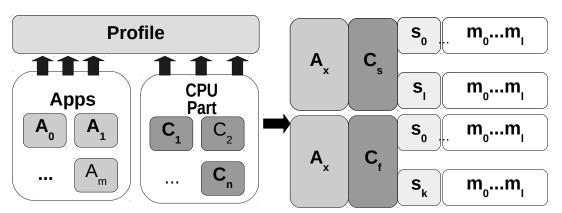

| 4.1        | Overview of our approach for margin characterization, modeling and                                                                                                                                                                                                                                                                                                                                  |            |

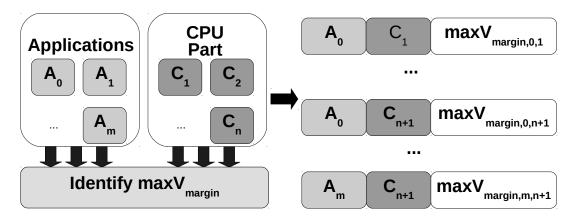

| 4.2        | dynamic prediction                                                                                                                                                                                                                                                                                                                                                                                  | 59<br>60   |

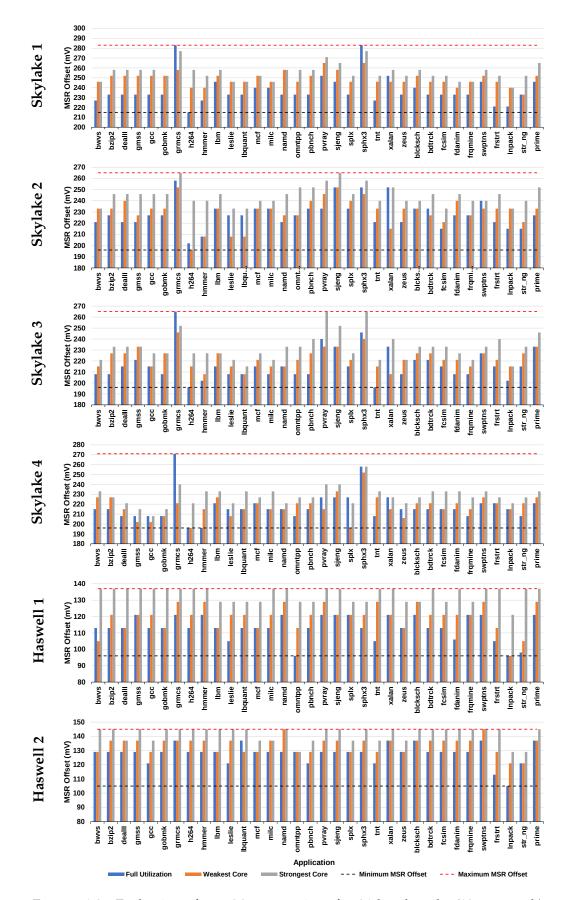

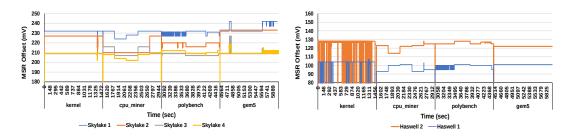

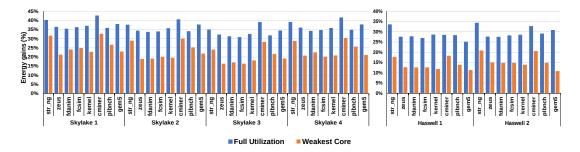

| 4.3        | Evaluation of $maxMargin$ settings for 34 benchmarks (10 runs each) in each workstation; the higher the bar, the wider the exploitable voltage margin. The horizontal dotted lines show the maximum (red) and                                                                                                                                                                                       |            |

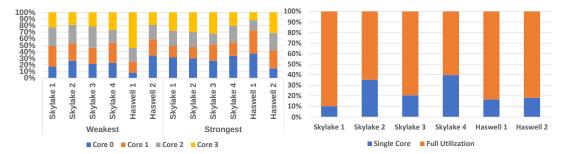

| 4.4        | minimum (black) values of $maxMargin$                                                                                                                                                                                                                                                                                                                                                               | 63         |

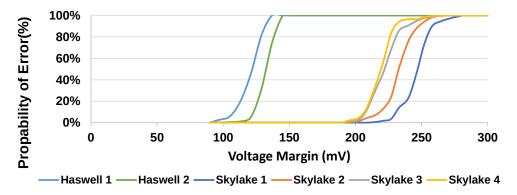

|            | which the core configuration was considered as the weakest                                                                                                                                                                                                                                                                                                                                          | 64         |

| 4.5        | Average (across all configurations) faulure probability CDF for each           |                |

|------------|--------------------------------------------------------------------------------|----------------|

|            | CPU, with respect to the applied $V_{margin}$                                  | 54             |

| 4.6        | Profiling performance metrics                                                  | 55             |

| 4.7        | Methodology Used during the model training phase                               | 66             |

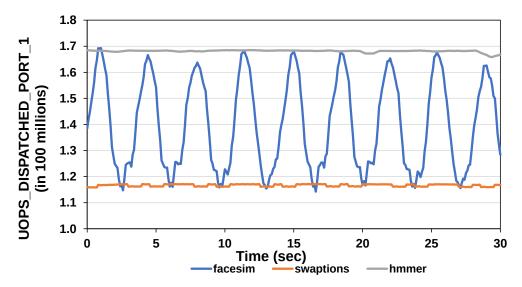

| 4.8        | The number of dispatched uops in port 1 during the execution time of           |                |

|            | an application                                                                 | 57             |

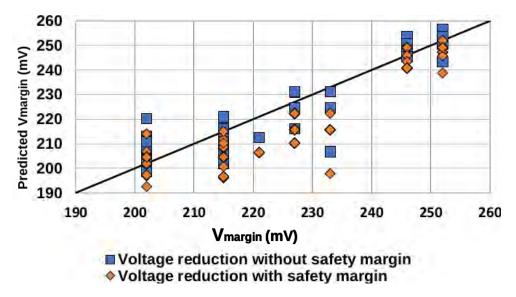

| 4.9        | Prediction of our model with and without the safety margin, for sam-           |                |

|            | ples in the validation data set                                                | <b>7</b> 1     |

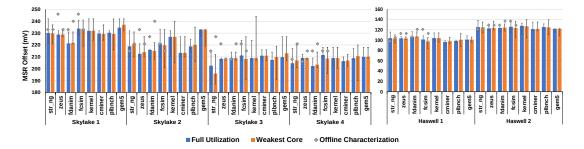

| 4.10       | The bars show the average dynamic $maxV_{margin}$ applied by xDVS for          |                |

|            | Skylake (left) and Haswell (right) workstations. The min-max bars              |                |

|            | represent the minimum and the maximum $maxV_{margin}$ applied by               |                |

|            | xDVS. The gray diamond represents the $maxV_{margin}$ as identified by         |                |

|            | offline characterization at the granularity of the whole application 7         | 72             |

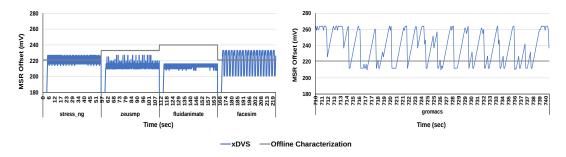

| 4.11       | Timeline showing the applied $maxV_{margin}$ for consecutive single core       |                |

|            | executions of four applications on Skylake 2 (left), and a snapshot of         |                |

|            | full system utilization execution for gromacs application on Skylake 4         |                |

|            | (right)                                                                        | <sup>7</sup> 2 |

| 4.12       | The timeline showing the applied $maxV_{margin}$ while executing the           |                |

|            | large applications in full system utilization for Skylake (left) and Haswell   |                |

|            | (right) workstations                                                           | 73             |

| 4.13       | Energy gains of xDVS when compared with Intel P-state governor                 |                |

|            | for Skylake (left) and Hawell (right) CPUs. The grey horizontal lines          |                |

|            | represent the $maxV_{margin}$ obtained by the offline characterization 7       | 73             |

| 5.1        | An architectural overview of GemFI. The red components of the ar-              |                |

|            | chitecture demonstrate the possible locations where faults can be in-          |                |

|            | jected, whereas the red ovals represent applications which use the ex-         |                |

|            | tended ISA                                                                     | 78             |

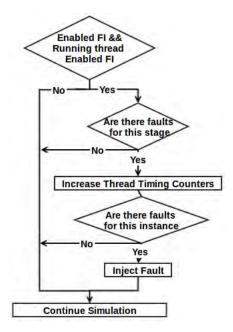

| 5.2        | GemFI functionality on each simulated instruction                              | 31             |

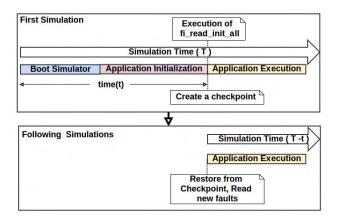

| 5.3        | Simple checkpoint-restore mechanism to speedup simulation campaigns.           | 82             |

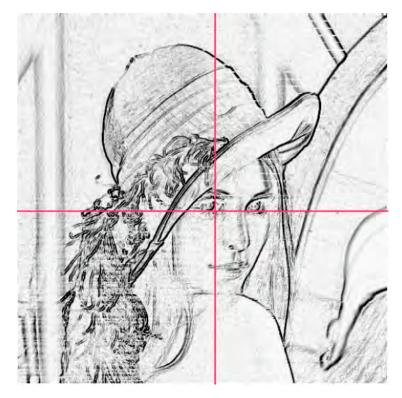

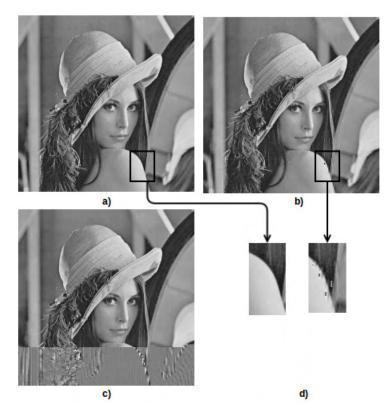

| 5.4        | Different categories of results for the <i>DCT</i> benchmark. a) A strict cor- |                |

|            | rect result b) Relaxed correct result c) SDC d) The difference between         |                |

|            | (a),(b) (loss of quality)                                                      | 34             |

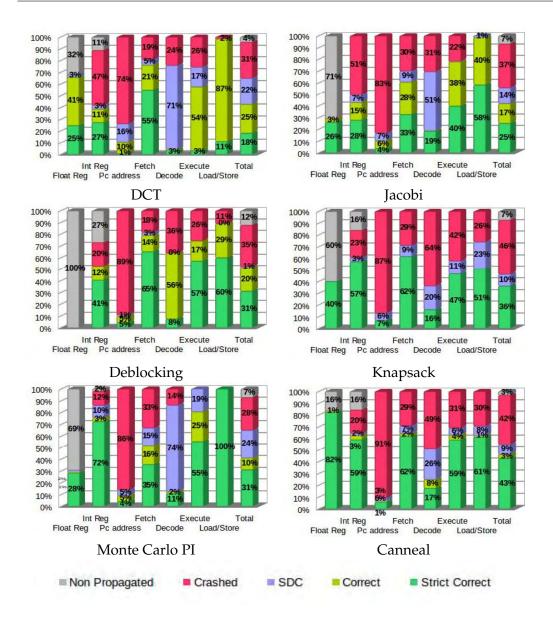

| 5.5        | Application behavior when fault injecting different architectural com-         |                |

|            |                                                                                | 36             |

| 5.6        | Correlation of the timing of fault injection with the effect on the appli-     |                |

|            |                                                                                | 38             |

| 5.7        | GemFI average overhead compared with unmodified Gem5. The chart                |                |

| <b>-</b> 0 | 1                                                                              | 39             |

| 5.8        | Effect of GemFI optimizations on the execution time of fault injection         |                |

|            | campaigns (y-axis in logarithmic scale)                                        | 39             |

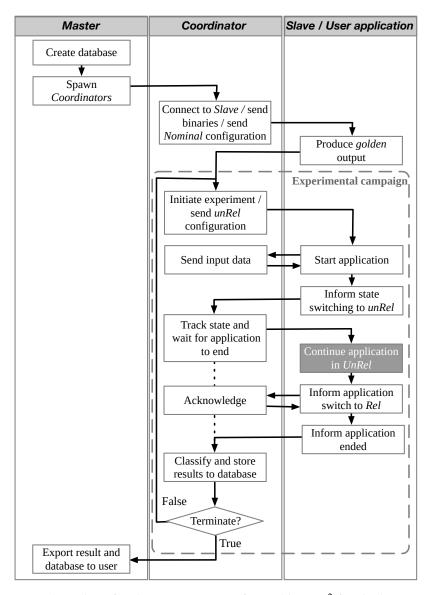

| 5.9         | system architecture of XM <sup>2</sup> . It comprises a single <i>monitoring</i> system and multiple <i>target</i> systems. The components corresponding to dark gray boxes are supplied by the user. XM <sup>2</sup> includes a built-in classifier |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| E 10        | of results, however the latter can be substituted by a user-provided one. 91                                                                                                                                                                         |

| 5.10        | Flow chart for the main steps performed by XM <sup>2</sup> for the basic case of an experimental campaign that does not result to crashes. The dark                                                                                                  |

|             | box is the only state where the target system is configured at an unre-                                                                                                                                                                              |

| <b>5</b> 11 | liable state                                                                                                                                                                                                                                         |

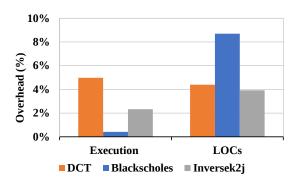

| 5.11        | code (LOC) when compared to a native execution and the original                                                                                                                                                                                      |

|             | version of the code respectively                                                                                                                                                                                                                     |

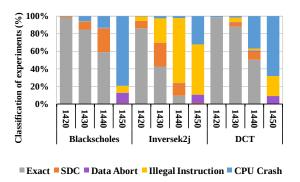

| 5.12        | Experimental results for different applications and different overclocked                                                                                                                                                                            |

|             | configurations                                                                                                                                                                                                                                       |

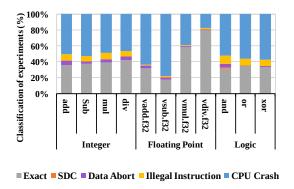

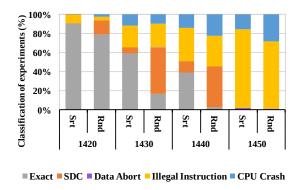

| 5.13        | Experimental results of the instruction error resiliency characteriza-                                                                                                                                                                               |

|             | tion when $V_u = 1.2V$ , $f_u = 1450MHz$ . The X-axis shows the different                                                                                                                                                                            |

|             | microkernels and the Y-axis presents the classification of the experi-                                                                                                                                                                               |

|             | ments according to the effects of overclocking on execution 99                                                                                                                                                                                       |

| 5.14        | Experimental results stressing the branch predictor for the two micro-                                                                                                                                                                               |

|             | kernels for different overclocked frequencies $(f_u)$                                                                                                                                                                                                |

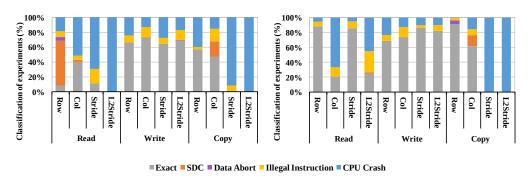

| 5.15        | Experimental results of the $Cache$ microkernels of Table 5.4 for $unRel =$                                                                                                                                                                          |

|             | (1.2V, 1430MHz), when the hardware prefetcher is enabled (left) and                                                                                                                                                                                  |

|             | disabled (right). The Y axis presents the classification of the experi-                                                                                                                                                                              |

|             | ments according to the effects of overclocked execution                                                                                                                                                                                              |

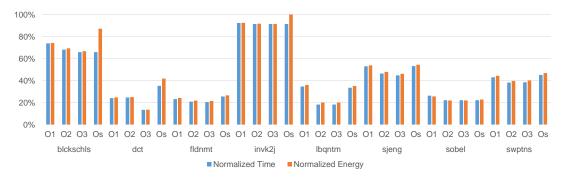

| 5.16        | Execution time and energy consumption of the application bench-                                                                                                                                                                                      |

| E 15        | marks for the different compiler optimization levels, relative to O0 102                                                                                                                                                                             |

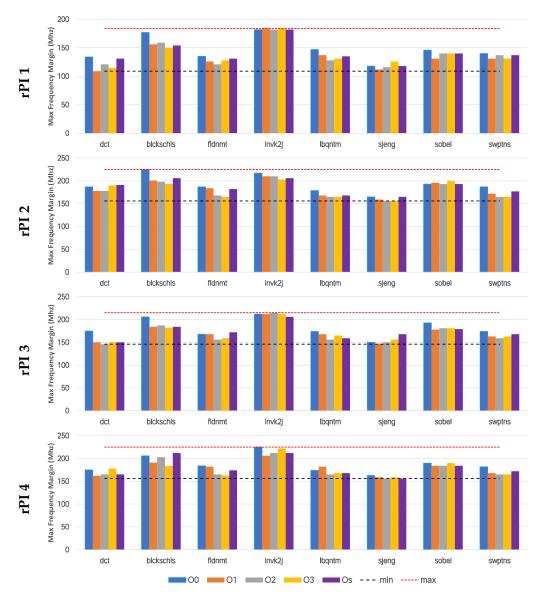

| 5.17        | Evaluation of $max f_{margin}$ settings for 8 benchmarks (1000 runs each)                                                                                                                                                                            |

|             | in each raspberry PI; the higher the bar, the wider the exploitable fre-                                                                                                                                                                             |

|             | quency margin. The horizontal dotted lines show the maximum (red)                                                                                                                                                                                    |

| 5 1 Q       | and minimum (black) values of $max f_{margin}$                                                                                                                                                                                                       |

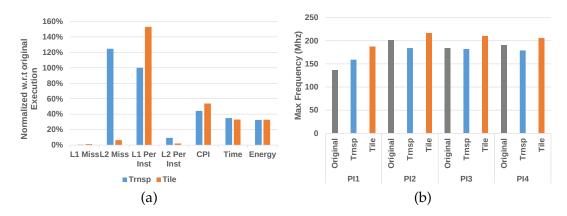

| 5.16        | and tiled MM versions, with respect to the original implementation.                                                                                                                                                                                  |

|             | (b) $maxf_{margin}$ for all raspberry PIs and all MM implementations 104                                                                                                                                                                             |

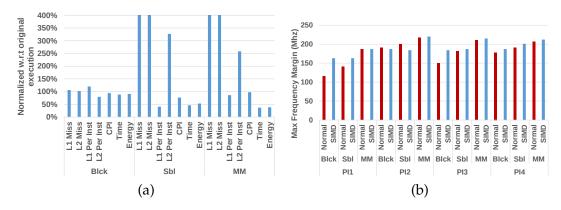

| 5 19        | (a) Normalized performance metrics and energy consumption of the                                                                                                                                                                                     |

| 0.17        | three benchmarks, with respect to the implementations without SIMD                                                                                                                                                                                   |

|             | instructions. (b) $maxf_{margin}$ for all raspberry PIs and benchmarks 105                                                                                                                                                                           |

| 7.1         | Vision of our approach. The applications and the computations should                                                                                                                                                                                 |

|             | provide information to the software stack about their quality/energy                                                                                                                                                                                 |

|             | requirements. Using this information the computations can be sched-                                                                                                                                                                                  |

|             | uled in hardware with different energy-reliability settings 119                                                                                                                                                                                      |

# **List of Tables**

| 2.1 | Lines of code (LOC) for the tasks and corresponding result-check and correction functions for each benchmark. The result-check functions |    |

|-----|------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | are implemented based on the original task code, which was modified                                                                      |    |

|     | to reduce its computational complexity.                                                                                                  | 30 |

| 2.2 | SlowRel and FastUnRel configuration settings used in our evalua-                                                                         |    |

|     | tion, and average fault rates of the $FastUnRel$ configurations                                                                          | 40 |

| 2.3 | Average task execution time in cycles (thousands), number of tasks                                                                       |    |

|     | executed reliably/unreliably, and number of voltage and frequency                                                                        |    |

|     | transitions, for each benchmark.                                                                                                         | 40 |

| 3.1 | Benchmarks used for the evaluation. For all cases, except Jacobi, the                                                                    |    |

|     | approximation degree is given by the percentage of accurately exe-                                                                       |    |

|     | cuted tasks. In <i>Jacobi</i> , it is given by the error tolerance in convergence                                                        |    |

|     | of the accurately executed iterations/tasks ( $10^{-5}$ in the native version).                                                          | 50 |

| 4.1 | Benchmarks used to characterize the voltage margins of the CPUs                                                                          | 61 |

| 4.2 | Characteristics of the workstations                                                                                                      | 62 |

| 4.3 | Most influential performance metrics for $V_{min}$ , as ranked by the MI                                                                 |    |

|     | algorithm.                                                                                                                               | 69 |

| 5.1 | Alpha instruction formats                                                                                                                | 85 |

| 5.2 | API to the run-time library of $XM^2$                                                                                                    | 93 |

| 5.3 | Raspberry 3B Specifications                                                                                                              | 97 |

| 5.4 | Different memory access patterns used by the source code transfor-                                                                       |    |

|     | mation case study                                                                                                                        | 01 |

| 5.5 | Brief Comparison between GemFI and XM <sup>2</sup>                                                                                       | 06 |

Dedicated to my family and friends

# Chapter 1

# Introduction

The scalability of semiconductor manufacturing process, as predicted by Moore's law, has been the driving force of the increase in the capabilities of computer systems. The 2013 International Technology Roadmap for Semiconductors (ITRS) report warns the public that CMOS, due to their constant scaling, will reach their atomistic and quantum mechanical physics boundaries in the next 3-12 years [47].

The scientific community is motivated to investigate novel designs which exploit heterogeneous technologies and emerging new information-processing paradigms. In contrast to the past, when technology was driven by the quest for higher performance, the primary goal of systems has shifted to optimize the power consumption/performance equilibrium.

## 1.1 The reality of power consumption

For over four decades Moore's Law, coupled with Dennard scaling [91] ensured the exponential performance increase in every process generation through device, circuit, and architectural advances. Up to 2005, Dennard scaling meant increased transistor density with constant power density. If Dennard scaling would have continued by the year 2020 [67], we would have approximately 40 times increase in energy efficiency compared to 2013. Unfortunately, Dennard scaling has ended because of the slowdown of voltage scaling due to slower scaling of leakage current.

The end of Dennard scaling has changed semiconductor industry dramatically. To continue the proportional scaling of performance and exploit Moore's Law, processor designers have focused on building multicore systems and servicing multiple tasks in parallel instead of building faster single cores. Even so, limited voltage scaling increasingly results in having a larger fraction of a chip unusable, commonly refer to as Dark Silicon [28]. It is expected by 2020 that only nine percent of the total number of transistors could be activated at any point in time due to tight power budgets [67].

To make things even worse, static and dynamic variations [13] result in adding voltage guardbands to ensure correct processor operation. The added guardbands increase energy consumption and force operation at higher voltage or lower frequency. They may also result in lower yield or field returns if a part operates at

higher power than its specification allows. The guardbands are becoming more prominent with area scaling, the use of more cores per chip, and core to core variations. The average power cost of these guardbands can be in the order of 35% [22]

For all these reasons, power consumption nowadays is a prime design parameter. If we need to go faster, we need to find ways to become more power efficient. For example, one of the major concerns of building the new generation of High Performance Computing (HPC) systems and overcoming the exascale barrier is power consumption. Such systems ideally would consume approximately 20 Megawatts and would maximize their performance by achieving greater degrees of parallelism. All other things being equal, if one design uses less power than another, then it has headroom to improve performance by using more resources or operating at a higher frequency. Simply put, a more energy efficient chip has headroom to provide more functionality and to service more tasks at given time frame.

### 1.2 Reliability and Power

Hardware designers go to great lengths to improve hardware reliability. They use guardbands in their designs against adverse combinations of factors that affect hardware reliability. This conservative design methodology essentially results in area, performance, power and energy overheads. Such design choices though, are not unreasonable as computation accuracy and hardware reliability have traditionally been primary concerns during the design of computing systems. After all, developers expect hardware to always behave in a reliable and predictable way. In the event that a hardware fault arises and manifests as an error in the software level it is treated as a rare scenario with developers actively spending effort to mask the errors from the user space, regardless of the magnitude of its effects.

In the terminology used in dependable and reliable operation of computer systems, a fault is an incorrect value within the internal state of the design of a system. A fault in the hardware level can result into errors and an error can result into a failure.

Possible sources of hardware unreliability are voltage droops, transistor variability, aging, temperature, or even alpha particles temporarily affecting hardware functionality. The traditional design technique addressing this problem also known as guardbanding, usually involves a combination of techniques, such as: i) higher supply voltage levels (voltage margins) ii) larger transistors iii) logic for error detection and correction iv) spare cells. Although, guardbands have successfully ensured correct operation up to date, their effectiveness in detecting and correcting all errors is questioned by researchers, as geometries and supply voltages are scaled down and circuits become more vulnerable to failures [124, 20, 111].

The extent of guardbanding that may be necessary to protect circuits against

all potential errors will lead to significant power overheads not sustainable by future systems, thus conflicting with power dissipation which is another major challenge of the semiconductor industry. Note that these guardbands are pessimistic, as they have to compensate for the worst case scenarios and combinations of non-determinism, switching patterns, temperature and aging effects. According to [22] the average power cost of guard bands is roughly 35%. However, most of the time, these guard bands represent mere overhead, as worst case scenarios and combinations will appear very seldom during application execution. The main reason for having these pessimistic guard bands and energy inefficiency is that modern computing systems execute programs under strict correctness requirements.

Guardbanding not only increases the power consumption of hardware but it implicitly limits its performance as well. For example, [28] warns that regardless of chip organization and topology, multicore scaling is power limited. A side-effect of this issue is that at the 7nm process node, more than 50% of the transistors in a general purpose processor will have to be powered off in every cycle. This is a trend that will be visible at larger scale as well. Even though, it will be possible to fit thousands of cores in the die it will be impossible to activate simultaneously more than a few tens or low hundreds [38].

The issue at hand is quite alarming. Even if future applications have the inherent parallelism to make efficient use of thousands of cores, the performance of our computing systems is going to be restricted due to the extreme power dissipation. In other words, unless we manage to design novel architectures, technology is bound to hit again the same power wall as single core architectures.

## 1.3 Design Space exploration

Assuming that the quality of the output is related to the reliability of the system, there is a need to rethink the design flow and propose abstractions that shift the reliability versus energy dissipation balance towards a design philosophy in which errors may be allowed to happen and safely ignored. To this direction one should consider and exploit opportunities presented at the hardware level as well as at the software level.

#### 1.3.1 Hardware Level

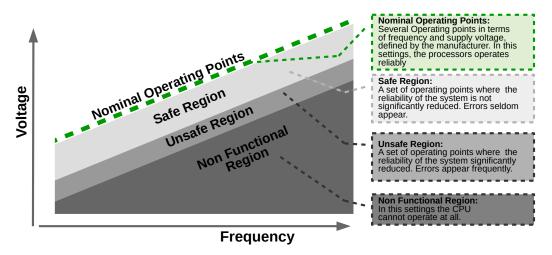

In figure 1.1 we present the possible operating points of a generic CPU. We briefly describe four different operational regions and discuss their trade-offs between energy and reliability:

**Nominal Operating Points.** Typically, a CPU manufacturer defines a finite number of operating points, called Nominal Operating Points (NOP) which guarantee error-less operation. These settings are the conventional operating points of modern CPUs. For the increased reliability the system designs needs to pay the overhead of the guardbands.

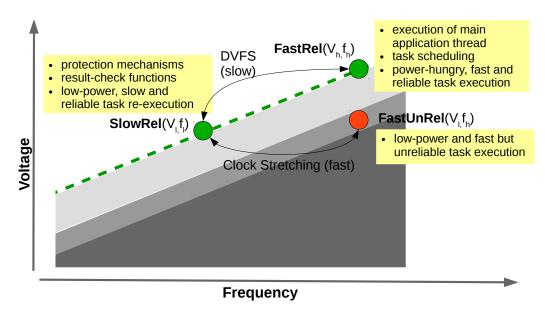

FIGURE 1.1: Description of the reliability of a generic CPU for different operating points in terms of supply voltage and frequency.

**Safe Region.** One can remove the voltage margins imposed by the guardbands, by decreasing the supply voltage, also referred as undervolting, or by increasing the operating frequency, also referred as overclocking, without reducing significantly the reliability of the system [95, 4, 5, 94, 74, 151]. In this region errors appear due to irregularities, which may appear only rarely or even not at all during the life cycle of a given processor. The energy reduction mainly depends on the magnitude of the margins.

**Unsafe Region.** It is possible, to perform even more aggressive undervolting or overclocking and operate in the unsafe region, where hardware starts to malfunction and produce timing errors during the execution time of a workload [11, 26, 22]. Since the voltage reduction is higher in comparison with the *safe* region, the energy gains are larger. However in these settings the errors occur frequently, therefore there is a need to add some protection mechanisms against these errors.

**Non Functional Region.** At this region the CPU is not operational at all as the majority of the paths within the netlist of the system experience timing violations.

#### 1.3.2 Software level

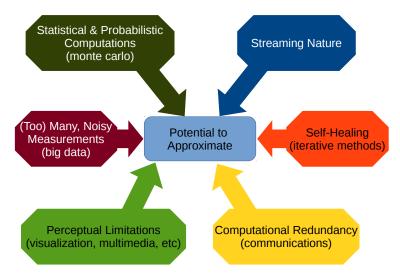

For a lot of applications, not all computations and not all data of the application are equally critical, requiring to be performed or maintained at 100% accuracy or correctness. Several application domains offer the opportunity to trade-off quality of output(QoO) for significant improvements in energy consumption. For such applications, it may be possible to only approximate the final output (or part of it), rather than computing the exact output result.

Typically such applications share a common property: they have relaxed accuracy constraints. In other words, they can accept a range of possible values as "correct". Figure 1.2 lists a few examples of application domains which have intrinsic

FIGURE 1.2: Application domains with intrinsic error resiliency.

error resiliency and are consequently approximation friendly. For example:

**Visualization applications** are amenable to approximations because their output is typically consumed by humans. Application developers can exploit the perceptual limitations of the human eye to approximate computations without inflicting noticeable quality degradation to their output.

Streaming applications are inherently amenable to approximations since they do not maintain a large state. They consume input data, perform computations, and produce output data. If an error occurs during the computation of a specific output data batch, the next batch will not be severely affected. In that sense, streaming applications inherently exhibit computational isolation.

Some **iterative methods**. For example, in the presence of errors iterative numerical methods still tend to converge to a correct solution but will typically require more iterations.

**Randomized computations**, If errors are random, the effect on these algorithm is part of the randomization process.

Approximate computing is an emerging paradigm, that allows a controlled decrease of the quality of the output for energy efficiency [6, 121, 149, 89]. Typically, approximate computing is used as a term to describe the disciplined aggressive optimization at the algorithmic level to gracefully trade-off computation accuracy with performance/energy efficiency.

A similar notion to approximate computing is *fault tolerant computing* in which the underlying hardware may exhibit unexpected behaviour such as computation errors, crashes, or even infinite loops. This uncertainty/unreliability can be the result of a wide variety of causes. It may be due to unreliable execution on energy efficient substrates, or even hostile environments such as space (alpha particles, cosmic rays, solar wind flux, etc). In any case, maintaining acceptable levels of reliability and maintaining an acceptable quality of the output while executing code using unreliable hardware requires the use of fault tolerance techniques. Although both

paradigms exploit similar features to achieve energy efficiency they demonstrate large differences. Approximate computing is controlled and predictable. A developer consciously designs an approximate version of the code and/or uses hardware with reduced precision. On the other hand, execution under unreliable conditions is less predictable and typically requires the application of fault tolerant computing techniques. For example, the developer should detect and correct errros before they irreversibly contaminate the application state.

One factor that contributes to the energy footprint of current computer technology is that all parts of the program are considered to be equally important, and thus are all executed with full accuracy. However, as shown by previous work [73], in several classes of computations, not all parts or execution phases of a program affect the quality of its output equally. In fact, the output may remain virtually unaffected even if some computations produce incorrect results or fail completely. Significance-aware computing [61, 90] exploits the algorithmic property of computational significance to create optimization opportunities in terms of performance and power-efficiency of applications.

#### 1.3.3 Significance Definition

A formal definition of significance can be provided as follows. Assuming code that implements the function  $y=f(\vec{x})$ , where  $\vec{x}$  is the vector of the function inputs, the significance of  $\vec{x}$  to the output y can be defined using interval arithmetic [92] and first order adjoint analysis. The range of possible input values is the input interval vector  $[\vec{x}]=[\vec{x},\overline{\vec{x}}]=\{\vec{x}\in I\!\!R^n|\underline{\vec{x}}\leq \vec{x}\leq \overline{\vec{x}}\}$ , and an evaluation of f in interval arithmetic is obtained by replacing all variables and intermediate elementary functions  $\phi$  with their interval version. The significance of an input element  $x_i\in\vec{x}$  to the final result y is equal to

$$S_y(x_i) = w([x_i] \cdot \nabla_{[x_i]}[y])$$

where  $w(\cdot)$  is the width of the interval. The first order derivative  $\nabla_{[x_i]}[y] = \frac{\partial f[\vec{x}_i]}{\partial [x_i]}$  is the derivative of the function result [y] with respect to the input variable  $[x_i]$ . In other words, the bounds of interval derivative  $\nabla_{[x_i]}[y]$  are the steepest downward and upward slopes, respectively, of  $y = f(\vec{x})$  in the interval  $[x_i]$ , which quantify the impact of all possible values from  $[x_i]$  on the final result y. If the range (width) of  $S_y$  is large, then  $x_i$  strongly affects the value of y. As such, the code that produces the value of  $x_i$  is highly significant for the accuracy of the final output y. More information on the algorithmic property of significance and a methodology for determining the significance of computations automatically can be found in [141].

#### 1.4 Contributions

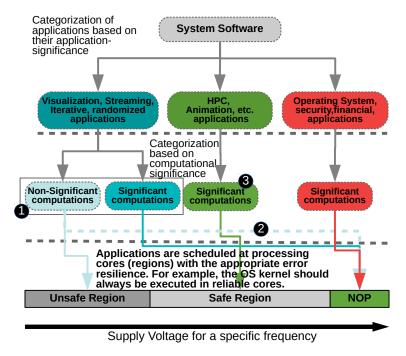

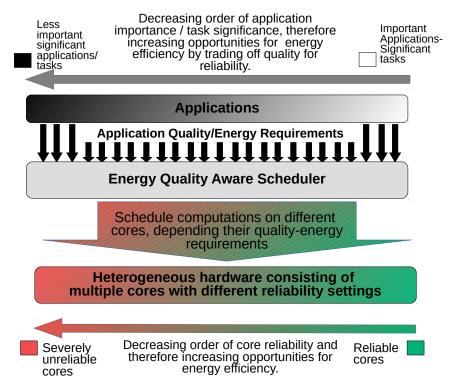

The granularity of *significance* is not bounded in the spectrum of a single application, but it can be projected to the entire software stack. For example, the Operating

FIGURE 1.3: Vision of our approach. Applications should be categorized based on their contribution to the output quality. Using this information the applications should be scheduled in hardware with appropriate levels of reliability.

System (OS) is more important (significant) than a media application, as an error corrupting the OS could propagate to multiple applications making the entire system unstable. Likewise, a security application is more significant than a gaming application. Using a similar reasoning the quality of the output can be projected to the entire software stack, where the quality of the system takes into account all the applications within the system. This vision is depicted in figure 1.3.

This PhD dissertation aims at improving power and energy efficiency by exploiting the correctness/reliability opportunities presented both in the software level and the hardware level. Applications which can tolerate quality degradation use significance-driven approach, which aims to gracefully trade-off application output quality with improved energy efficiency by forcing the CPU processor to operate on an unsafe region (Figure 1.3 black circle 1).

The significance-driven approach can be also exploited in *approximate* computing, in which alternative more energy efficient approximate versions of the non-significant computations are scheduled for execution in Nominal operating points (Figure 1.3 black circle 2).

In any case though the significance-based computing model is not suited for all applications. For instance, the significance of computations may be highly input-dependent, hard to specify at design time and difficult or costly to extract even at run time. Also, some programs may require all tasks to be executed without inaccuracies. To this direction in this these we achieve energy efficiency by executing applications in the *safe* operational region of CPUs. In which errors are not expected to happen, but pose a rare event(Figure 1.3 black circle 3).

Finally, this PhD dissertation distributes the responsibility for energy efficiency and reliability in various design layers starting from the circuit all the way to the application layer, where available slack in output QoS can be reduced to increase energy efficiency. The realization of such a system requires modeling of the effects of potential hardware misbehaviour induced by various sources and also tools that can easily propagate such effects. To this direction, we designed, implemented and deployed experimental frameworks, which are used to study the trade-offs between energy/power efficiency and execution resilience (both in terms of quality of output and execution resilience).

The next sections describe the contributions in greater detail.

#### 1.4.1 Significance Aware Computing

We investigate significance aware computing, based on the premise that specific phases of a computation may incur a high toll on performance and energy without the corresponding contribution to the quality of the result.

For example, Discrete Cosine Transform (DCT), a module of popular video compression kernels, which transforms a block of image pixels to a block of frequency coefficients, can be partitioned into layers of significance, owing to the fact that human eye is more sensitive to lower spatial frequencies, rather than higher ones. By explicitly tagging operations that contribute to the computation of higher frequencies as less-significant, one can leverage smart underlying system software to trade-off video quality with energy and performance improvements. Significance aware computing aims to exploit regions of an application which are amenable to aggressive optimizations that do not severely impact the final application outcome but lead to improvements in energy/power/performance.

There is need for an intuitive programming model which is user-friendly but also offers the necessary expressiveness and functionality to address all of the key challenges of the signifiance aware paradigm. To this direction, we introduce a programming model which extends the OpenMP, one of the most popular parallel programming models, and provides the following main features:

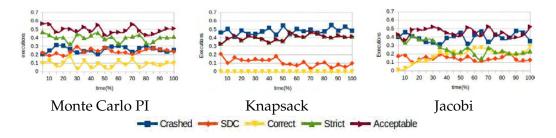

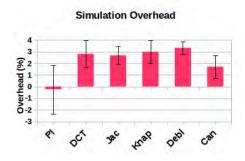

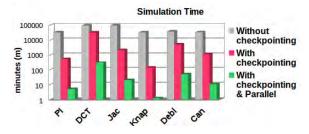

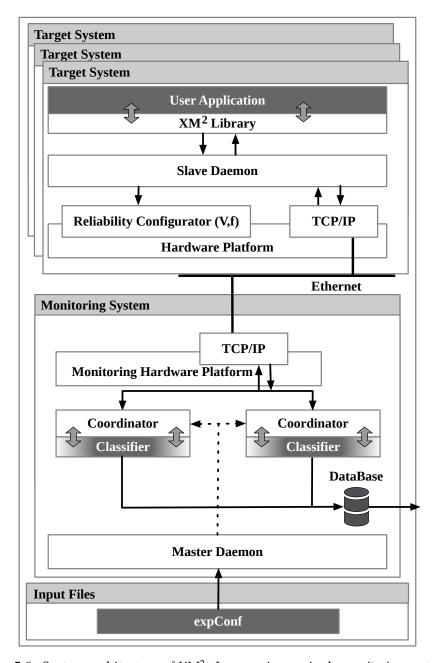

**Significance Characterization:** The developer can specify the significance of different parts of the computation based on how strongly each part contributes to the quality or correctness of the end-result.