# University of Thessaly, School of Engineering Department of Electrical and Computer Engineering

# **Diploma** Dissertation

**Title:** "Graphical Representation of Standard-Cell Placement, a placement visualization tool"

Student's Name: George Stergioulas

Supervisor: Prof.: Georgios Stamoulis Assistant: M.Sc.: Ioannis Arvanitakis

Date: October 2013

#### **Preface and acknowledgements**

The following dissertation introduces a tool for the visual representation of the standard cells position within a chip area. It analyzes the placement problem in theory and the software design and functionality, acting also as a user's manual for the aforementioned tool.

This dissertation was made possible thanks to the idea and support of prof. Georgios Stamoulis and the invaluable assistance of MSc graduate Ioannis Arvanitakis. I was searching for a subject relevant to graphics, and the VEDA Laboratory of the Department of Computer and Communications Engineering at the University of Thessaly happened to work on placement algorithms development.

One of the design tools developed at the VEDA Laboratory needed a graphics interface so I started developing graphics for hardware design, leading to this dissertation. The finished result is a stand-alone GUI that can parse and draw the cell positions within a chip, after it has been provided with the appropriate data.

Finally I would like to express my gratitude to everyone that helped me reach this point, from fellow students and friends to professors. A separate thanks is also appropriate for Maria, whose support and guidance made all this possible.

2

### **Table of Contents**

| 1. Prefacepage 2                                         |

|----------------------------------------------------------|

| 2. Table of Contentspage 2                               |

| 3. A story about graphics, CAD and EDApage               |

| 4. The placement problem definitionspage 19              |

| 4.1. Definitionspage 19                                  |

| 4.2. Computer Aided Designpage 21                        |

| 4.3. Electronic Design Automationpage 2                  |

| 4.4. Design Flowpage 23                                  |

| 4.4.1. Front-end flowpage 25                             |

| 4.4.2. Back-end flowpage 20                              |

| 5. The visualization toolpage 3                          |

| 5.1. File types that the tool usespage 3                 |

| 5.1.1. Input files for the algorithmpage 3               |

| 5.1. 2. Output files that are used by the toolpage 32    |

| 5.2. Benchmark Circuitspage 34                           |

| 5.3. Possible future upgrades and expansion ideaspage 34 |

| 5.4. Technology, problems and solutions appliedpage 35   |

| 5.5. User guide to the toolpage 38                       |

| 6. Appendix   | page 50 |

|---------------|---------|

| 7. References | page 71 |

### 3. A story about graphics, CAD and EDA.

One of the most notable advances in computers in the past years must have been the way we perceive the information. From the command line interfaces of the early 80's, to the full-blown 3D games and interfaces.

Computer graphics by definition are in fact those generated from computers, but also the representation of image data using a computer system, with the assistance of specifically designed hardware and software.

This technology has led to the revolution of animation, movie production and of course the video game industry. Computers began as bulky monochrome boxes and forty years later they now fit in the palm of our hands, producing extreme computational power and impressive life-like graphics in real time. This is all relevant to the need for better and more sophisticated hardware design tools. Processors with billions of transistors keep reducing in size. They are becoming more and more efficient, as well as cheaper. The future lies in the advances of embedded systems and mobile computing rather than big power-hungry desktops and the immersive technologies for seamless interaction with the virtual environments and augmented reality applications. This is what makes efficient and effective chip design techniques so important. More computational power is needed from smaller systems.

5

Some milestones in the development of graphics technologies and the way we interact with computers are shown below.

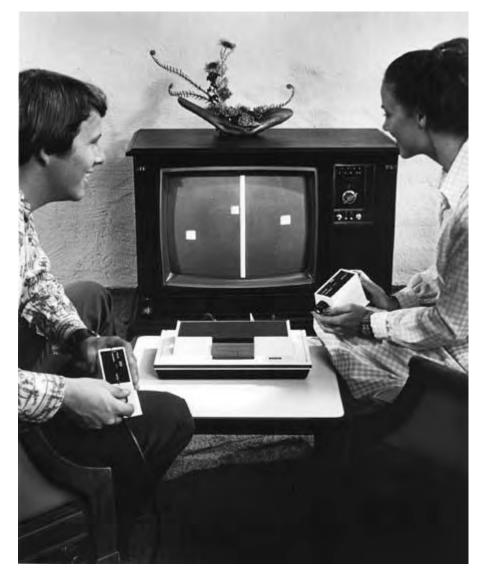

Picture 3.1

The original "Pong" game, 1972. The first mainstream video game in the world, by Atari.

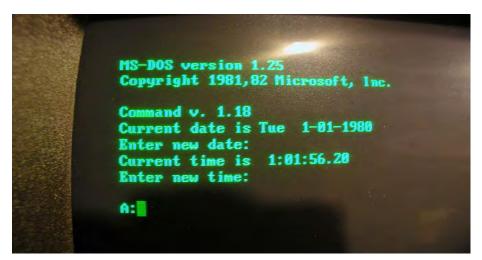

Picture 3.2

10 years after "Pong", this command line interface on a monochrome screen is still the only way to interface with a

computer

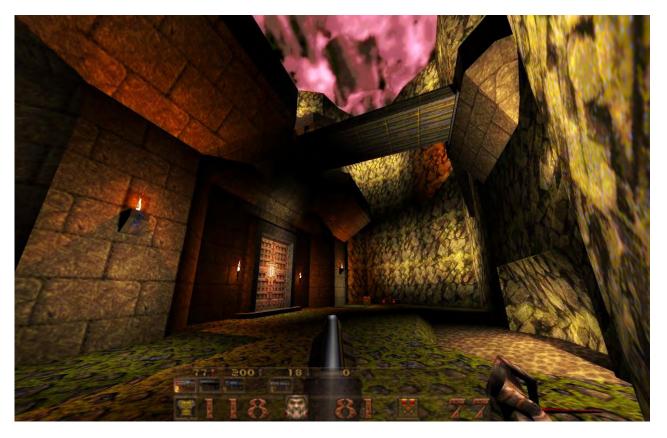

Picture 3.3

The year is 1996, and the world is presented with the first fully three dimensional game using graphics acceleration for the home computer. Quake is about to revolutionize the game industry and create a market for the graphics hardware industry as well.

The images above show the revolution that graphics brought to our world, and how fast and exponentially the whole technology evolved. From the 90's it only takes ten years for things to really take-off. Graphics hardware becomes impressively more powerful with every new generation affecting the world in multiple aspects. From the unmanned military drones to the entertainment industry, graphics technologies open up new possibilities.

#### Picture 3.5

In-game unedited screenshot showcasing how far graphics have come, from the "Project Cars" driving simulator. Currently in early development stage it will be available within the current year for home PC's.

The "Ironman" movies franchise, relies heavily on computer effects to create the immersive atmosphere. It also shows a plausible idea of how humans could interact with computers in the coming years.

#### Picture 3.6

This introduction leads us to the Graphical User Interface. In computing, graphical user interface (also known as "GUI") is a type of human-computer interface that allows interaction with devices through graphical icons, windows, menus and visual indicators that can be manipulated by a mouse, as opposed to text-based interfaces, typed command labels or text navigation. GUIs were introduced in reaction to the perceived steep learning curve of command-line interfaces (CLI), which require commands to be typed on the keyboard. GUIs can also be manipulated by a keyboard although to a more limited extend. A window in a GUI is a part of the screen that can display information independently from the rest of the screen. Windows can open simultaneously and independently so that the user can organize the information within the space available on the screen. This space is usually called the desktop.

The actions in GUI are usually performed through direct manipulation of the graphical elements. Besides in computers, GUIs can be found in hand-held devices such as mobile phones, portable media players, gaming devices, household appliances, office, and industry equipment.

11

#### Picture 3.7

Command-line interface vs the latest Android touch interface

All of the above lead us closer to what this dissertation is about. GUI made the idea of Computer Aided Design or CAD possible. The definition of CAD according to <u>wikipedia</u> is the use of computer systems to assist in the creation, modification, analysis, or optimization of a design. CAD software is used to increase the productivity of the designer, improve the quality of design, improve communications through documentation, and to create a database for manufacturing. CAD output is often in the form of electronic

files for print, machining, or other manufacturing operations. Computer-aided design is used in many fields. Its use in electronic design is known as Electronic Design Automation, or EDA.

More about the history of CAD and EDA is to be found in the following chapter.

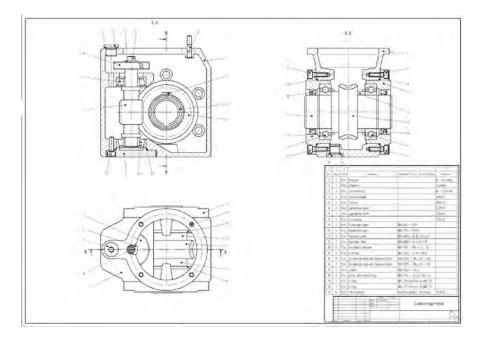

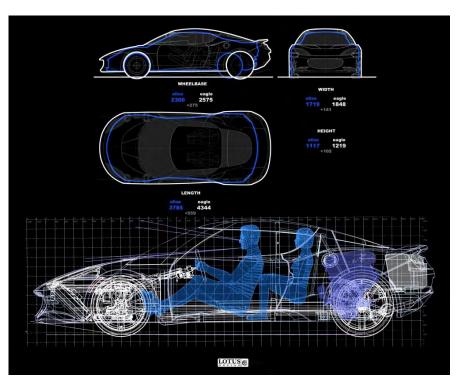

Picture 3.8

Picture 3.9

Picture 3.11

Electronic design automation (EDA or ECAD) is a category of software tools for designing electronic systems such as printed circuit boards and integrated circuits. The tools work together in a design flow that chip designers use to design and analyze entire semiconductor chips. (wikipedia)

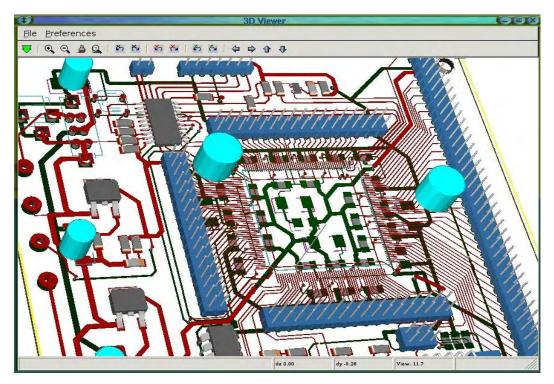

Picture 3.11

3D PCB layout

Picture 3.12

| plications Places System   |                                                                                                                |                                |                         | 991                                     | Sun 30 Dec, 7:15 PM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|----------------------------|----------------------------------------------------------------------------------------------------------------|--------------------------------|-------------------------|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| robot-io.sch - gschem      |                                                                                                                | THE TE OF GO                   | per Viewert 1.0-pre:    |                                         | and the second se |

| File Edit Buffer View Page | Add Hierarchy Attributes                                                                                       | Options Help                   | View Analyze Jools E    | (elp                                    | A REAL PROPERTY AND INCOME.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                            |                                                                                                                |                                | S 2 4 4                 | Q Q Q I I I I I                         | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                            |                                                                                                                | Lave                           | rs Messages             | ×1.1.1. 10.1.1.1.1.1.1                  | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                            |                                                                                                                |                                | lay method: Norma +     |                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                            |                                                                                                                |                                | output back.gbr         |                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| CONVILM                    | CONN2_F SEL                                                                                                    |                                | outout front.gbr        | a.                                      | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| -                          |                                                                                                                |                                | plated_drill.cnc        | 888888888888888888888888888888888888888 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 0 3                        | 0 0 0 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1                                                                        |                                |                         |                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| e 0 2                      | 0.2.                                                                                                           | 2.81                           |                         | 000000000000000000000000000000000000000 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 0.4                        | 0 4. ibr                                                                                                       |                                |                         | 000000000000000000000000000000000000000 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 0 2                        | 0 9                                                                                                            |                                |                         | 3. 000000000000000000000000000000000000 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                            | -0+                                                                                                            |                                |                         | 000000000000000000000000000000000000000 | -0 000 222122                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                            |                                                                                                                |                                |                         | 00000000000                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| -                          |                                                                                                                |                                |                         |                                         | 000000000000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                            | MOP                                                                                                            |                                |                         | 00000000000                             | 000000000000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| A In DA                    |                                                                                                                | rocessor add-on IC connections |                         | 000000000000                            | 000000000000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| gEDA - File Browser        | the second s |                                |                         |                                         | 00000000000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Ele Edit View Go Bookmark  | s Help                                                                                                         |                                |                         | 00000000000                             | 00000000000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                            | 0 0                                                                                                            | Select                         |                         | 00000000000                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Back Forward Up            | Stop Reload                                                                                                    | Home                           |                         | 1 00000000000                           | 00000000000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Location: /home/pcjc2/gl   | EDA 9 100% 9                                                                                                   | Te robel osch2ocb              | theorem in the state of | 000000000000000000000000000000000000000 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| REF. FRANK                 |                                                                                                                | 1 1                            | 🖻 🗙 🔶                   | 0000 0000                               | 00000000000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| . 50                       |                                                                                                                | Quit New Open                  |                         |                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| circuit.cmd circuit.g      | sch2pcb circuit.net                                                                                            | Schematic pages                | Layout                  |                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 100                        | -                                                                                                              | robot-io.sch                   | robot.pcb               |                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                            | (무역)                                                                                                           | robot-i2c.sch                  | Edit layout             | 02.8, 1212.0) mil •                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                            | 2c.sch circuit-io.sci                                                                                          |                                | Update layout           |                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| circuit.pcb circuit-       |                                                                                                                |                                |                         |                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| circut-pco circut-         |                                                                                                                |                                |                         | 2017 St. 35 St. 25 C                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                            | Dack.gbr plated drill.c                                                                                        | nc Add Bernove                 | 2                       |                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| outout_front.gbr output_t  | Dack.gbr plated_drill.c                                                                                        | nc                             |                         |                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

PCB layout and schematic for connector design

| [/home/diego/cvs/                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | fpgatools/s2proto/s2proto.sch1                                                                                                                                              |                                       |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|--|--|--|--|

| Eile Preferences Help                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                             |                                       |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                             |                                       |  |  |  |  |

| Image: Section of the section of t | JP4_15 7:<br>CCLK<br>ODONE<br>J/INIT<br>FPGA<br>TD0 FPGA<br>TD0 FPGA<br>TD0 FPGA<br>TD0 FPGA<br>TD0 FPGA<br>TD0 FPGA<br>TD0 FPGA<br>CLOU<br>DM<br>D0/DIN<br>File s2proto-fp |                                       |  |  |  |  |

| · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                             | · · · · · · · · · · · · · · · · · · · |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                             |                                       |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Z 4 X 5.5500 Y 1.0000 x -0.3000 y -2.1330                                                                                                                                   | Inch                                  |  |  |  |  |

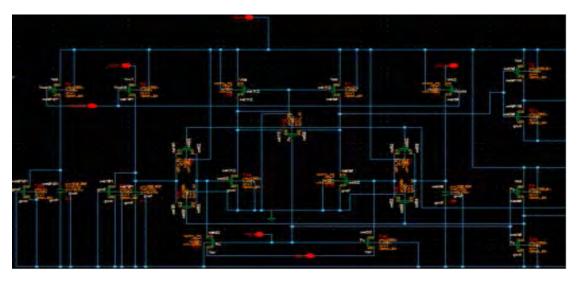

Picture 3.13

Schematic capture program

Design of Sense Amplifier circuit using Cadence Spectre tool.

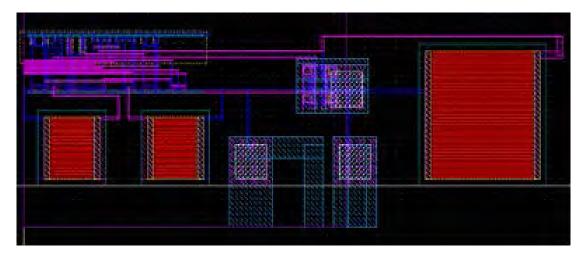

Picture 3.15

Layout of charge sharing measurement circuit using the Cadence Virtuoso layout tool.

Picture 3.16

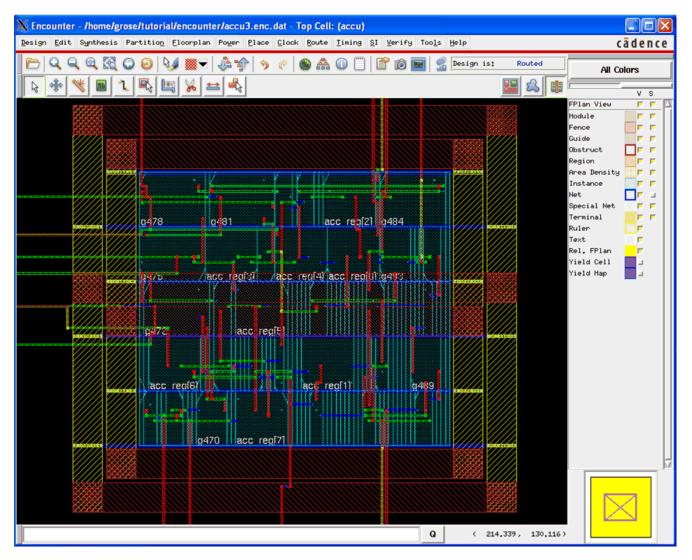

Cadence SOC Encounter

### 4. The placement problem definitions

#### **4.1 Definitions**

Integrated Circuit (IC): or monolithic integrated circuit (also referred to as chip, or microchip) is an electronic circuit manufactured by the patterned diffusion of trace elements into the surface of a thin substrate of semiconductor material. [wikipedia] Very-Large-Scale Integration (VLSI): is the process of creating integrated circuits by combining thousands of transistors into a single chip. [wikipedia]

Application-Specific Integrated Circuit (ASIC): is an IC customized for a particular use, rather than intended for general-purpose use. [wikipedia]

Standard-cell library: is a collection of low-level logic functions such as AND, OR, INVERT, flip-flops, latches, and buffers. These cells are realized as fixed-height, variablewidth full-custom cells. The cells are fixed-height, variable-width full-custom. The fixedheight enables them to be placed in rows. [wikipedia]

Integrated circuit layout: also known IC layout, IC mask layout, or mask design, is the representation of an integrated circuit in terms of planar geometric shapes which correspond to the patterns of metal, oxide, or semiconductor layers that make up the components of the integrated circuit. [wikipedia]

Core area/Die area: Core area is the area of silicon needed for the cell placement. Die area is the whole silicon area of the chip, as these areas may differ. Module: is defined as a block of cells, other modules or macros. The most used style is the standard cell layout because of its fixed height of the modules that decrease the time complexity and memory allocated for placement algorithms, which for big circuits of 10000000 gates is critical.

There are five major styles of layout:

*1. Gate array:* The gate array design consists of prefabricated silicon with identical modules distributed evenly on the real-estate. The function of a module is determined solely by its connections. Therefore the entire logic is determined by the wires. Space has been reserved for routing

*Sea-of-gates:* The sea-of-gates layout is similar to gate array, but no space is reserved for routing. Instead the entire real estate has been filled with preferable transistors. Some of the transistors become unusable however since space must still be allocated for routing.

*Standard-cell:* is a collection of low-level logic functions such as AND, OR, INVERT, flip-flops, latches, and buffers. These cells are realized as fixed-height, variable-width full-custom cells. The cells are fixed-height, variable-width full-custom. The fixed-height enables them to be placed in rows. Originally routing was done between rows but multilayer technology now allows for routing anywhere on the real-estate.

*4. Mixed-cell:* The mixed-cell model is similar to standard-cell layout, but allows large modules in the layout which may very is height and width

20

*5. General-cell(Macros):* The final layout style which is also the only full-custom is the general-cell layout style. In this case modules are allowed any size and position on the real estate.

Overlap: Two modules overlap with respect to placement if the upper right corner coordinates of the first are smaller than the lower left corner of the second.

Legal placement: A placement is legal when the following constraints are met: There is no overlap between modules

All modules are within the core area

#### **4.2 Computer Aided Design**

Computer Aided Design (CAD) is the use of computer systems to design detailed physical objects, through the entire research and development process, thus for the creation, modification, analysis, optimization and final draw of a design. CAD software was created to assist the designer, deal with more complex designs, reduce their faults, and decrease the completion time. Moreover, the designer is allowed to keep documentations and create databases for manufacturing. CAD output is often in the form of electronic files for print or machine operations.

CAD involves all the information needed for the manufacturing process, such as shapes, materials, processes, dimensions and tolerances according to application-specific

conventions. Furthermore it may be used to design curves and figures in two-dimensional (2D) or three-dimensional (3D) space.

Nowadays, the number of industries turning to CAD is growing, because of its benefits such as lower cost of product development and a shortened design cycle. CAD software is extensively used in many applications such as automotive, shipbuilding, aerospace and microelectronic industries, industrial and architectural design. Those are the reasons of why the computer aided design has become an especially important technology within the scope of computer-aided technologies. It is one of many tools used by engineers and designers and is used in many ways depending on the profession of the user and the type of software in question.

#### **4.3 Electronic Design Automation**

Electronic Design Automation (EDA or ECAD) is a category of CAD tools for designing electronic systems such as printed circuit boards and integrated circuits. Before EDA, integrated circuits were designed by hand and manually laid out. The earliest EDA tools were produced academically. By the mid-70's the first EDA tools for placement and routing were developed. One of the most famous was the "*Berkeley VLSI Tools Tarball*", a set of UNIX utilities used to design early VLSI systems. The beginning of industrial EDA was at 1981, as the larger electronic companies pursued EDA manually until then. Now EDA tools work together in a design flow that designers use to design and analyze entire semiconductor chips.

EDA led to the development, massive production and cost reduction of high-tech conveniences such as cell phones, navigation systems, media players etc. Nowadays EDA has an extraordinary effect on human life, as almost everything and every daily task have been influenced by this. The progression of microprocessor technology in terms of performance and features made the computer an essential tool and part of everyday life. EDA has increased importance in the latest years, with the continuous scaling in semiconductor technology, because with the DSM era there are a lot of problems to be faced. Some of them are Design for Testability (DFT) and Automatic Test Pattern Generation (ATPG), lithography etc. Moreover, the evolution of the tools is necessary in order to overcome the difficulties of this era.

#### **4.4 Design Flow**

Design flows are the explicit combination of EDA tools to accomplish the design of an integrated circuit. Moore's Law has driven the entire IC implementation RTL to GDSII design flows from one which uses primarily standalone synthesis, placement, and routing algorithms to an integrated construction and analysis flows for design closure. [wikipedia]

Due to the progress being made by the semiconductor industries, e.g. the transistors' scaling, reducing the interconnection delay has become the great challenge. This fact led

to a new way of thinking about integrating design closure tools and new scaling challenges for the current state of the art tools uprised, such as leakage power, variability, and reliability. There are two discrete flows for ASIC and FPGA designs. This thesis is based on the ASIC flow.

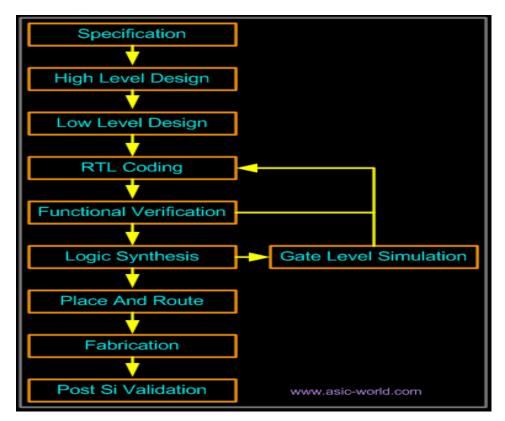

As mentioned above all EDA tools work together in a design flow that chip designers use to design and analyze entire semiconductor chips. In this section is described a typical design flow, as there are some variations, e.g. for low-power design. Picture 4.1, below, illustrates the ASIC flow.

Front-end and Back-end flow(asic-world.com)

The whole process it can be separated in 2 domains: Front-end flow

Back-end flow

#### 4.4.1 Front-end flow

The Front-end flow is the process that guides from the concept to the netlist of logic-gates of a circuit. It includes steps, such as architectural design, simulation and synthesis. The front-end flow finishes at the Logic Synthesis step as depicted in the picture 4.1.

Specification: The step at which are described important parameters of the design, e.g. what the design should do.

High-level design: Various blocks are defined and description of the communication between them. Description is given in high-level languages (SystemC, C, C++).

Low-level design: It is described how each block is implemented. It contains details about FSMs, counters, registers etc.

RTL coding: The step at which Low-Level design is converted into Verilog / VHDL code, using synthesizable constructs of the language.

Functional Verification: It is verified that the design does its expected function. Testbenches are created to apply all possible stimuli at the input and check the output. Logic Synthesis: Is the process in which synthesis tools take RTL code, target technology and constraints as inputs and maps the RTL to target technology primitives. After the gate-level netlist is created, timing analysis is done to check that the mapped design is meeting timing requirements.

Gate-level Simulation: Check if the Design Under Test (DUT) is functionally correct.

Before passing the netlist to the back-end flow, usually it is done Formal verification and insertion of scan-chains.

Formal verification: Check if the RTL to gate mapping is correct Scan-chain insertion: Insert scan-chain in case of ASIC for design-fortestability(DFT) [asic-world]

#### 4.4.2 Back-end flow

Back-end flow or physical implementation is the step in the standard design cycle which follows after the Front-end. At this step, circuit representations of the components (devices and interconnects) of the design are arranged on a piece of semiconductor material. More specifically they are converted into geometric representations of shapes which, when manufactured in the corresponding layers of materials, will ensure the required functionality of the design. The next step after Physical Design is the Manufacturing process or Fabrication Process that is done in the Wafer Fabrication

Houses.

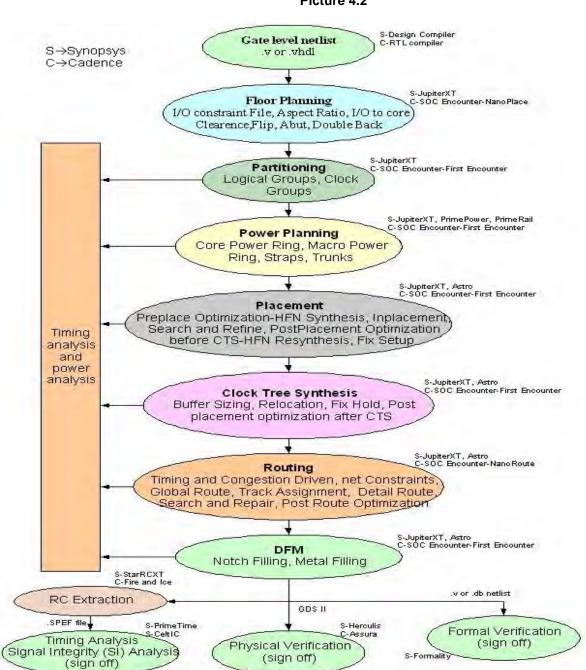

The main steps of the back-end are described in picture 4.2.

Picture 4.2

Detailed back-end design flow with EDA tools and file format

Gate-level netlist: Is the circuit's synthesized netlist, produced after the completion of the front-end flow. It includes only standard-cells and their interconnections, as well and primary inputs and outputs of the circuit.

Floorplanning: Is the process in which the area of the design, the IO structure and the aspect ratio are decided. The usual process is to find structures that should be placed close together, and allocates space for in order to meet the, sometimes, conflicting goals of available space (cost of the chip) and the required performance. During this process some components such as the macro's used in the design, memory, other IP cores and their placement needs, the routing possibilities and also the area of the entire design (core area/die area), are taken into account in order to find the most suitable place for them, as these components can have a dramatic effect on the performance of the chip.

Partitioning: Is a process of dividing the chip into small blocks. This is done mainly to separate different functional blocks and also to make placement and routing easier. Partitioning can be done in the RTL design phase when the design engineer partitions the entire design into sub-blocks and then proceeds to design each module. These modules are linked together in the main module called the TOP LEVEL module.[wiki]

Placement: Is the process of placing the modules of the design, described in the gate-level netlist, in the core area decided in the floorplan step.

Clock-Tree Synthesis (CTS): Before CTS, clock is not propagated and considered ideal. Clock tree begins at source clock and ends at pins of a flop.

Routing: There are two types of routing in the physical design process, global routing and detailed routing. Global routing allocates routing resources that are used for connections. Detailed routing assigns routes to specific metal layers and routing tracks within the global routing resources.[wiki]

Signoff: Checks the correctness of the layout design, before it can be taped-out. There are several categories of signoff checks:

- DRC Also known as geometric verification, this involves verifying if the design can be reliably manufactured given current photolithography limitations. In advanced process nodes, Design-for-Manufacture (DFM) rules are upgraded from optional (for better yield) to required.

- *LVS* Also known as schematic verification, this is used to verify that the placement and routing of the standard-cells in the design has not altered the functionality of the constructed circuit.

*Formal Verification* - The logical functionality of the post-layout netlist is verified against the pre-layout, post-synthesis netlist.

*Voltage-drop analysis* - Also known as IR-drop analysis, verifies if the power-grid is strong enough to ensure that the voltage representing the binary high value never dips lower than a set margin.

*Signal-integrity analysis* - Noise due to crosstalk and other issues is analyzed, and its effect on circuit functionality is checked.

*Static-timing analysis (STA)* - Is used to verify if all the logic data paths in the design can work at the intended clock-frequency.

*Electromigration lifetime checks* - To ensure a minimum lifetime of operation at the intended clock frequency without the circuit succumbing to electromigration.

Once the design has been physically verified, optical-lithography masks are generated for manufacturing. The layout is represented in the GDSII stream format that is sent to a semiconductor fabrication plant (fab).

### 5. The visualization tool

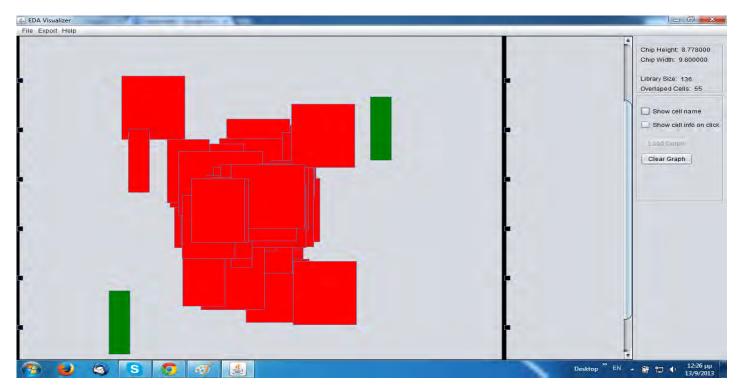

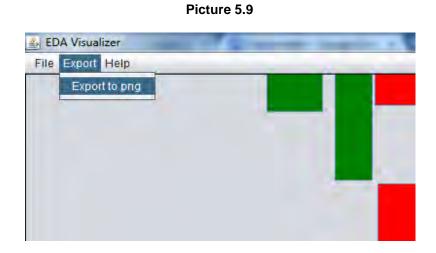

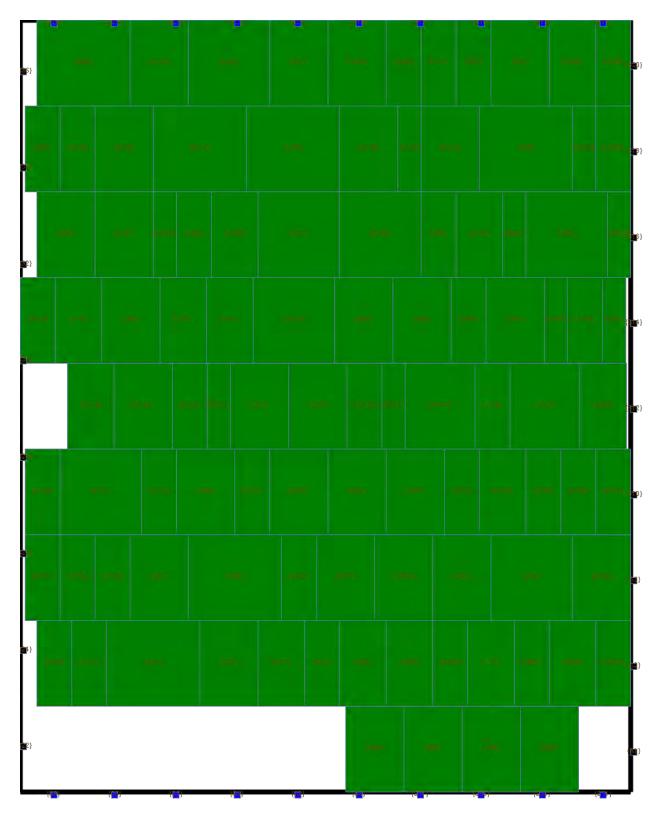

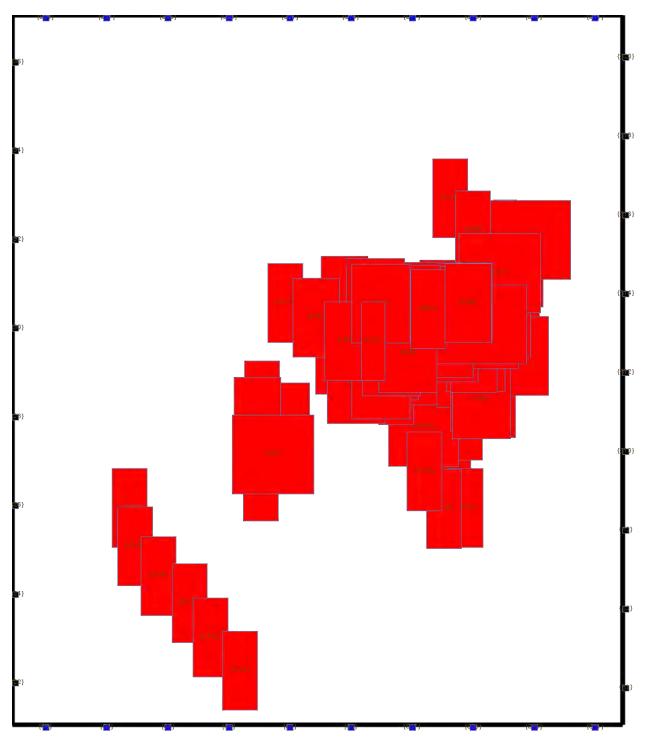

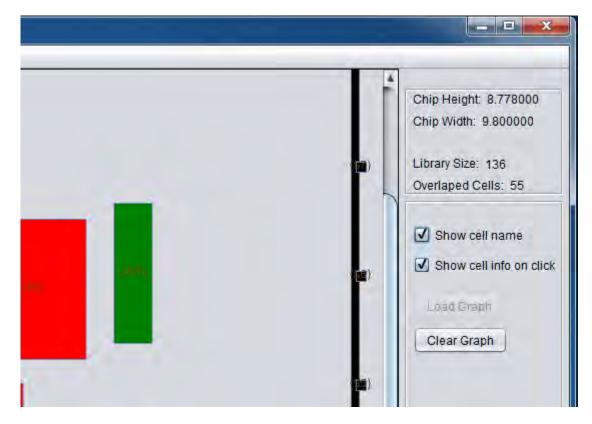

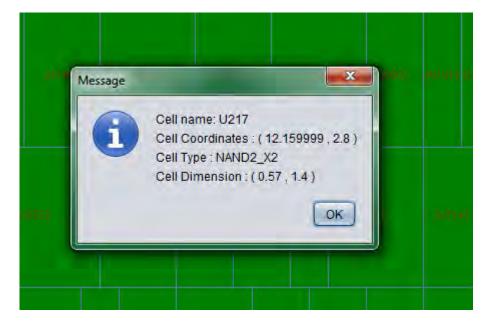

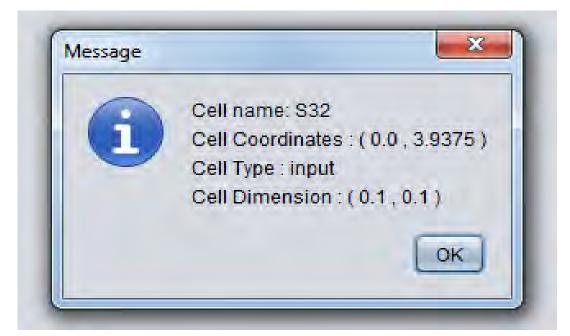

This tool was conceived in order to represent with graphics the cell placement within a chip area. It uses data parsed from other tools like Cadence, and visualizes the data for an easy to understand image of the positions of the cells within the usable area. This makes it easier to assess the optimal positions of the cells, with colors distinguishing the unwanted overlapping cells and also a point of reference for the free space in the chip. Finally it provides information for each cell (type and size) and the option to export the full sized image of the chip to .png files.

#### **5.1** File types that the tool uses

#### 5.1.1. Input files for the algorithm

The input of the algorithm we developed is according to the standards being used by industrial placement tools and described in the previous chapter.

- Verilog netlist

- Technology library: Nangate 45nm Open Cell Library, which is an open cell library

- I/O pin placement: The positions of I/O pins are being placed randomly by the algorithm or a file that described their position can be given as input.

#### 5.1.2 Output files that are used by the tool

The output of our algorithm is a .txt file that describes the final position of the cells of the IC. They are constructed in order to simplify the data inside the file and avoid working with VERILOG files, making it more accessible should one try to study them without a visualization tool.

The file structure is as follows:

• The dimensions file for each chip only has the height and width of the chip area. For example the dimension file for the S27 chip is this:

chip height = 5.600000 chip width = 5.538500

• The library size file for all the chips comprises of three columns. The type of the

cell and the size of the cell in X and Y coordinates:

| (std-cell Type) | Х        | Y        |

|-----------------|----------|----------|

| AND2_X1         | 0.760000 | 1.400000 |

| AND2_X2         | 0.760000 | 1.400000 |

| AOI211_X1       | 0.950000 | 1.400000 |

| AOI211_X2       | 0.950000 | 1.400000 |

| AOI211_X4       | 1.710000 | 1.400000 |

| BUF_X1          | 0.570000 | 1.400000 |

| BUF_X16         | 1.140000 | 1.400000 |

| INV_X1          | 0.380000 | 1.400000 |

| INV_X16         | 0.950000 | 1.400000 |

| INV_X2          | 0.380000 | 1.400000 |

• The legalized and unlegalized cell positions are described by the format in the

respective files:

| AOI21_X2 | U26 | 3.662859 | 0.000000 |

|----------|-----|----------|----------|

| NAND2_X2 | U25 | 4.180000 | 2.800000 |

| NAND3_X2 | U24 | 0.950000 | 2.800000 |

| NOR2_X2  | U23 | 4.398846 | 4.200000 |

| INV_X16  | U22 | 0.028522 | 1.400000 |

| INV_X8   | U9  | 1.928515 | 1.400000 |

| INV_X32  | U8  | 2.660000 | 2.800000 |

| Input    | S1  | 5.538500 | 4.900000 |

| input    | S2  | 5.538500 | 3.500000 |

| input    | S3  | 5.538500 | 2.100000 |

| output   | S5  | 4.153875 | 5.600000 |

| output   | S7  | 4.153875 | 0.00000  |

etc...

#### **5.2 Benchmark Circuits**

The determination of the performance of an EDA tool is one of the major issues to be faced by a designer. One widely distributed way to control the final result is the selection of appropriate benchmark circuits, which will be given as input to the software. In this thesis are used the ISCAS '89 and ITC '99 benchmark circuits. In the remaining part of the chapter basic characteristics of these circuit designs will be presented, as well as, statistical data concerning the number and type of modules that the circuits are consisted of. These are the circuits that we are also going to use for demonstration and testing of the visualization tool.

#### 5.3 Possible future upgrades and expansion ideas

- In its current state, the tool can only parse a specific file format. A major upgrade would be the ability to work with Cadence standard .lef and .def files without any format transformation prior to using them in the tool. More file formats could also be an option.

- A more user-friendly and efficient way to load the required files instead of manually choosing them one by one. This could also be upgraded to control the validity of the files loaded in order to avoid invalid results.

- A zoom in/zoom out option that could provide a better view of large chips areas.

- 3D rendering and animation abilities

34

- An extra module able to provide graphical representation of the connections (nets) between cells is also possible.

- > Ability to assess qualitative and quantitative characteristics of circuits.

- Embed the algorithms developed by the VEDAlab and ability to work as a whole with them making this a complete EDA tool.

#### 5.4 Technology, problems and solutions applied

This tool is built using Java. Libraries such as JGraphX were used to create vectors that would later allow interaction with the cells. JGraphX is a Java graph visualization library that can easily create graphs among other things.

Java tools such as Swing were also employed for the drawing of the graphics. The code is written in a way that makes it easy to understand and extend its functionality.

Problems that appeared during the development of the tool were mainly of algorithmic nature.

✓ The check whether two cells overlap each other for instance is implemented in the following way:

```

private String checkOverlap(Cell t, int i) {

String color = "fillColor=green";

Cell t1;

for (int j = 0; j < cellList.size(); j++) {

t1 = cellList.get(j);

if (i == j || t1.getTypeName().equals("input") ||

t1.getTypeName().equals("output")) {

}

}

```

```

continue;

}

if(t.rect.intersects(t1.rect)){

color = "fillColor=red";

overlapCounter++;

break;

}

}

return color;

}

```

Borders indicating the chip area are drawn using vertices from the JGraphX library.

✓ The parsing of the files is another important area of the tool development process. In this specific implementation I adapt the parser to the format of the input files by not taking into account the strings that are not needed. For example the chip dimensions are loaded as per the following code:

```

String hstr, wstr;

try {

Scanner sc = new Scanner(file);

sc.next();

sc.next();

sc.next();

hstr = sc.next();

sc.next();

sc.next();

sc.next();

wstr = sc.next();

chipX = Float.parseFloat(wstr);

chipY = Float.parseFloat(hstr);

jLabelHeight.setText(hstr);

jLabelWidth.setText(wstr);

}

```

### **5.5 User guide to the tool**

The tool is run via the executable .jar file. Java insures compatibility on multiple platforms provided that it (a Java package) is installed in the target machine.

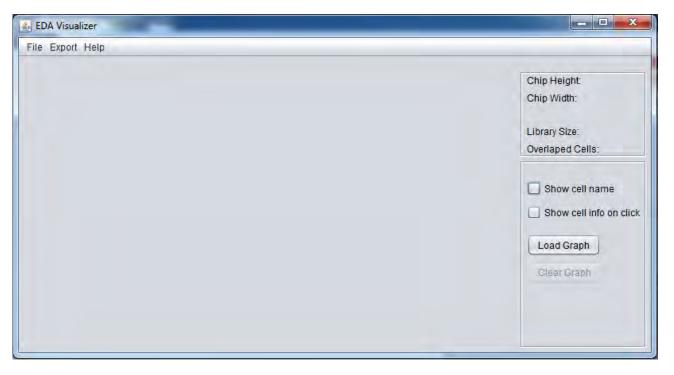

The window that the user is first greeted with is the following in the picture 5.1:

Picture 5.1

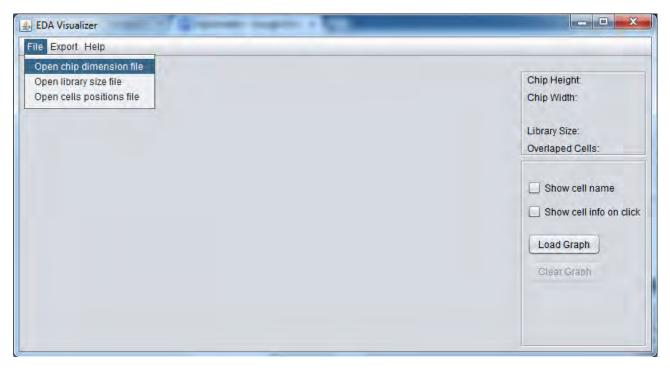

In here we can see a grey area that will draw the cells once it has all the required data and the "Load Graph" button is pressed. In order to start using the tool one must load the appropriate files in the following order. First one needs to open the "File" menu and select a chip dimensions file.

The next dialog gives the user the option to select the appropriate dimensions file:

| Look in:                                                            | dimensions                                                                                                                                                                                                                                                                              |  |

|---------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| S27.txt<br>S208.txt<br>S298.txt<br>S344.txt<br>S349.txt<br>S382.txt | S386.txt       S641.txt       S1196.txt         S400.txt       S713.txt       S1238.txt         S420.txt       S820.txt       S1423.txt         S444.txt       S832.txt       S1488.txt         S510.txt       S838.txt       S1494.txt         S526.txt       S953.txt       S1494.txt |  |

| File Name:                                                          | S208.txt                                                                                                                                                                                                                                                                                |  |

| Files of Type:                                                      | All Files                                                                                                                                                                                                                                                                               |  |

Now the user can see information about the chip dimensions.

Secondly the library size is required.

| 🛃 EDA Visualizer                                                                |                                                                                                              |

|---------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|

| File Export Help                                                                |                                                                                                              |