# Πανεπιστημίο Θεσσαλίας

$\Delta$ iii $\Lambda$ Ωmatikh Epgasia

# Εισαγωγή σφαλμάτων για ανάλυση αξιόπιστης λειτουργίας σε επεξεργαστές πολλαπλών πυρήνων

Συγγραφέας: Γεώργιος ΤΖΙΑΝΤΖΙΟΥΛΗΣ Επιβλέποντες: Αναπληρωτής καθηγητής Νικόλαος ΜΠΕΛΛΑΣ

Επίχουρος χαθηγητής Χρήστος ΑΝΤΩΝΟΠΟΙΛΟΣ

6 Ιουλίου 2011

#### Περίληψη

Καθώς οι τεχνολογίες των Ηλεκτρονικών Υπολογιστών εξελίσσονται, καινούργια προβλήματα εμφανίζονται μαζί τους. Ένα απο τα αναδυόμενα προβλήματα είναι η μείωση της αξιοπιστίας των ηλεκτρονικών κυκλωμάτων. Η αύξηση της ευαισθησίας των τρανζίστορ στη κοσμική ακτινοβολία, η διακυμάνσεις των ηλεκτρικών τους χαρακτηριστικών λόγο αστοχιών στη διαδικασία παραγωγής καθώς και η μείωση της αποδοτικότητας της παραγωγής ηλεκτρονικών κυκλωμάτων αποτελούν καίρια ζητήματα προς επίλυση ώστε να διατηρήσουμε την αξιοπιστία των μελλοντικών συστημάτων στα επιθυμητά επίπεδα. Σε αυτή τη κατεύθυνση δημιουργήσαμε ένα περιβάλλον εισαγωγής σφαλμάτων για την αξιολόγηση αξιόπιστης λειτουργίας υπολογιστικών συστημάτων. Παράλληλα, πειραματιστήκαμε με δύο εφαρμογές και παραθέτουμε μια εισαγωγή στο πώς επηρεάστηκε η συμπεριφορά τους απο σφάλματα υλικού.

# Περιεχόμενα

| 1        | Εισαγωγή                                                                                                                                                                                                                  | 3                                             |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| <b>2</b> | Introduction                                                                                                                                                                                                              | <b>5</b>                                      |

| 3        | Fault Tolerant Systems         3.1 Dependability Attributes         3.2 Dependability Threats         3.3 Faults Impact on a System - An Architectural Perspective         3.4 Quantitative Analysis of μarch Reliability | 7<br>9<br>9<br>10                             |

| 4        | <ul> <li>4.1 A Fault Injection Taxonomy</li></ul>                                                                                                                                                                         | <b>12</b><br>12<br>13<br>15<br>16<br>17<br>18 |

| 5        | 5.1Introduction5.2Simulation Attributes                                                                                                                                                                                   | <b>19</b><br>19<br>19<br>21                   |

| 6        | <ul> <li>6.1 Register File Fault Model</li></ul>                                                                                                                                                                          | 23<br>24<br>25<br>26<br>26<br>27              |

| 7        | 7.1       Introduction: Where, When, What                                                                                                                                                                                 | 28<br>28<br>29<br>30<br>30<br>31              |

|                                                                         |                                                          | 7.2.1   | Where                                        | 33              |  |  |  |

|-------------------------------------------------------------------------|----------------------------------------------------------|---------|----------------------------------------------|-----------------|--|--|--|

|                                                                         |                                                          | 7.2.2   |                                              | 33              |  |  |  |

|                                                                         |                                                          | 7.2.3   | What                                         | 34              |  |  |  |

|                                                                         | 7.3                                                      | Usage/  | Export to M5 configuration file              | 35              |  |  |  |

|                                                                         |                                                          | 7.3.1   | Register Injected Fault Configuration        | 36              |  |  |  |

|                                                                         |                                                          | 7.3.2   | PC Injected Fault Configuration              | 37              |  |  |  |

|                                                                         |                                                          | 7.3.3   | Memory Injected Fault Configuration          | 37              |  |  |  |

|                                                                         |                                                          | 7.3.4   | Fetch Stage Injected Fault Configuration     | 37              |  |  |  |

|                                                                         |                                                          | 7.3.5   | Decode Stage Injected Fault Configuration    | 38              |  |  |  |

|                                                                         |                                                          | 7.3.6   | Execution Stage Injected Fault Configuration | 38              |  |  |  |

|                                                                         |                                                          | 7.3.7   | Monitoring                                   | 38              |  |  |  |

| 0                                                                       | <b>T</b>                                                 |         |                                              |                 |  |  |  |

| 8                                                                       |                                                          |         | 1 8 / 1                                      | <b>39</b>       |  |  |  |

|                                                                         | 8.1                                                      |         | 0.7                                          | $\frac{39}{40}$ |  |  |  |

|                                                                         | 8.2 Statistical Fault Injection in Matrix Multiplication |         |                                              |                 |  |  |  |

|                                                                         | 8.3                                                      |         | 9                                            | 43              |  |  |  |

|                                                                         | 8.4                                                      | Target  | ed Fault Injection In The AVS Decoder        | 44              |  |  |  |

| A                                                                       | Α                                                        |         |                                              | 46              |  |  |  |

| A                                                                       | А<br>А.1                                                 | Statist |                                              | <b>±</b> 0      |  |  |  |

| A.1 Statistical Fault Injection in Matrix Multiplication — Addi<br>Data |                                                          |         |                                              |                 |  |  |  |

|                                                                         | ical Fault Injection in Matrix Multiplication — Overview | 46      |                                              |                 |  |  |  |

|                                                                         | A.2                                                      |         | · ·                                          | 46              |  |  |  |

|                                                                         | A.3                                                      |         |                                              | 40<br>47        |  |  |  |

|                                                                         |                                                          |         |                                              | 47<br>47        |  |  |  |

|                                                                         | A.4                                                      | -       | 5                                            |                 |  |  |  |

|                                                                         | A.5                                                      | Examp   | ble Frames with SDC                          | 49              |  |  |  |

| 9                                                                       | Con                                                      | clusior | 15                                           | 53              |  |  |  |

| -                                                                       | 9.1                                                      | Conclu  |                                              | 53              |  |  |  |

|                                                                         | 9.2                                                      |         | Work                                         | $53 \\ 54$      |  |  |  |

|                                                                         | 0.4                                                      | rasure  | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,       | <u> </u>        |  |  |  |

# Κεφάλαιο 1 Εισαγωγή

Τις τελευταίες δεκαετίες γίναμε μάρτυρες της ραγδαίας ανάπτυξης των επιδόσεων και δυνατοτήτων των ηλεκτρονικών υπολογιστών αλλά και γενικότερα όλων των ψηφιακών συστημάτων. Οι συνεχείς εξελίξεις στην τεχνολογία της λιθογραφίας εξακολουθούν, τα τελευταία τριάντα χρόνια, να μειώνουν το μέγεθος των τρανζίστορ κατα το μισό κάθε 18 μήνες δημιουργώντας ένα πλεόνασμα σε κάθε νέα γενιά. Το πλεόνασμα αυτό χρησιμοποιείται για την υλοποίηση πιο περίπλοκων και αποδοτικών αρχιτεκτονικών, που ταυτόχρονα λειτουργούν σε υψηλότερες συχνότητες και μειωμένη τροφοδοσία.

Αυτή όμως η πρόοδος δεν γίνεται χωρίς την εμφάνιση προβλημάτων. Καθώς το μέγεθος των τρανζίστορ μίκρυνε δευτερεύοντα φαινόμενα που δεν επηρέαζαν τις προηγούμενες τεχνολογίες μετατράπηκαν στα κυρίως εμπόδια για περαιτέρω βελτίωση των ψηφιαχών συστημάτων. Η δυσανάλογη επιτάχυνση των τρανζίστορ σε σχέση με τις δυναμικές μνήμες τυχαίας προσπέλασης δημιούργησε το επονομαζόμενο "memory wall", ενώ η συνεχής συσσώρευση τους ανέβασε την ενεργειαχή πυχνότητα σε δυσβάσταχτα επίπεδα.

Πέρα των παραπάνω προβλημάτων, ένα ακόμη —ιδιαίτερα σημαντικό— πρόβλημα είναι η μείωση της αξιοπιστίας των τρανζίστορ. Η μείωση των διαστάσεων τους έκανε τα ηλεκτρικά στοιχεία πιο ευάλωτα σε λάθη λόγω κοσμικής ακτινοβολίας.  $\Pi$ αράλληλα, οι διαφορές λόγω αναχρίβειας στη διαδιχασίας εχτύπωσης τους έχει επιπτώσεις στα ηλεκτρικά χαρακτηριστικά τους με αποτέλεσμα να συμπεριφέρονται πλέον περισσότερο ως τυχαίες μεταβλητές, αχρηστεύοντας την τεχνική της ανάλυσης χρονισμού χειρότερης περίπτωσης. Αχόμη, η αποδοτιχότητα της διαδιχασίας παραγωγής, δηλαδή πόσα απο τα παραγόμενα συστήματα τελικά θα βγουν στην αγορά, γίνεται πιο περίπλοκη. Συγκεκριμένα, καθώς περισσότερα στοιχεία συνθέτουν το τελικό μας σύστημα, μεγαλώνει και η πιθανότητα να εμφανιστεί αστοχία ή ανακρίβεια σε κάποιο απο αυτά. Η τάση αυτή μπορεί να οδηγήσει στο μέλλον, για λόγους κόστους, να δίνονται στη κατανάλωση συστήματα που μόνο ένα μέρος αυτών θα έχουν αξιόπιστη λειτουργία. Διαβλέποντας ότι τα προβλήματα αυτά θα γίνουν πιο έντονα με τις επόμενες γενιές υπολογιστών και η προοπτική της αύξησης των σφαλμάτων σε τέτοιο βαθμό ώστε αχόμη χαι συστήματα στα οποία δεχόμαστε να παρουσιάζονται λάθη (π.χ. προσωπικός υπολογιστής) να γίνουν υπερβολικά αναξιόπιστα, η ερευνητική κοινότητα στράφηκε τα τελευταία χρόνια στην αναζήτηση βιώσιμων λύσεων.

Προϋπόθεση για τη δημιουργία και παραγωγή λύσεων είναι η ανάλυση της επίδρασης των σφαλμάτων υλικού στις εφαρμογές που θα εκτελεστούν σε αυτό. Με τη σειρά του αυτό, προϋποθέτει την ύπαρξη κατάλληλων μετρικών για να ποσοτικοποιήσουμε την αξιοπιστία ενός συστήματος, εργαλεία τα οποία θα μας επιτρέψουν τον πειραματισμό με μη-αξιόπιστα περιβάλλοντα εκτέλεσης, αλλά και πρωτότυπα μηχανισμών επανάκαμψης από/αποφυγής σφαλμάτων. Σε αυτό το σημείο είναι και η συνεισφορά αυτής της διπλωματικής εργασίας.

Το προϊόν αυτής της εργασίας είναι η επέκταση ενός σύγχρονου, ευρέως διαδεδομένου προσομοιωτή πλήρων-συστημάτων (αχριβείας-κύκλου) με ένα σύνολο δομών και συναρτήσεων που επιτρέπουν την εισαγωγή σφαλμάτων στις δομές του. Ο επιλεγμένος προσομοιωτής (M5) παρέχει τη δυνατότητα προσομοίωσης μονοπύρηνων/πολυπύρηνων συστημάτων, καθώς και συστήματος-συστημάτων. Η νέες δυνατότητες εισαγωγής σφαλμάτων στις δομές του δεν υπόκεινται σε κανέναν περιορισμό στον αριθμό, το χώρο ή το χρόνο. Υποστηρίζονται η εισαγωγή σφαλμάτων σε 2 μοντέλα (λειτουργικό και αναλυτικό) της Μονάδας Επεξεργασίας Δεδομένων — συγκεκριμένα στο φάχελο καταχωρητών, το μετρητή προγράμματος και τα στάδια προσκόμισης, αποκωδικοποίησης και εκτέλεσης της εντολής — και στα περιεχόμενα της φυσικής μνήμης.

Όσον αφορά το τρόπο που θα αλλοιωθεί η τιμή του επιλεγμένου στοιχείου, το εργαλείο μας προσφέρει την επιλογή μεταξύ άμεσης ανάθεσης κάποιας τιμής, εναλλαγής ενός bit στη συμπληρωματική του τιμή, λογική διάζευξη της τιμής του στοιχείου με κάποια σταθερά καθώς και την ανάθεση σε όλα τα bit της δομής την τιμή 1 ή 0. Τα σφάλματα αυτά μπορεί να οριστούν ως παροδικά, μόνιμα ή στιγμιαία.

Μετά το πέρας της υλοποίησης της επέκτασης του προσομοιωτή συνεχίσαμε με πειραματισμό χρησιμοποιώντας το καινούργιο εργαλείο. Πειραματιστήκαμε με 2 εφαρμογές: μια εφαρμογή πολλαπλασιασμού πινάκων 64x64 και τον αποκωδικοποιητή βίντεο AVS.

Τα συμπεράσματα αυτών των πειραμάτων ήταν, αφενός ότι δεν φανερώνονται όλα τα λάθη στο επίπεδο της διεπαφής του χρήστη· δηλαδή αρκετά σφάλματα επικαλύπτονται/χάνονται και αυτό διότι υπάρχει επαναχρησιμοποίηση των καταχωρητών και 'επιθετική' προσκόμιση και εκτέλεση εντολών με αποτέλεσμα να μη χρησιμοποιούνται όλα τα αποτελέσματα που παράγονται/επηρεάζονται απο σφάλματα. Αφετέρου, ότι υπάρχουν τμήματα σε προγράμματα τα οποία μπορούν να υποστούν σφάλματα χωρίς να διακόπτεται η εκτέλεση ή η αλλοίωση των δεδομένων να μην τα καθιστά άχρηστα (π.χ. σφάλματα στο κάτω-δεξί κελί του πινάκα iDCT στον AVSA.2). Η τελευταία παρατήρηση έχει ιδιαίτερη σημασία καθώς μπορεί να μας βοηθήσει στην επίλυση του ενεργειακού προβλήματος, "power wall". Συγκεκριμένα, σε συνδυασμό με μια αρχιτεκτονική που θα προσφέρει ανοχή σε σφάλματα χρονισμού θα μας έδινε τη δυνατότητα να εκτελούμε τέτοιους κώδικες σε Μονάδες Επεξεργασίας Δεδομένων που λειτουργούν σε τιμές τροφοδοσίας κάτω των προδιαγραφών, το οποίο δημιουργεί σφάλματα χρονισμού στο κύκλωμα αλλά παράλληλα εξοικονομεί ενέργεια (βλέπε συνάρτηση 1.1).

$Power = Capacitance * Frequency * Voltage^2$ (1.1)

# Chapter 2

# Introduction

During the last four decades we witnessed an enormous growth in the performance and functionality of processors. Advances in fabrication technology conveyed us from  $10\mu$ m features width in 1971 to today's 32nm, a trend that led to the doubling of processors' transistor count every two years — colloquially called Moore's law. This surplus of transistors enabled computer architects to design more sophisticated circuits which, at the same time, functioned at a higher frequency and lower voltage.

On the other hand, secondary phenomena that had little or no effect on previous technologies were exacerbated as transistor features shrank creating new obstacles that halt performance [9]. The disproportional speed-up of transistors, compared to that of DRAMs, created the so called "memory wall" and their continuous accumulation increased circuit power density to an unbearable degree, a phenomenon called "power wall".

Apart from the above problems, as transistors approached the nanometer threshold they became more vulnerable to radiation-induced faults (cosmic particles that enter the atmosphere). Furthermore, as their features size decreases, the problems from process variations increase. The electric characteristics of transistors now behave more like random variables making a deterministic worst case timing analysis ineffective. As the impact of physical variables becomes more intense, researchers are working on building reliable systems with unreliable components to guarantee the correct function of modern electronic devices under such constraints. Another important aspect, though not strictly technical, is the decrease of the process yield. Accumulation of more components for a single system means that there is a greater chance part of it to contain corruptions, which will affect its output's reliability. Currently, this problem is solved by disabling such modules, however, this is inefficient in both economic and performance terms. Except from the direct benefits from technological advancements in this area other areas may be benefit too; for example, fault-tolerant architectures would enable the use of processors in sub-threshold voltage levels to improve power efficiency.

Reliable execution on unreliable components is the next "wall" electronic system designers should overcome to further improve computers performance. To effectively attack this problem we need to perform a thorough analysis of the way hardware faults manifest to errors in the different abstraction layers of computer systems. The analysis and categorization of the behavior of faults will enable the creation of a hierarchy of targets/modules that need to be enhanced to achieve robustness.

In order to expand our understanding on the aforementioned problems new tools need to be created or the existing ones should be augmented to support the new constrains and physical variables. The main contribution of this Thesis is in this direction. In order to study the behavior of applications in the presence of transient faults, we developed a fault injection framework on top of M5 (a full system, cycle-accurate simulator) as we could not find an existing tool to cover our needs.

We choose to work with a software simulator for the perspective and attributes it provides. By using a simulator we are able to study architectures and configurations not yet implemented and at the same time exercise complete control over the nature of a fault; that is, the location and timing of the manifestation of the fault, as well as its effect on the affected module's value. Also, the provided controllability in experimentation enables the partial examination of a program's execution for a more thorough analysis of its behavior on an unreliable environment.

The other contribution of this Thesis is the experimental evaluation of two applications on an unreliable environment: an 64x64 matrix multiplication kernel and the AVS decoder.

This document is structured in two basic blocks: the first one introduces the theoretical background and the second describes the framework and outlines the experimental evaluation.

In the first part, a brief introduction in fault-tolerance and fault injection is given in Chapters 3 and 4. In Chapter 5 we discuss the benefits of full system simulation.

In the second part, starting at Chapter 6, we give an overview of the fault model in which this work was based upon. Chapters 7 and 8 discuss the implementation details of the framework and an analysis of the results obtained using it, in respect.

Finally, Chapter 9 presents the conclusion of this work and directions for future work.

# Chapter 3

# **Fault Tolerant Systems**

In the previous section we discussed the need for fault-tolerant design of future systems. A system is fault-tolerant if it is capable of performing its specified tasks in the presence of faults, either at the hardware or at the software level.

For example, software bugs need to be overcomed for continuing correct execution and hardware module failures should not inhibit the system's ability for correct execution. By correct we are not referring only to error free results, but also on results that maintain a small, user/application defined, margin of error.

Fault tolerance is an important feature of a system as it ensures its dependability; it is, as stated in [6], the ability to deliver service that can justifiably be trusted.

### 3.1 Dependability Attributes

Dependability can be considered as the integrating concept of the following attributes [6]:

**Reliability** : continuity of correct service.

Availability : readiness for correct service.

Safety : absence of catastrophic consequences on the user's environment.

**Maintainability** : ability to undergo modifications and repairs.

Following, we will see in more details the two main attributes of dependability [41], reliability and availability.

We can define **reliability** (R) as the probability that a component will not experience an error, visible to the defined abstraction's outer scope, in the time interval (0, t],

$$R(t) = P(T > t), \tag{3.1}$$

where T is a random variable expressing the component's lifetime.

The reliability of a system (i.e. an accumulation of similar components) of N modules in a period of time (0, t] is given by the fraction of the unfaulted components until time t to the total amount of components.

$$R_N(t) = \frac{N_{\text{unfaulted}}(t)}{N_{\text{total}}} = \frac{N_{\text{total}} - N_{\text{faulted}}(t)}{N_{\text{total}}} = 1 - \frac{N_{\text{faulted}}(t)}{N_{\text{total}}}, \quad (3.2)$$

where  $N_{\text{total}}$  is the total number of components,  $N_{\text{unfaulted}}(t)$  is the total number of components that *have not* experienced an error in the time interval (0,t] and  $N_{\text{faulted}}(t)$  is the total number of components that *have* experienced an error in the time interval (0,t].

As **hazard rate**  $H_N(t)$  we define the probability that a system of N components, that have not presented a fault till time t, will present an error in the time interval  $\Delta t$ .

$$H_N(t) = \frac{\frac{d}{dt} \left( N_{\text{faulted}}(t) \right)}{N_{\text{unfaulted}}} = \frac{\frac{\frac{d}{dt} \left( N_{\text{faulted}}(t) \right)}{N_{\text{total}}}}{\frac{N_{\text{unfaulted}}}{N_{\text{total}}}}$$

(3.3)

By combining equation 3.3 and the derivative of equation 3.2,

$$\frac{d}{dt}\left(R_N(t)\right) = -\frac{\frac{d}{dt}\left(N_{\text{faulted}}(t)\right)}{N_{\text{total}}},\tag{3.4}$$

we get,

$$H_N(t) = \frac{-\frac{d}{dt} \left( R_N(t) \right)}{R_N(t)},$$

(3.5)

which we can transform to equation 3.6,

$$R_N(t) = e^{-\int H_N(t) \, dt},\tag{3.6}$$

so as to represent reliability in terms of the hazard rate.

The exponential relationship between a system's reliability and time, as shown in equation 3.6, is known as the *exponential failure law* and enables us to compute the overall reliability of a system with N components by the following equation.

$$R_N(t) = \prod_{i=1}^N R_i(t) = e^{-\left(\sum_{i=1}^N (\int H_i(t) \, dt)\right)t}$$

(3.7)

Finaly, **availability** can be defined as the probability that the system will function correctly at a given time.

$$Availability = \frac{System \text{ up-time}}{System \text{ overall time}}$$

(3.8)

### 3.2 Dependability Threats

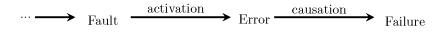

When the dependability of a system is compromised, we say a failure has occurred; that is, the desired service of the system deviates from correct function. A failure occurs when an error is presented in a system component. An error is a divergence of a component to an incorrect state. The cause of an error is called a fault and with that we have formed the chain of dependability threats.

The connection between the dependability threats is depicted in figure 3.1.

Figure 3.1: Chain of dependability threats [6].

Faults can be categorized according to their nature in three basic categories [41]:

- **Permanent:** Permanent faults are present indefinitely in the system until corrective measures are taken.

- **Intermittent:** Intermittent faults appear, disappear and then reappear in the system's life time and can be early indications of permanent faults.

- **Transient:** Transient faults appear and disappear without repetition.

A brief correspondence of different hardware faults to fault types can be seen in table 3.1.

|                 |                                        | Fault Types  |              |

|-----------------|----------------------------------------|--------------|--------------|

|                 |                                        | Permanent    | Transient    |

|                 | Electro-migration                      | $\checkmark$ |              |

|                 | Metal Stress Voiding                   | $\checkmark$ |              |

|                 | Gate Oxide Wear-out                    |              |              |

|                 | Hot Carrier Injection                  |              |              |

| Hardware faults | Negative Bias Temperature Instability  |              |              |

|                 | Radiation                              |              | $\checkmark$ |

|                 | Transistor Variability                 |              | $\checkmark$ |

|                 | Thermal Cycling                        |              | $\checkmark$ |

|                 | Erratic Fluctuation in minimum voltage |              |              |

Table 3.1: Hardware faults and their type

# 3.3 Faults Impact on a System - An Architectural Perspective

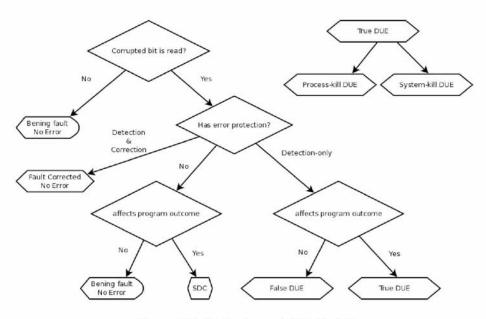

Whether a fault manifests to a failure depends on whether the error will be masked/corrected or not. Figure 3.2 shows all the possible outcomes of an error occurrence by an architectural perspective.

Figure 3.2: Faults impact [42, 43, 41]

To find the possible outcomes and the impact of a fault on a system's behavior we must first consider if the faulty part (bit) is used by the system for a particular service. If it is not used, then the fault is called benign and produces no error, otherwise we have to further consider if it is covered by any error-correction mechanism.

If the faulty part is covered by a detection and correction mechanism then the fault is corrected and produces no error. In case of no protection mechanism or a detection-only mechanism then we need to evaluate if the error influences the output of the particular service.

If no error protection covers the erroneous part but it does not influence the system's output then the fault is benign and no error occurs, but in the case that the output is influenced then we have a Silent Data Corruption (SDC).

On the other hand, if the fault is covered by detection-only mechanism then again we observe the influence that it has on the system's output. If the output is not altered we have a False Detected Unrecoverable Error (False DUE), else, if it affects the system's output we have a True Detected Unrecoverable Error (True DUE).

True Detected Unrecoverable Error can be further divided into System-kill and Process-kill faults based on whether the error can be isolated in a single process or it requires a system wide restart.

### 3.4 Quantitative Analysis of µarch Reliability

As the reliability assessment of a system is crucial and influences decisions in the design phase of a project, research has been made in producing quantitative measures of it.

The most well known measures of system's reliability are Mean Time to Failure (MTTF), Failure in Time (FIT) and Mean Time between Failures (MTBF) [41].

MTTF expresses the mean time between two faults (i.e. if a module presents a fault every 2 years its MTTF is 2 years).

$$MTTF_N = \frac{1}{\sum_{i=0}^N \frac{1}{MTTF_i}} \tag{3.9}$$

Due to the complexity of computing the MTTF for a number of components many choose to use FIT which is additive. One (1) FIT represents a fault in a billion  $(10^9)$  hours, so if we have two components and the first one has a FIT of 10 and the other a FIT of 20 then their overall FIT is 30.

$$FIT_N = \sum_{i=0}^{N} FIT_i \tag{3.10}$$

the relation between MTTF and FIT is:

$$MTTF_{in years} = \frac{10^9}{FIT \times 24 \ hours \times 365 \ days} \tag{3.11}$$

MTBF expresses the mean time between the occurrence of two faults. To compute MTBF we need to know the Mean Time to Repair (MTTR).

$$MTBF = MTTF + MTTR \tag{3.12}$$

In the recent literature additional metrics have been proposed for use in evaluating a structure's reliability. In [43] and [42] the Architectural Vulnerability Factor (AVF) was introduced. AVF is defined as "the fraction of time an upset in a cell can cause a visible error in the final output of the program". AVF integrates both the application and  $\mu$ architecture vulnerability factors and does not provide any detail on the degree that a particular  $\mu$ architecture or application affects the vulnerability factor. An effort to separate these two factors into distinct metrics was made in [53] and [52] by introducing the Program Vulnerability Factor (PVF) and Hardware Vulnerability Factor (HVF).

# Chapter 4

# **Fault Injection**

After introducing the general concept of dependability/fault-tolerance of a system in this chapter we will present fault injection (FI) a technique to evaluate it.

Fault injection can be defined as the process of introducing and instrumenting faults/disruptions in a system for study of its behavior in the presence of faults. FI is an essential complement to other techniques used for validation of systems' dependability.

To enhance our confidence in the validation process of a system, it is necessary to use a variety of different methods to thoroughly examine and ensure a good level of dependability. Fault injection allows to confirm the structure and calibrate the parameters of existing fault-tolerance models or to develop new fault-tolerance models and validate them: for example x% of errors of type y are detected [28].

Based on the phase of a project, fault injection is employed using different techniques and layers of abstraction. During the design phase, simulation is mainly used for assessing the dependability of the system, whereas at the prototype phase physical fault injection is preferred.

### 4.1 A Fault Injection Taxonomy

This section serves as a brief taxonomy of fault injection techniques. The basic techniques will be presented along with related work and the advantages and disadvantages of each approach [60]. The first part classifies techniques based on the method used for the injection and the second enumerates the layers of abstraction at which the fault can be injected.

#### 4.1.1 Physical Fault Injection

Physical fault injection methods are using the actual hardware of the System Under Test (SUT) and the injection is done by augmenting the system with special hardware that enables the introduction of faults. Such techniques can be further divided to those that have direct contact with the SUT and those that don't. Fault injection with contact is performed by producing voltage and current disturbances to the system's external pins. The pins can be manipulated by either using active probes or using sockets. According to the first method, pinlevel active probes are attached in the SUT pins in order to directly create stack-at faults or to short-circuit them to create bridging faults. According to the second method, injection is performed by inserting a socket between the targeted module and its circuit board. The socket enables the creation of stack-at, open or more complex logical faults like inverted, XORed, ANDed pins or previous value of them.

For fault injection *without contact* special equipment is needed and it mainly targets transient fault injection. To create hardware faults without contact one can employ radioactive isotopes, neutron beams, proton beams or other means for creating electromagnetic interferences in the SUT. Radioactive isotopes such us americium-241, uranium-238, californium-252 or thorium-232 that emit alpha particles can be used for measuring the impact of alpha particle induced errors, whereas for neutron induced soft errors one can use energetic proton or neutron beams[36]. A list of locations where one can find the equipment for such experiments can be found at the JEDEC standard No.89[5].

The main advantage of physical fault injection is that it uses the original hardware without changes and experiments are executed at real-time enabling the experimentation with large workloads and unaltered applications. Moreover, it can inject faults in places that are hard to reach by other means without changing the SUT's hardware, thus it is one of the less-intrusive FI methods.

On the other hand, these methods have low portability over systems, requiring new design and installation for each platform. The use of special purpose hardware that requires large funding and can be found in limited places makes difficult the broad adaptation of such techniques by the research community. In addition, physical fault injection lacks in terms of controllability and observability; especially in methods without contact it is extremely hard to create targeted and precise injection.

Physical fault injection was one of the first methods used to assess the dependability of a system. A lot of tools and techniques have been developed during the past decades. Some of them are:

- **RIFLE[39]** A pin-level fault injection system that employs the socket method and was developed at the University of Coimbra for dependability evaluation.

- **MESSALINE**[4] A pin-level fault injection system developed at LAAS-CNRS that uses both socket and probe methods.

- **FIST**[34] Fault injection system developed at the Chalmers University of Technology for study of transient faults using heavy-ion radiation.

- FTMP[26] A fault-tolerant processor created by NASA which has also been evaluated using fault injection techniques.

#### 4.1.2 Fault Emulation

In Fault Emulation techniques (a.k.a SWIFI, Software Implemented Fault Injection) faults are introduced through changes in the software, so as to emulate corruptions from hardware faults, while executing in the actual SUT. Fault emulation techniques can be divided into compile-time techniques and run-time techniques, based on the time the injection is performed.

Compile time fault injection modifies the source code or assembly instructions of the software under evaluation during the compilation process in order to emulate hardware and software (bugs) faults.

On the other hand, in run time fault injection the application's execution is halted through timers, traps/exceptions or code is injected to perform fault injection in the hardware structures that are accessible through software. When using timers (hardware or software) a timeout occurs at a specific time and control is given to system software that performs the fault injection. Similarly, traps or exceptions are used to specify the timing of fault injection based on events (e.g. specific instruction execution or memory address access). Finally, the last approach, code injection, inserts instructions in parts of the source code at run-time to emulate hardware faults.

Fault emulation fault injection has the advantage of been fast (execution at real time) and use the actual SUT. Also, it enables targeting parts of applications or operating systems, which is hard to do with other techniques. Another advantage of software based techniques is the high controllability that they provide and the repeatability of the experiments.

However, fault emulation is an intrusive method both in modifying the original source code and in indirectly affecting the applications' timing. The execution of the fault injection and control framework on the same system can disrupt the statistics and observations of the experiment. In addition, software-based methods can only access structures that are available through the ISA, thus restricting the injection capabilities.

Fault emulation was the prevaling choice for fault injection during the 90's. Some of the most widely accepted frameworks are:

- FERRARI[31] A framework for fault emulation using traps and systems calls developed at the University of Texas, Austin.

- **FINE**[32] A run-time fault injection and monitoring environment for the Unix OS developed at the University of Illinois, Urbana Champaign.

- FTAPE[55] A fault injection framework for assessing a system's fault tolerance developed at the University of Illinois, Urbana Champaign.

- JIFI[51] An application-level fault injection framework developed for use on a fault tolerant parallel processing cluster at the California Institute of Technology.

- **XCEPTION[13]** A software fault injection and monitoring environment that employs the debugging and performance monitoring capabilities of microprocessors for fault injection; developed at the University of Coimbra, Polo II.

- **DOCTOR**[49] An integrated software fault injection environment developed at the University of Michigan with emphasis in portability.

- **EXFI**[10] A SWIFI environment for fault coverage evaluation on embedded microprocessor-based boards that relies on the "Trace Exception Mode" of multiprocessors; developed at Politecnico di Torino.

- **NFTAPE**[54] A configurable environment for automating fault injection experiments. It was developed in a modular way to enable the usage of different tools for fault injection, triggering and monitoring. It was developed at the University of Illinois, Urbana Champaign.

- **GOOFI**[1] A fault injection tool with support for pre-execution fault injection and injection through scan-chain capabilities of the processor. It was developed at the Chalmers University of Technology with emphasis on portability.

- FAIL-FCI[25] A high-level fault injection framework for evaluation of distributed applications in the presence of faults (crashes) developed at IN-RIA, France.

#### 4.1.3 Software Simulation

Simulation-based fault injection requires the design and development of a simulation model of the SUT (i.e. processor, devices) that is simulated on another system. The simulation model of a system can be described either using a common programming language like C and C++ or a Hardware Description Language (VHDL, Verilog). Traditionally, the system under test is called target and the system in which the simulator is executed is called host.

Due to the extensive use of Hardware Description Languages, like VHDL, in the design process of modern ICs, several techniques have been proposed in simulation based fault injection with the use of HDL models. We can divide these techniques in two main categories: those that require modification of the original HDL source code and those that use built in capabilities of the simulator.

The first approach, that relies on code modification, augments the system's source code with dedicated fault injection modules called saboteurs or modify -mutate- the original code of a module to enable precise injection and tracing of faults.

The second approach uses modified simulators that support the injection and inspection of faults through built-in instructions/commands. The instructions target module signals and variables that can be directly accessed and manipulated through the simulator interface at run-time.

Another approach in simulation-based fault injection is the system modeling in a high-level programming language. The system's description in a functional layer enables full system simulation or system of systems simulation. Recent research in fault injection and reliability favors the usage of full system simulators that can be used, not only for assessment of the robustness of an architecture, but also for characterizing behavior of large workloads in the presence of faults.

Simulation-based fault injection frameworks can support any system abstraction level, electrical, logical, functional, architectural or hybrids, providing a plethora of choices. In addition, the use of software enables full control over fault modeling (transient, permanent, intermittent) and injection. Simulation provides maximum observability without being intrusive, as any element or module can be accessed at any time without influencing the behavior of the system. Simulation-based fault injection tools do not require the modification of application source code, enabling the validation of applications whose source code is not available. Another advantage of such tools is the low cost of reproduction of the system for multiple parallel simulations. The main disadvantage of simulation based fault injection techniques is that experiments are consuming (compared to other methods). The more detailed the model, the more time it will take to have it simulated. This is in fact the main reason the research community started favoring simulators with higher level of abstraction, mainly developed using C and C++. Also, the implementation of an accurate model is expensive in time and effort and crucial for the simulators are commercial products, their source code is not available for modification.

Nowadays, simulation-based fault injection has become the most widely accepted methodology. Some of the past and currently used frameworks are:

- SIMICS[40][8] A commercial full-system simulator that has been augmented with fault injection capabilities.

- **COTSon[3][23]** A commercial full-system simulator that has been augmented with fault injection capabilities

- SWAT-sim [38] A framework for hierarchical simulation for studying the systemlevel manifestation of gate-level faults.

- **VERIFY**[50] A simulation based fault injection framework that augmented the VHDL language with fault injection signals and their occurrence enabling the description of components behavior after faults and instrumentation of fault injection campaigns.

- **DEPEND**[22] A functional simulation framework focusing in providing a design and fault injection framework for system level dependability analysis.

- MEFISTO[29] An integrated environment for applying fault injection with support of different levels of abstraction.

- **HEARTLESS**[47] A hierarchical Register-Transfer-Level fault simulator.

- **GSTF**[7] A simulation based fault injection tool with capabilities of evaluating medium-complexity system models.

#### 4.1.4 Hardware Emulation

To cope with the time overhead of simulating the SUT, the usage of FPGAs has been proposed. The circuit under examination is implemented using the standard synthesis, placement and routing design flows and then it is downloaded to an FPGA. The fault injection process is instrumented through a computer that is connected with a high speed communication link to the FPGA board through its I/O pins. There are two approaches for enabling fault injection in FPGAs: the first is to alter the source code of the SUT and augment it with modules and structures for fault injection, whereas the alternative is to use the run-time reconfiguration. Run-time reconfiguration (RTR) exploits the ability of FPGAs to be reprogrammed on-the-fly. That way, the hardware can be alter directly in its low level structures to inject faults in it.

The benefits of hardware emulation based fault injection is the speed-up of experimentation compared to simulation-based methods and also the comparable controllability of these methods. Furthermore, FPGAs can be used for dependability assessment of reusable circuit components (IP blocks). On the other hand, hardware emulation methods experience the same problems, thought not in such extend, with pin-level fault injection techniques. The injection capabilities are constrained by the number of free I/O pins of the programmable hardware. Moreover, the link used for the communication between the FPGA and the fault injection controller can influence the experimentation speed.

This approach for fault injection is new and has yet to receive wide acceptance from the research communication. Example publicatios on related research are:

- **FOCUS**[14] A design automation environment developed at the University of Illinois at Urbana-Champaign that fashioned a scan-chain technique for fault injection in an FPGA board.

- Using RTR for FI Applications [2] A proposal for exploiting the run-time reconfiguration capabilities of modern FPGA's for speeding-up the fault injection process.

## 4.2 Abstraction Based Categorization

Apart from the previous, method-oriented, categorization of fault injection techniques/frameworks, we can approach fault injection techniques based on the level of abstraction at which the faults are injected.

Experimentation in system's dependability, fault-detection and fault recovery mechanisms may be verified by injecting faults at any level of abstraction and allowing the errors to propagate to higher levels. Researchers prefer to work in the lowest level of abstraction to assure accuracy of the experiments, however, problems may arise from such a choice as it was previously described. Consequently, there has been extensive research in how physical faults manifest in higher levels (rtl, functional), to enable the usage of high-level simulators [59, 18, 12].

The following taxonomy is provided as given in [59] and presents a list of increasing levels of abstraction from the device level to the network level. It can be generalized into two broad categories: circuit-level abstractions at the lower end and functional-level abstractions at the higher end.

Circuit: In this category, the physical makeup of the processor is considered.

- **Device:** Its main focus is the transistor and other circuit elements. For simulated fault injection an analog simulator is need, whereas for physical injection radiation or other physical stress may be used.

- Gate: Its main focus are logic gates (AND, OR, NAND, XOR, multiplexers, etc). The stack-at or fixed-at model is employed although some implementations use more accurate models, modeling signals and storage cells coupling.

- **Basic Block:** Its main focus are functional units of the system like adders and registers and the fault models are high-level abstraction of physical fault models.

- Chip: Its main focus is the chip's boundary I/O.

- **Functional:** In this category, the circuit description itself is no longer considered, but instead a functional description of it is used.

- Micro-operation: Its main focus in micro-instructions and faults are injected at data transfers and micro-sequencing.

- **Macro-operation:** Its main focus are ISA instructions and faults are injected by flipping bits in the instruction word.

- **System:** Its main focus is Memory and processor I/O in which faults are injected.

- **Network:** Its main focus are messages and other ways of communication where faults can be injected (e.g. message corruption, dropped package).

# 4.3 Our Choice

After studying past implementations and publication in the area of fault injection, we decided that simulation based fault injection and specifically full system simulation is what best serves our needs and objectives. Using a full system simulator we will be able to evaluate the impact of faults in large workloads, full OSs and in general real world applications which is our main target.

In brief, simulation provides maximum controllability over the injection procedure in both spatial and temporal manner, also, it enables the studying of independent or concurrent execution of applications. Another key feature that pushed toward this decision was the observability over the full trace of the behavior of the system, before and after an injection, that a simulator provides; needed for understanding the way different faults affect instructions and workload patterns.

As mention in section 4.1.3 software simulation is a non-intrusive method to the application that is executed and can provide statistics and logs of arbitrary detail. In addition, as our choosen simulation framework is open source we can alter the modules structure to match desired accuracy for each experiment.

Finally, we try to mitigate the time overhead of the simulation by running multiple simulation in parallel, something that can only be done with simulationbased fault injection techniques as the installations can be easily and with no cost reproduced.

In the next section we provide an overview of full system simulation and an introduction to the M5, the simulator we augmented with fault injection capabilities and used in for experiments.

# Chapter 5

# **Full System Simulation**

### 5.1 Introduction

Full system simulation of a computer system is the process of modeling its physical components in such a high detail that any software for the targeted system can run unmodified on the virtual hardware. Simulated components can be anything from CPUs, cache memories, network connections or any other peripherals/modules that compose or interact with the SUT.

Due to these characteristics full-system simulators are able to run operating systems without the need of modifying them or their device drivers, thous expanding the capabilities in hardware and system software design.

We should note here that the models' fidelity can be of arbitrary level, however, the more detailed the model the smaller the system we can test (model detail  $\uparrow \rightarrow$  simulation time  $\uparrow$ ).

# 5.2 Simulation Attributes

Full system simulation is becoming more and more appealing for use in research. The advancements in simulation and testing theory have boosted the efficiency of simulators and the computational power explosion enabled us to simulate large systems on cheap personal computers.

Because of those two factors an increasing number of researchers (Table 5.1) choose to use simulators on their experiments.

However, these are not the only reasons behind the increase in the number of publications that use simulators. Since simulation is done using software it offers many advantages compared to the real machine environment (see section 4.1.3).

Jakob Engblom lists the attributes that make simulation appealing in [19]. We set forth this list here for completeness.

- **Configurability.** Technological barriers or lack of physical/hardware resources do not place constrains on system configuration options.

- **Extendability.** The simulator can be easily augmented with additional components without any limitations (i.e. GPU/DRAM slots).

| Year | Total papers | Simulation |

|------|--------------|------------|

| 2009 | 43           | 39         |

| 2004 | 31           | 27         |

| 2001 | 25           | 22         |

| 1997 | 30           | 24         |

| 1993 | 32           | 23         |

| 1985 | 43           | 12         |

| 1973 | 28           | 2          |

Table 5.1: Performance evaluation methodologies in papers appearing in the Proceedings of the International Symposium on Computer Architecture. Adapted from [56]

- **Controllability.** The execution of the simulation can be arbitrarily controlled, stopped, and restarted.

- **Determinism.** A simulation is completely deterministic (assuming correct programming).

- **Checkpointing.** The state of the simulated components can be saved and restored.

- Availability. Creating a new machine is just a matter of copying the setup. There is no need to produce hardware prototypes or development boards.

- **Inspectability.** The complete state of the simulator can be investigated and monitored without disturbing the execution.

- **Sandboxing.** The simulation environment is completely isolated. No external variable can influence it and no code or data can escape unless explicitly allowed.

These attributes create an ideal environment for a system designer.

The coexistence of Configurability and Extendability expand the possible configurations for simulation beyond technological barriers. We can design software for hardware that is not yet in production (e.g. Linux was compatible with the AMD 64bit architecture before it became available [35]).

The attributes of Controlability, Determinism, Checkpointing and Inspectability create an ideal environment for debugging. Each flaw can be spotted, isolated and recreated until it is solved.

Finally, sandboxing erases any environmental causes that can influence a physical system and prevent disasters from failed experiments (i.e. aircraft computer systems, nuclear factory sensors).

A major feature for both the industrial and academic community is the availability of the simulated system. After an initial cost for creating the setup, duplication comes with zero cost in time or budget. This can also be used to mitigate the time overhead of simulation by running multiple experiments in parallel. In addition, the development of a software description of the system is much faster than an actual physical implementation, thus the whole design process is boosted.

### 5.3 An overview of the M5 simulator

For the purposes of our research we used and extended the M5 simulator [16, 11]. M5 is described from its main site as "a modular platform for computer system architecture research, encompassing system-level architecture as well as processor microarchitecture".

M5 is a full-system simulator that initiated at the University of Michigan. Until now it consists of around 180K (C++ & Python) lines of code, is freely distributed under a BSD-style license and has no dependency to any commercial or restrictive license software. These features make the M5 simulator an ideal tool for research on an academic environment and a great contribution to free and open source software.

As a framework, M5 is an event-driven simulator centered around a main event queue where all modules schedule their events. The implementation is heavily object oriented; all simulated components (i.e. CPUs, Caches) as well as their internal structures are instantiated as objects. This is the key to M5's modularity and flexibility.

M5 uses Python to initialize the simulation and configure the scheme of the SUT. For this to be feasible all simulated objects developed in C++ are wrapped using  $SWIG^1$  and exported as Python interfaces for use on the system configuration process. The configuration scripts are semi declarative, hiding all the unnecessary information about how the modules connect and communicate. The simulators capabilities scale from uni-/multi- processor system to multisystem systems without much overhead for creating the configuration.

Along with the scalability of configurations we can also choose from multiple object implementations based on our need for accuracy. For example, we can choose from 3 different CPU models, an 1 CPI CPU with atomic memory accesses, an 1 CPI CPU with detailed memory accesses and a full OoO Superscalar CPU based on the ALPHA 21264 processor.

Apart from the level of abstraction in the implementation, M5's uniform (method-based) API across object types enables us to interchange similar simulated objects. The simulation can start with a simple, functional CPU (so as to speed up the initialization process of the experiment) and then change into a more detailed model from which we will acquire our statistics and results. Moreover, M5 features a detailed event-driven memory system able to model complex multi-level cache hierarchies coupled with a coherence protocol implementation. Together, all these modules give a vast amount of possible composition of custom/complex systems for simulation.

In order to enable the easy expansion of its capabilities the simulator has been developed from the start so that it would not be coupled with any ISA increasing the number of applications and OS that could be used with it. Currently, the Alpha, SPARC, MIPS, ARM and x86 ISAs are supported.

Finally, one of M5's most appealing features is its full system simulation capabilities (M5 successfully simulates systems running an unmodified version of the Linux kernel). With full system simulation we are able to perform realistic simulation of the concurrent execution of applications on top of an operating system; in our case, to get a more detailed insight of specific parts of applications, the OS and their behavior under the influence of faults.

<sup>&</sup>lt;sup>1</sup>Simplified Wrapper and Interface Generator: A software development tool that connects programs written in C and C++ with a variety of high-level programming languages

All the above features conveyed us in choosing M5 as the most suitable simulator for experimenting and implementing our fault injection framework. Even though other full system simulators support fault injection, our framework is unique in that it covers a substantial amount of errors and provides high injection precision. Also, it is provided under a free-software license enabling modification and experimentation by anyone.

# Chapter 6

# Generic Processor Fault Model

After explaining the reasons for choosing M5 as the base for our fault injection framework, in this section we provided an overview of the fault model on which we based our implementation. In general, proving the sufficiency of a fault model is very difficult. It is more realistic to assume that a fault model is sufficient and justify this assumption to the greatest extent possible with experimental and historical data or results published in literature.

To this end, Yount and Siewiorek [58, 57] developed a very generic fault model for the register file within a processor which Johnson, Cutringht and DeLong [18] have augmented through simulations [58, 57] so as to fully explain the results of their test.

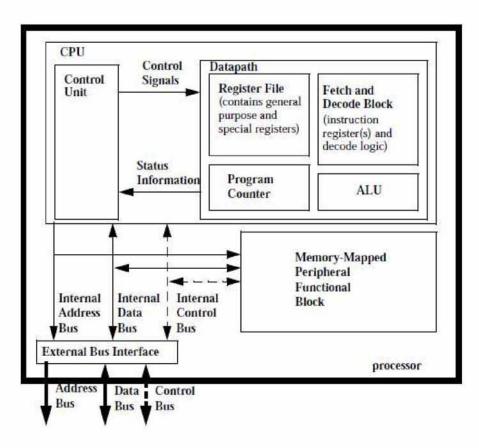

The augmented generic behavioral-level fault model describe the faulty behavior of a general-purpose, implementation-independent processor like the one shown in Figure 6.1

The full model consists of seven locations where faults can manifest:

- 1. Register File

- 2. Program Counter

- 3. Control Unit/Instruction Decode

- 4. Bus

- 5. ALU

- 6. Fetch and Execute

- 7. Memory Mapped peripheral functional block

The framework that we developed covers only 4 of those locations for fault injection (1, 2, 3, 5). Following, a description of the attributes - where, when, what - of each fault model that we implemented will be given. Excerpts from the following text are taken from [18] where a detailed presentation of the model can be found.

Figure 6.1: General processor diagram [18]

### 6.1 Register File Fault Model

#### 6.1.1 Register Fault Model

The register fault model covers corruptions in the registers of the CPU. These can be general or special purpose registers.

#### Where

One or more registers of the CPU is/are potential candidate for corruption.

#### When

Corruption can occur at an instruction boundary.

#### What

There are four scenarios on how the structure's value can be corrupted:

1. Missed load (6.1) all or part of a register is not loaded when it should be.

$$R_k \leftarrow expr \Rightarrow R_k \leftarrow (expr \bigoplus (mask\langle (w-1) \dots 0 \rangle))$$

(6.1)

2. Extraneous load (6.2) all or part of a register is loaded when it should not be.

$$R_k \leftarrow expr \Rightarrow R_j \leftarrow expr \quad \exists (j \neq k) \tag{6.2}$$

3. Level change in storage (6.3) the value of one or more bits in the register is complemented.

$$R_k \Rightarrow R_k \bigoplus (mask \langle (w-1) \dots 0 \rangle)$$

(6.3)

4. All 0/1 (6.4) Assign the value of all zeros and all ones to the register.

$$R_k \Rightarrow R_k \bigoplus R_k$$

$$R_k \Rightarrow R_k \bigoplus \overline{R_k}$$

(6.4)

### 6.1.2 Read/Write Register Selection Fault Model

The read/write register selection fault model covers faults within the decoding stage of the pipeline where an error can result in selecting the wrong register to be used as an input/output operand to the current operation (6.5)(6.6).

$$(R_k \leftarrow R_i opR_j) \Rightarrow (R_k \leftarrow R_x opR_j) \quad \exists (x \neq i) (R_k \leftarrow R_i opR_j) \Rightarrow (R_k \leftarrow R_i opR_x) \quad \exists (x \neq j)$$

$$(6.5)$$

$$R_k \leftarrow R_i op R_j \Rightarrow (R_x \leftarrow R_i op R_j) \quad \exists (x \neq k) \tag{6.6}$$

#### Where

Instructions during the fetch and decoding stage.

#### When

Corruption can occur at an instruction boundary.

#### What

The corruption that will result to a read or write register selection error are shown in equations (6.7) and (6.8) respectively.

$$instr_fetch(addr) \Rightarrow \\ \bigoplus_{(((x-a-i)@0)\#mask\langle (i+a-1)\dots i\rangle \# (i@0)),} (6.7)$$

$instr\_fetch(addr) \Rightarrow$

$$instr_fetch(addr)$$

$$(6.8)$$

$$(((x-b-j)@0)#mask\langle (i+b-1)\dots i\rangle \#(j@0)),$$

where x is the instruction width, i/j is the starting position of input/output register selection filed, a/b is the register selection field width, v@0 stands for repeating zero (0) v times and # stands for concatenate.

### 6.2 Program Counter Fault Model

The Program Counter (PC) fault model covers corruptions of the Program Counter of a CPU.

#### Where

The processor's Program Counter register.

#### When

Corruption can occur at an instruction boundary.

#### $\mathbf{What}$

There are three scenarios on how the structure's value can be corrupted:

1. **Missed load** (6.9) All or part of a register is not loaded when it should be.

$$PC \leftarrow expr \Rightarrow PC \leftarrow (expr \bigoplus (mask\langle (w-1)\dots 0 \rangle))$$

(6.9)

2. Level change in storage (6.10) The value of one or more bits in the register is complemented.

$$PC \Rightarrow PC \bigoplus (mask\langle (w-1)\dots 0 \rangle)$$

(6.10)

3. All 0/1 (6.11) Assign the value of all zeros and all ones to the register.

$$PC \Rightarrow PC \bigoplus PC$$

$$PC \Rightarrow PC \bigoplus \overline{PC}$$

(6.11)

# 6.3 Control Unit/Instruction Decode Fault Model

The Control Unit/Instruction Decode fault model covers corruptions of similar type to the read/write register fault model and mainly refers to corruption of the opcode field.

#### Where

Any location where an instruction may reside (i.e. memory, instruction register).

#### When

Corruption can manifest at an instruction boundary or on a memory reference.

#### What

The corruption that will result in a fetch/decode error is described in equations (6.7)

$$instr\_fetch(addr) \Rightarrow \\ \bigoplus_{(((x-c-k)@0)\#mask\langle (k+c-1)\dots k\rangle \# (k@0))} \\ (6.12)$$

where k is the starting position of the operation code field, and c is the width of the operation code. Note that values for k and c may vary, depending on the format of a given instruction.

### 6.4 ALU Fault Model

The ALU fault model covers corruptions in the ALU module of the processor, based on a general arithmetic instruction format such as (6.13)

$$D \leftarrow S_1 op S_2, \tag{6.13}$$

where D is the destination for the result of the operation (i.e. a register or a memory location) and  $S_1$ ,  $S_2$  are the sources for the operation again of the same possible types as the destination.

We define as possible locations for corruptions D ,  $S_1$  , and  $S_2$  , as well as the operation itself, which could be corrupted to another valid instruction or an invalid instruction.

The behavior of the ALU fault model can be defined as a subset of the other fault models behavior and thus expressed through them.

# Chapter 7

# Implementation

In the introductory section we gave a brief overview of the reliability problems that arise with aggressive feature, voltage and frequency scaling and highlighted the importance of understanding how the function of each abstraction layer in computer systems is affected by such faults. The characterization and modeling of the errors will enable us to design and implement feasible solutions to preserve the current levels of system's robustness.

In order to assess the impact of faults to each layer, new tools need to be developed or the existing ones should be enhanced. An example of such a tool is M5, the full system, cycle-accurate simulator with broad acceptance in the area of performance analysis that we described in Section 5.3. To avoid reinventing the wheel we augmented its existing infrastructure with fault injection capabilities, following the general processor fault model described in Chapter 6. The end-result is a modular and configurable framework for studying the effect of transient faults in reliability of applications. In addition, the developed framework can be used for the evaluation of new fault tolerance techniques or to calculate the robustness of a system through fault injection campaigns which can be automated using the provided tools and API.

The framework was developed using C++ and employed the *SWIG* library for exporting the instrumentation API to the configuration interface of M5, thus creating a uniform development environment for the simulator and the fault injection framework. We should note here that fault injection is currently only supported in the ALPHA ISA. However, porting it to other ISAs does not require extensive modification as the only ISA-depended portion of the framework is the functions used to distinguishing processes/threads and user/privileged mode execution.

In the following Sections, we will attempt to give a general description of fault injection frameworks and present implementation details and choices that were made for the development of our tool.

### 7.1 Introduction: Where, When, What

Fault injection's instrumentation variables can be divided into three basic categories [23]:

1. Where: The location of the injected fault.

- 2. When: The time when the fault should manifest.

- 3. What: The nature of the fault; the way that the faulted structure will be influenced.

#### 7.1.1 Where

The first aspect that we need to clarify when creating a fault injection scenario is the location of the faults, namely the modules/structures that will be targeted. A good method for selecting injection targets is the top-down approach; that is, we first select the high-level unit (CPU, DRAM module), then we proceed with internal modules and finally pick a single bit that will be affected. Common locations for fault injection are the levels of memory hierarchy, special and general purpose registers, control logic and pipeline stages of a processor (fetch, decoding and execution).

The location where a fault will be injected is crucial, as it partially defines/bounds the possible errors that can be created[24]. As different modules have different functions and process different types of data, we can create groups that contain all the possible errors for each structure, however, we should note that some interleaving does exist between errors in different structures.

A fault occurring in a register (integer, floating point or special purpose) will affect its internal storage and in the case of miscellaneous register the processor state (e.g. corruption of the processor's execution mode register).

A fault at a memory location will affect its internal storage and possibly the execution and output of a process that uses its content.

A fault at the fetch and decoding stage will affect the decoding of the instruction (i.e. register selection, operation selection (e.g. Table 7.1), immediate value).

A fault at the execution stage will affect the result of the ALU operation and the content of the destination register or memory location, or -in the case of program control instruction- a wrong path can be taken.

| Mnemonic | Format | Opcode (hex) | Function Code (hex) | Description                                             |

|----------|--------|--------------|---------------------|---------------------------------------------------------|

| BEQ      | Bra    | 39           | -                   | Branch if = zero                                        |

| BGE      | Bra    | 3E           | -                   | $\begin{array}{c c} Branch & if \\ >= zero \end{array}$ |

| BGT      | Bra    | 3F           |                     | Branch if > zero                                        |

| BIC      | Opr    | 11           | 08                  | Bit clear                                               |

| BIS      | Opr    | 11           | 20                  | Logical sum                                             |

| BLBC     | Bra    | 38           | 22                  | Branch if<br>low bit clear                              |

Table 7.1: Qualifiers for operate instructions, excerpt from Table A-2[17]

In general, the location of an injection is described deterministically and the spatial distribution of faults in the simulated modules is produced by a distribution function. The distribution function can be derived from low level characterization of the hardware's behavior under different internal and external conditions (i.e. radiation, thermal distribution, utilization). Alternatively, statistical fault injection can be used as shown in [37]. Note that most fault injection frameworks are evaluated through statistical fault injection and not by strict mathematical proof of their correctness.

#### 7.1.2 When

Another essential variable in a fault injection campaign is the timing of the injections; the time that a fault will occur (manifest).

Faults can be set to occur based on the value of a system variable. Commonly used variables are overall simulation time, processor cycles, executed/fetched instructions or occurrence of a specific addresses in the Program Counter (PC).

The flexibility in setting the manifestation time of a fault is of great importance when one is interested in acquiring targeted results; for example, when we are interested in studying specific regions of an application.

However, fault manifestation based on simulation time, clock cycles and fetched instructions is not deterministic especially when done on a full system multi-core simulation environment, where multiple applications are running and no control over their scheduling in time and hardware is possible. As a more precise timing method the PC value can be used.

Similarly to the location variable, the timing variable of the injection can be generated from temporal distribution models of hardware faults (module error rate) or statistical methods (e.g. uniform, logarithmic distribution function).

#### 7.1.3 What

The final fault injection instrumentation variable that we will describe is the nature of the fault; how the structure's value will be corrupted. As faults manifest in different ways, based on their cause, we need to use different models for each type of hardware fault.

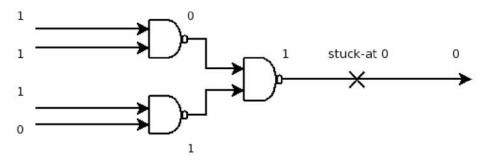

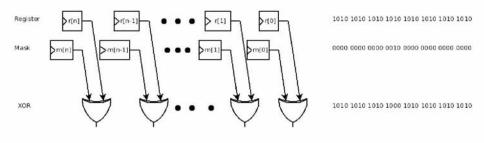

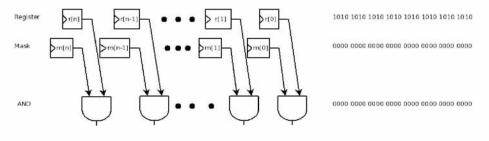

The most common way to model permanent faults is the stuck-at model[30] where a signal is permanently set (stuck) to one (1) or zero (0) (Figure 7.1). Transient faults are modeled using the bit-flip model[41] where a bit's value is flipped to its complement (Figure 7.2).

Figure 7.1: Stuck-at model illustration

Figure 7.2: Bit-flip model illustration [41]

Except from these two methods, more accurate models can be used for modeling hardware faults. Recent research results show an increase in multi-bit [21] and circuit timing errors that are not covered by the above fault models.

### 7.2 Our Implementation

Having explained the aspects of fault injection instrumentation, we will try to place our implementation details in the general picture. For the development of our tool we abhered to the object oriented approach of the M5 simulator. The framework is composed of classes that define different fault types and fault queues where the objects are stored for quick access and easy manipulation.

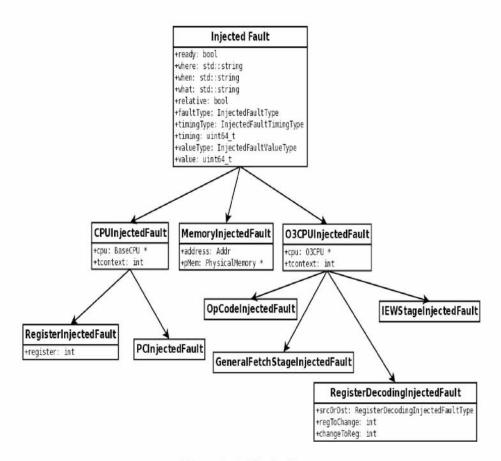

The hierarchy of fault types that our framework currently supports is depicted in Figure 7.3. All fault objects derive from the *InjectedFault* class that contains the basic variables for fault injection and the generic attributes of a fault. The *InjectedFault* class derives from the *SimObject/MemObject* classes so that we can use the fault injection objects at the configuration interface. More details about each fault type will be given later.

A core component of the fault injection framework is the queue structure. All faults described at the configuration file are inserted in 4 queues, based on their characteristics; execution, fetch, decode and other. The queues are constructed at the beginning of the simulation and are global to the framework and the simulator. The queue class provides public functions for inserting, removing and searching a fault (based on injection time and location). In addition, to improve performance the faults are kept in a descending order to decrease the average search time.

At the initialization of the simulation the configuration file is parsed and simulation objects are created for all described components. All faults that can be scheduled at that point are send in the global event queue of the simulator or a processor's instruction event queue. Faults that manifest on a specific cycle are pushed into the *mainEventQueue* and faults that manifest based on a CPU's fetched instruction count are pushed into the CPU's *comInstEventQueue*. All other instances are kept in the queues that are scanned in every cycle to find if any fault instance is ready to manifest. The scanning of the queues is done independently for each pipeline stage in order to support injection in-between them. This is the main reason we altered the source code of the CPU models, even though are initial approach was to avoid any changes to existing M5 code.

Figure 7.3: Fault classes

Another feature of our framework is "Relative Fault Injection", that is, faults can be set to manifest relatively to the value of a processor's variable. To enable relative fault injection an extra instruction has been added to the ISA, namely  $f_{i\_vaddr\_inst^1}$ .

The *fi\_vaddr\_inst* instruction is used to set a relative point for fault injection. When executed by the processor it stores the PC address, Tick cycles and fetched instructions number so that these values can be used as reference points in the injection of relative faults.

At the section where we described the timing of an injection (When) we mentioned the importance/need of bounding faults' occurrence. In our implementation this is supported through the use of another instruction that was introduced to the ISA,  $f_{i\_activate\_inst^2}$ , and a function of the M5 simulator namely inUserMode().

The *fi\_activate\_inst* is used to enable and disable the manifestation of faults. More specifically, when inserted in a code its first occurrence enables the manifestation of faults for the specific process/thread and the second one disables it. To achieve such behavior we exploit the Process Control Block

$<sup>^{1}</sup>f_{vaddr_{inst}} \rightarrow \operatorname{asm}(".long 0x04XXX67")^{3}$

$<sup>^{2}</sup>fi\_activate\_inst \rightarrow asm(".long 0x04XXXX66")^{3}$

<sup>&</sup>lt;sup>3</sup>The Xs can be of any value.

(PCB) address <sup>3</sup>, which is unique for each process/thread. Whenever a fault event tries to manifest, we search using the PCB address as a key on a hash table that contains the processes/threads for which fault injection has been enabled.

For the needs of our experiments we used an already implemented function of the M5 simulator, the *inUserMode()* function. *inUserMode()* returns true if the processor is currently in user mode, thus enabling us to restrict faults in user mode application code; in the same way we are able to inject faults only to operating system code. As we were not interested in injecting faults in the OS, by-default our framework isolates fault injection to the user mode of the processor. However, this feature can easily became a run-time argument of the configuration file.

#### 7.2.1 Where

As described previously (Chapter 6), our implementation is based on the generic processor fault model described in [18]. It supports fault injection in memory locations, registers and the fetch, decode and execution stages of an instruction.

All the possible locations for fault injection, according to [18], are shown in table 7.2; the supported locations are marked with a  $\sqrt{}$ .

| Faults                              | Status       |

|-------------------------------------|--------------|

| Register File                       | $\checkmark$ |

| Program Counter                     | $\checkmark$ |

| Memory Unit                         | $\checkmark$ |

| Control Unit                        | $\checkmark$ |

| Fetch & Decode Logic Block          | ×            |

| Internal Data Bus, Internal Address | ×            |

| Bus, and Internal Control Bus, as   |              |

| well as the External Bus Interface  |              |

| ALU                                 | $\checkmark$ |

| Memory-Mapped Peripheral Devices    | ×            |

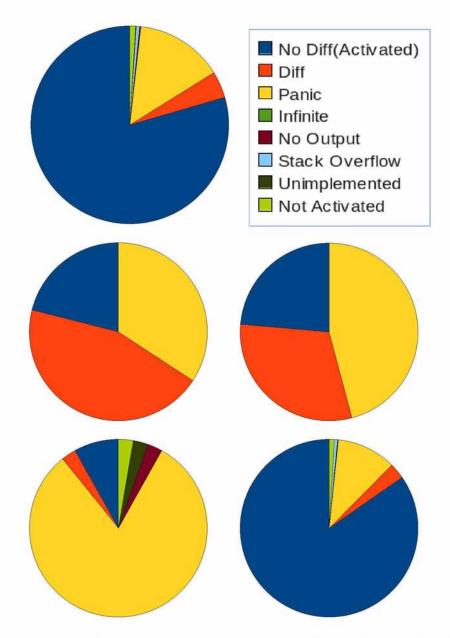

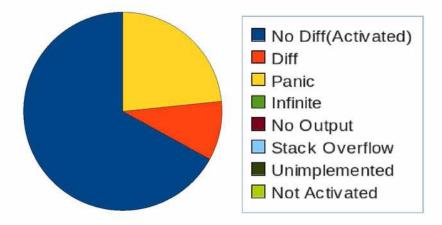

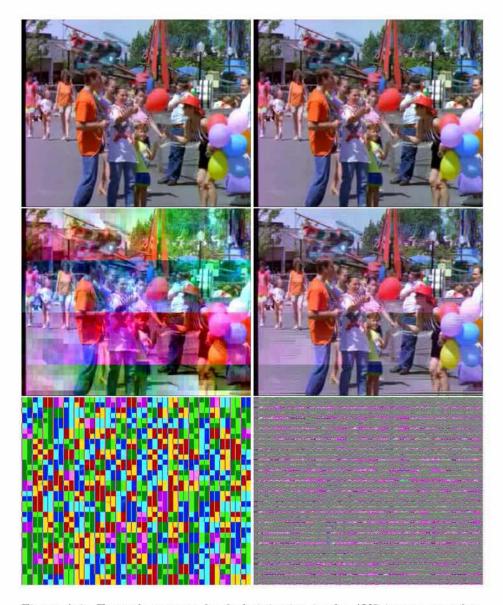

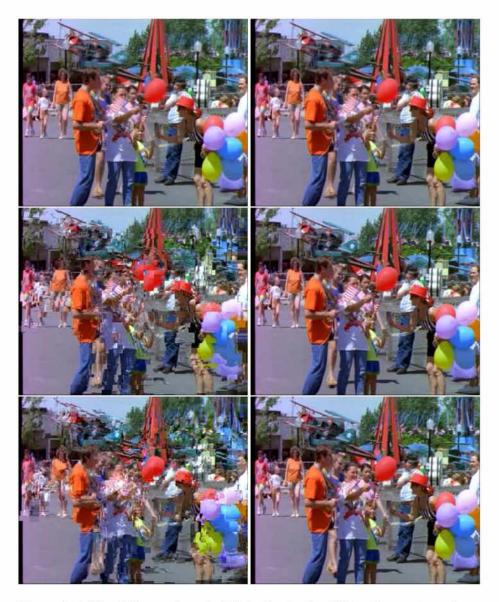

Table 7.2: Modules where fault injection is supported