## ΠΑΝΕΠΙΣΤΗΜΙΟ ΘΕΣΣΑΛΙΑΣ

# ΤΜΗΜΑ ΜΗΧΑΝΙΚΩΝ Η/Υ, ΤΗΛΕΠΙΚΟΙΝΩΝΙΩΝ ΚΑΙ ΔΙΚΤΥΩΝ

# Χρήση Μοντέλου Παράλληλου Προγραμματισμού για Σύνθεση Αρχιτεκτονικων

Μια εργασία που εκπονήθηκε από τον Muhsen Owaida για τις απαιτήσεις του Διδακτορικού Διπλώματος.

Επιβλέπων Καθηγητής: Αν. Καθηγητής, Νικόλαος Μπέλλας

Βόλος, Αύγουστος 2012

# Acknowledgement

The work of this dissertation has been one of the most significant academic challenges I have ever had to face. Without the support, patience and guidance of the kind people around me this dissertation would not have been completed.

First of all, my enormous debt of gratitude goes to my thesis advisor and mentor, Professor Nikolaos Bellas. Throughout the period of my PhD studies, Professor Bellas was there for me to actively support and guide me toward taking the best possible decisions and to develop to a much better researcher. I am thankful for his patience and immense knowledge and help in writing this dissertation. I am especially thankful to him for his mentorship and friendship throughout these years.

I owe sincere and earnest thankfulness to my committee member, Professor Christos D. Antonopoulos for his constant guidance and insightful comments which have been invaluable on both an academic and a personal level, for which I am extremely grateful. It has been a great privilege for me to work under his guidance.

I would like to express my sincere gratitude to my committee member, Professor Georgios Stamoulis for his assistance and guidance in getting my PhD studies started. I would like to thank also my colleagues and fellow students, especially Konstantis Daloukas and Charalambos Antoniadis for their help and cooperation in my research. I would like to thank the staff of the Department of Computer and Communication Engineering at the University of Thessaly for their support and constant encouragement.

Finally, I wish to thank my family, who have always believed in me and helped me to reach my goals. Their support forged my desire to achieve all that I could in life.

I would like to acknowledge the financial support of the Greek State Scholarship Foundation (IKY) throughout the period of my PhD studies, which without it this research would not have begun.

dedicated to my family

# TABLE OF CONTENTS

| TABLE OF C              | CONTENTS                                              | ]   |

|-------------------------|-------------------------------------------------------|-----|

| LIST OF FIG             | URES                                                  | IV  |

| LIST OF TA              | BLES                                                  | V   |

| LIST OF ALC             | GORITHMS                                              | VII |

| -                       |                                                       |     |

|                         |                                                       |     |

| INTRODUCT               | TION                                                  | 1   |

| 1.1 B                   | ackground                                             |     |

| 1.1.1                   | Modern Parallel and Heterogeneous Computing           |     |

| 1.1.2                   | FPGA-based Computing Platforms                        |     |

| 1.2 RES                 | EARCH OBJECTIVE AND CONTRIBUTION                      | 5   |

| 1.3 THE                 | SIS STRUCTURE                                         |     |

| CHAPTER 2               |                                                       | 9   |

|                         | PENCL TOOL FLOW                                       |     |

|                         |                                                       |     |

|                         | DL FLOW AND INFRASTRUCTURE                            |     |

|                         | NCL PROGRAMMING MODEL                                 |     |

| 2.2.1                   | Overview                                              |     |

| 2.2.2                   | Computation Model                                     |     |

| 2.2.3                   | Synchronization                                       |     |

| 2.2.4                   | OpenCL Memory Structure                               |     |

|                         | NCL TO C TRANSFORMATION                               |     |

| 2.3.1<br>2.3.2          | Logical Threads Serialization                         |     |

| 2.3.2<br>2.3.3          | Loop Fission                                          |     |

| 2.3.3<br>2.3.4          | Variable Privatization                                |     |

|                         | Output C function structureVM COMPILER INFRASTRUCTURE |     |

| 2.4 LLV<br>2.4.1        | ILLVM Intermediate Representation (LLVM-IR)           |     |

|                         | ATED WORK                                             |     |

|                         |                                                       |     |

| CHAPTER 3               |                                                       | 30  |

| ARCHITECT               | TURAL TEMPLATE                                        | 30  |

|                         | RVIEW                                                 |     |

| 3.2 HIG                 | H LEVEL ARCHITECTURE                                  |     |

| 3.2.1                   | Hierarchical Structure                                |     |

| 3.2.2                   | Interconnection network                               |     |

|                         | CESSING ELEMENT (PE) ARCHITECTURE                     |     |

| 3.3.1                   | Datapath and AGU Modules                              |     |

| 3.3.1.1                 | Functional Units                                      |     |

| 3.3.1.2                 | Storage Units                                         |     |

| 3.3.1.3<br><b>3.3.2</b> | Control Unit                                          |     |

| 3.3.2.1                 | Stream Interface Unit.                                |     |

| 3.3.2.1                 | Input Streaming Units Output Streaming Units          |     |

| 3.3.2.2                 | Local Cache                                           |     |

| 3.4   | Con     | TROL ELEMENT (CE) ARCHITECTURE                 | 46         |

|-------|---------|------------------------------------------------|------------|

| 3.4   | 4.1     | Functional and Storage Units                   | 47         |

| 3.4   | 4.2     | Control Unit                                   | 48         |

| 3.4   | 4.3     | Streaming Interface                            | 49         |

| 3.5   | EXE     | CUTION MODEL                                   | 50         |

| 3.6   | REL     | ATED WORK                                      | 53         |

| CHAD' | TED 4   |                                                | <b>5</b> 0 |

|       |         |                                                |            |

| SILIC | ON OP   | PENCL BACKEND                                  | 58         |

| 4.1   | Віту    | WIDTH OPTIMIZATION                             | 58         |

| 4.2   |         | DICATION                                       |            |

|       | 2.1     | Overview                                       |            |

|       | 2.2     | Prior Work                                     |            |

|       | 2.3     | Predication Algorithm                          |            |

|       | 4.2.3.1 | If-conversion algorithm                        |            |

|       | 4.2.3.2 | <u> </u>                                       |            |

| 4.3   | Con     | DE SLICING                                     |            |

|       | 3.1     | Overview                                       |            |

|       | 3.2     | Slicing Algorithm                              |            |

| 4.4   |         | FRUCTION CLUSTERING                            |            |

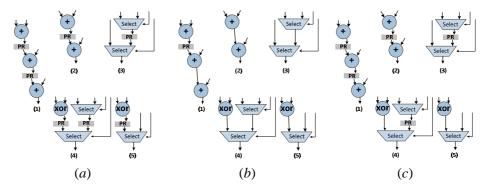

|       | 4.1     | Overview                                       |            |

|       | 4.2     | Grammar Generation                             |            |

|       | 4.4.2.1 | Grammar Representation                         |            |

|       | 4.4.2.1 | Generation of Grammar-based DFG representation | 73         |

|       | 4.4.2.3 | Computational Complexity and Correctness       |            |

|       | 4.3     | Grammar-Driven Datapath Synthesis Flow         |            |

|       | 4.4.3.1 | Data Flow Graph Slicing                        |            |

|       | 4.4.3.2 | Grammar Generation & Selection                 |            |

|       | 4.4.3.3 | Macro Functional Unit Pipelining               |            |

|       | 4.4.3.4 | Scheduling and Implementation                  |            |

| 4.5   | SCH     | EDULING                                        |            |

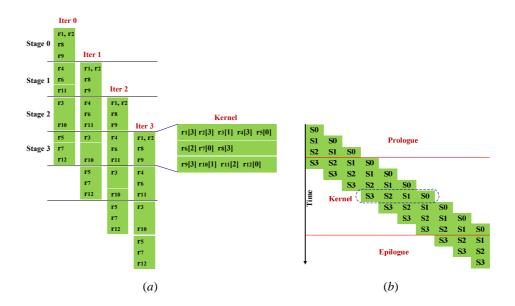

| 4.5   | 5.1     | Modulo Scheduling                              | 92         |

|       | 4.5.1.1 | Overview                                       |            |

|       | 4.5.1.2 | Swing Modulo Scheduling                        | . 94       |

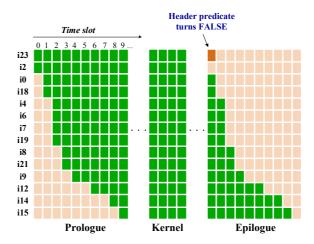

|       | 4.5.1.3 | Hardware Support                               | . 95       |

| 4.6   | CAC     | CHE INSTANTIATION                              | 96         |

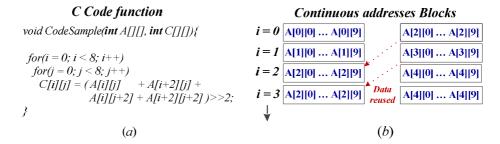

| 4.0   | 6.1     | Memory Addresses Profiling                     | 96         |

| 4.6   | 6.2     | Cache Configuration Computation                |            |

| 4.7   | Loc     | AL BUFFERS SYNCHRONIZATION                     | 99         |

| 4.8   | REL     | ATED WORK1                                     | 103        |

| CHAD' | TED 5   | 1                                              | ι 1Λ       |

|       |         |                                                |            |

| EXPE  | RIMEN   | NTAL EVALUATION1                               | 110        |

| 5.1   | BEN     | CHMARK SUITE1                                  | 110        |

| 5.2   | MET     | THODOLOGY                                      | 113        |

| 5.3   |         | CUTION MODEL EVALUATION                        |            |

| 5.4   |         | WIDTH OPTIMIZATION EVALUATION                  |            |

| 5.5   |         | FRUCTION CLUSTERING EVALUATION                 |            |

| 5.6   |         | CHE ALLOCATION EVALUATION                      |            |

| 5.7   |         | CRALL PERFORMANCE ANALYSIS AND COMPARISONS     |            |

|       |         |                                                |            |

|       |         | 1                                              |            |

| CONC  | LUSIC   | ONS AND FUTURE WORK1                           | 134        |

| DIDI IOOD ADIIX  | 7 | 12  | 7 |

|------------------|---|-----|---|

| - BIBLIUUTKAPH Y | Y | 1.3 | 1 |

# **LIST OF FIGURES**

| Number                                                                        | Page |

|-------------------------------------------------------------------------------|------|

| Figure 1.1: Heterogeneous System.                                             | 3    |

| Figure 1.2: FPGA fabric basic components.                                     |      |

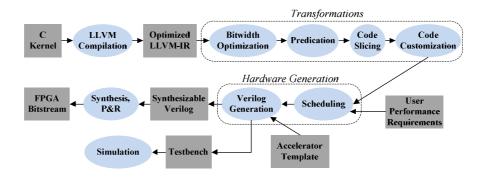

| Figure 2.1: Silicon-OpenCL Tool Flow.                                         | 9    |

| Figure 2.2: SOpenCL Low Level Compiler (SOpenCL-LLC)                          | 10   |

| Figure 2.3: C-to-RTL backend.                                                 | 11   |

| Figure 2.4: OpenCL Platform Model.                                            |      |

| Figure 2.5: 2-dimensional computations grid geometry (N = 2)                  | 12   |

| Figure 2.6: Chroma Interpolation OpenCL kernel                                | 13   |

| Figure 2.7: Matrix Multiplication OpenCL kernel example.                      |      |

| Figure 2.8: OpenCL memory hierarchy.                                          |      |

| Figure 2.9: Logical Threads Serialization.                                    |      |

| Figure 2.10: Loop Fission example                                             |      |

| Figure 2.11: Barrier Elimination examples.                                    |      |

| Figure 2.12: Variable privatization example                                   |      |

| Figure 2.13: OpenCL kernel for LU Decomposition.                              | 21   |

| Figure 2.14: LLVM compiler Infrastructure                                     | 22   |

| Figure 2.15: SSA Representation.                                              | 23   |

| Figure 2.16: LLVM-IR Example.                                                 |      |

| Figure 3.1: Motion Compensation Block Manual design.                          | 31   |

| Figure 3.2: Program structure of LU Decomposition kernel                      | 32   |

| Figure 3.3: Interconnect communication channels                               |      |

| Figure 3.4: Processing Element (PE) architectural template                    | 36   |

| Figure 3.5: Datapath of the $PE(L_{I \mid 0})$ module in Figure 3.2b          | 37   |

| Figure 3.6: $L_{I_{-}0}$ Loop C source code in Figure 3.2a                    | 39   |

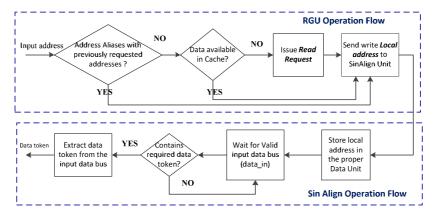

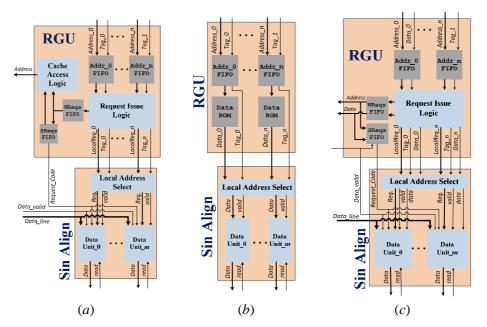

| Figure 3.7: $RGU$ and $SinAlign$ modules operations flow                      | 41   |

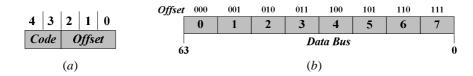

| Figure 3.8: Local Address Encoding                                            |      |

| Figure 3.9: RGU and SinAlign modules configurations                           | 42   |

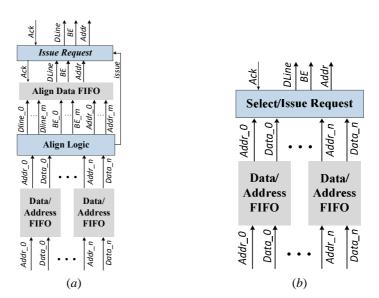

| Figure 3.10: SoutAlign module                                                 |      |

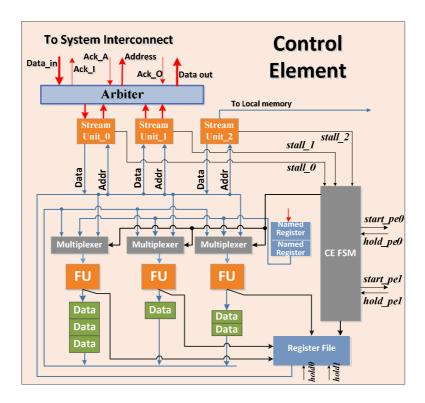

| Figure 3.11: Control Element Architectural Template                           | 47   |

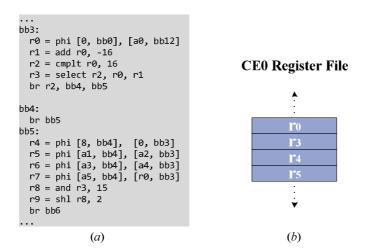

| Figure 3.12: CE Register File allocation.                                     |      |

| Figure 3.13: CE Stream Unit Configurations.                                   | 49   |

| Figure 3.14: Synopsis of the FSM of CE0.                                      | 50   |

| Figure 3.15: Timing for a work-item execution.                                |      |

| Figure 3.16. Nested loop execution model                                      | 52   |

| Figure 3.17: PICO-NPA system.                                                 |      |

| Figure 3.18: Trident system target architecture.                              |      |

| Figure 3.19: Laura target architecture                                        |      |

| Figure 3.20: (a) ROCCC Module architecture model. (b) Optimus Filter template |      |

| Figure 3.21: MARC System Architecture                                         | 57   |

| Figure 4.1: SOpenCL backend transformations.                                  | 58   |

| Figure 4.2: Bitwidth optimization example                                     |      |

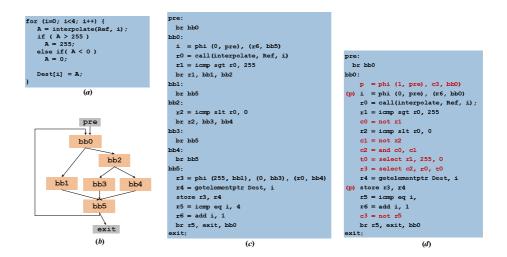

| Figure 4.3: IF-Conversion using LLVM assembly.                                |      |

| Figure 4.4: If-conversion transformation for value-clipping example           |      |

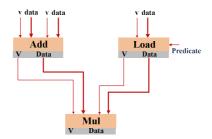

| Figure 4.5: Predicated execution architectural support                        |      |

| Figure 4.6: Programm slicing.                                                 | 65   |

| Figure 4.7: Code Slicing Example.                                             |      |

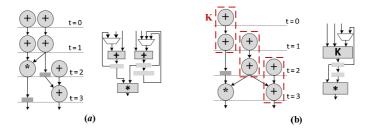

| Figure 4.8: Scheduling and binding of a DFG.                                  | 70   |

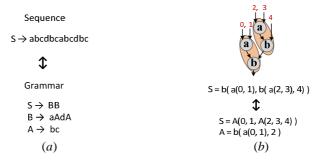

| Figure 4.9: Grammar representation                                            | 71   |

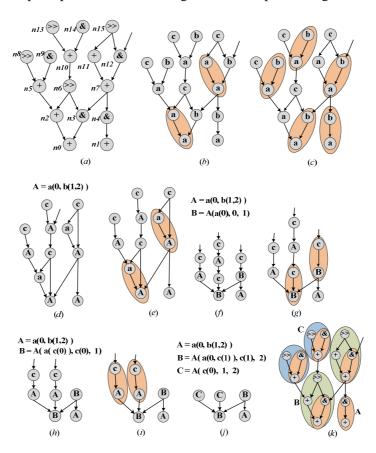

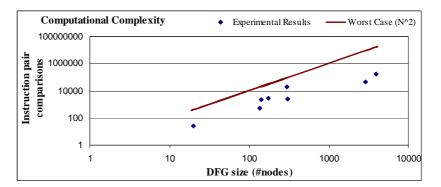

| Figure 4.10: Motivational example showing the steps of Algorithm 4.3                       | 75  |

|--------------------------------------------------------------------------------------------|-----|

| Figure 4.11: Experimental evaluation of the computational complexity of Algorithm 4.3      | 77  |

| Figure 4.12: Grammar based datapath synthesis flow.                                        |     |

| Figure 4.13: DFG slicing example                                                           |     |

| Figure 4.14: The selection process of Rules in the grammar of Figure 4.10                  | 84  |

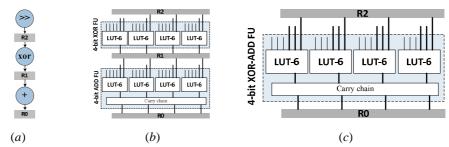

| Figure 4.15: MFU Pipelining Example                                                        | 84  |

| Figure 4.16: Experimental method micro-benchmarks                                          | 90  |

| Figure 4.17: Modulo Scheduling                                                             | 93  |

| Figure 4.18: Valid-bit flow over the loop execution duration for the kernel of Table 4.4   | 95  |

| Figure 4.19: Example of data reuse across outer loop iterations                            | 97  |

| Figure 4.20: Memory Dependency Graphs for LUD OpenCL architecture                          | 100 |

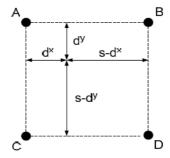

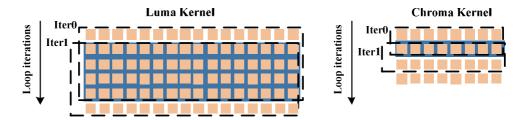

| Figure 5.1: Sub-pixel Chroma interpolation in AVS Motion Compensation                      | 111 |

| Figure 5.2: Simulation and Verification Testbench.                                         | 114 |

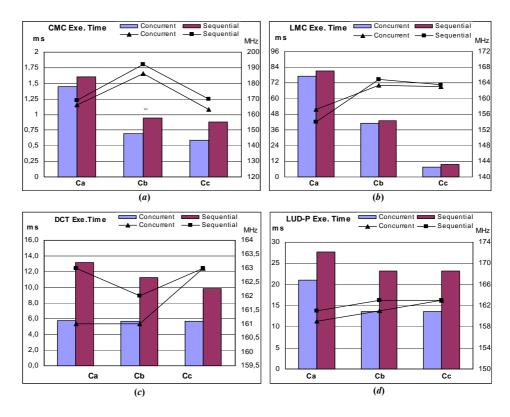

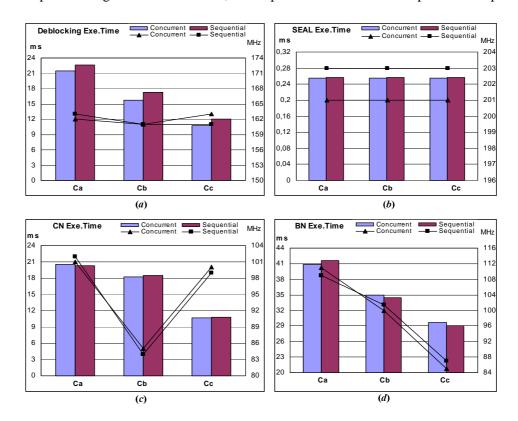

| Figure 5.3: Execution Time (bars in ms) And clock frequency (lines in MHz) for concurred   | nt  |

| and sequential configurations                                                              | 117 |

| Figure 5.4: Execution time (bars, in ms) And clock frequency (lines in MHz) for concurrent | nt  |

| and sequential configurations                                                              |     |

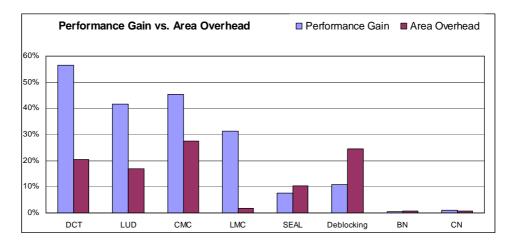

| Figure 5.5: Concurrent operation performance gain and area overhead                        | 119 |

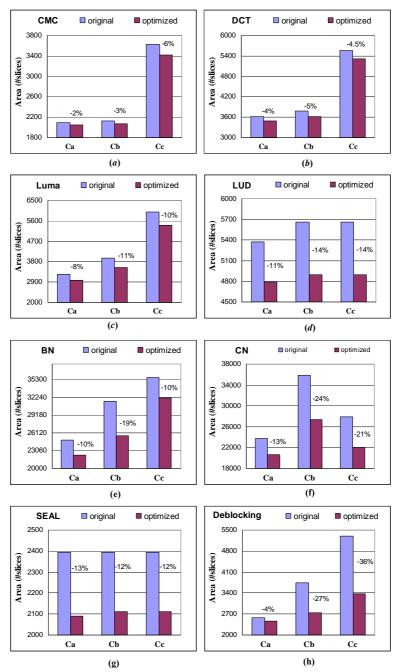

| Figure 5.6: Area results for Bitwidth optimization                                         |     |

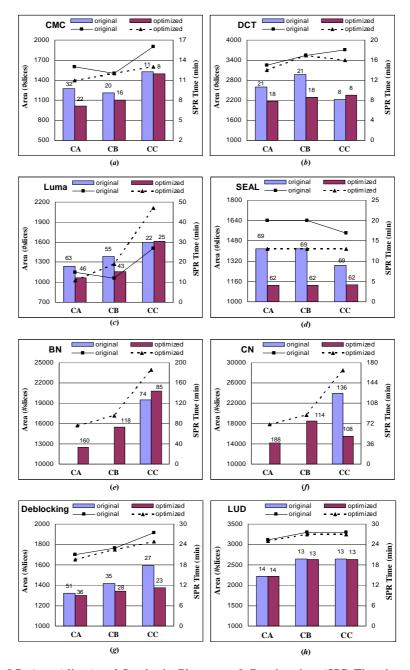

| Figure 5.7: Area (slices) and Synthesis, Placement & Routing time                          | 124 |

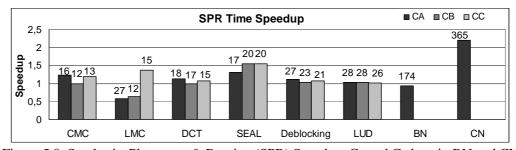

| Figure 5.8: Synthesis, Placement & Routing (SPR) Speedup                                   | 126 |

| Figure 5.9: Area Reduction (AR) correlation with the number of macro-instructions per      |     |

| grammar rule (a, c, e) and the DFG coverage (b, d, f).                                     |     |

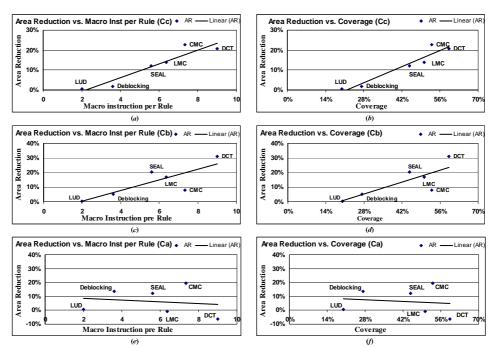

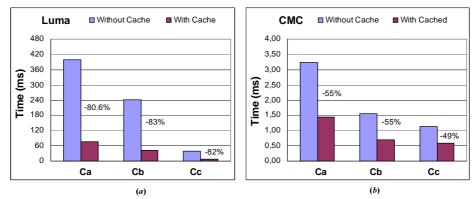

| Figure 5.10: Luma (LMC) and Chroma (CMC) kernels data reuse pattern                        | 129 |

| Figure 5.11: Execution time for LMC and CMC configurations with and without cache          | 130 |

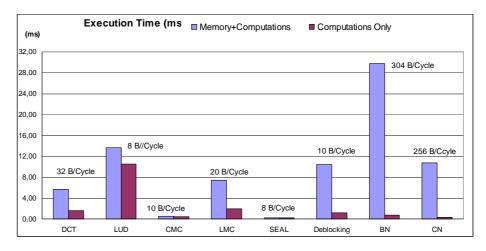

| Figure 5.12: Comparison of execution time for Memory transfers plus computations and       |     |

| computations only                                                                          | 131 |

# LIST OF TABLES

| Number                                                                                   | Page |

|------------------------------------------------------------------------------------------|------|

| Table 4.1: Experimentally derived values of the $A_l$ parameter                          | 88   |

| Table 4.2: Examples of the area consumed by a set of micro-benchmarks                    |      |

| Table 4.3: Examples of some micro-benchmarks critical path (ns).                         |      |

| Table 4.4: Modulo Scheduled kernel example                                               | 95   |

| Table 5.1: Applications used for experimental evaluation.                                | 110  |

| Table 5.2: Experimentation Data Set Size.                                                | 113  |

| Table 5.3: Concurrent/Sequential modes area results for the benchmarks implemented on    |      |

| Xilinx Virtex-6 LX760 device.                                                            |      |

| Table 5.4: Bitwidth optimization Frequency (MHz) results for the test kernels on Xilinx  |      |

| Virtex-6 LX760.                                                                          | 122  |

| Table 5.5: Grammar generation results on the kernels DFGs.                               | 122  |

| Table 5.6: Instruction Clustering Frequency (MHz) results for the test kernels on Xilinx |      |

| Virtex-6 LX760.                                                                          | 128  |

| Table 5.7: FPGA Slices for CMC and LMC kernels with and without cache                    |      |

| Table 5.8: SOpenCL based design of Deblocking filter compared to manual design           | 132  |

| Table 5.9: SOpenCL based design of SEAL kernel compared to manual design                 | 132  |

# **LIST OF ALGORITHMS**

| Number                                             | Page |

|----------------------------------------------------|------|

| Algorithm 4.1: If-conversion algorithm             | 62   |

| Algorithm 4.2: Code slicing algorithm              | 66   |

| Algorithm 4.3: Grammar Extraction Algorithm        |      |

| Algorithm 4.4: Grammar Rules Selection             |      |

| Algorithm 4.5: Custom Instruction Pipelining       |      |

| <b>Algorithm 4.6:</b> $A_l$ parameters estimation. |      |

| Algorithm 4.7: Redundant Dependency Elimination    |      |

## CHAPTER 1

### Introduction

#### 1.1 Background

### 1.1.1 Modern Parallel and Heterogeneous Computing

The ever increasing demand for more efficient computing has pushed the evolution of computing systems to spectacular levels over the last few decades. Advances in computing systems are the key to the development of new domains and revolutionary technologies, such as personalized medicine, online social interaction, and immersive entertainment experiences.

While appetite for high performance and more efficient computing is increasing, today's computing systems are struggling with technology limitations. The traditional way to improve performance by increasing clock frequency has already come to an end. As a result, computing systems are shifting towards energy-efficient parallel computation models. Using many slower parallel processors instead of a single high speed core has provided higher energy efficiency.

Parallel architectures developed over the last decade, can be classified into different categories. The first category includes multiple instances of the traditional general purpose processor have been arranged within the same chip to produce multi core processors (MCPs). Another category includes the Graphic Processing Units (GPUs) with hundreds of simple processing cores. Nvidia GeForce256 was the first GPU released on 1999 [1]. Finally, streaming/Vector processors are multi-core processors, specially designed for streaming applications. Streaming processors like *RSVP*, *Imagine*, *Raw*, *and Merrimac* [2, 3, 4, 5] promoted high performance computing by exploiting heavy data parallelism in streaming applications and employing a distributed memory model.

While the many-core processing hardware technology is progressing rapidly, software development for parallel computing is falling behind. The challenge rising with parallel computing systems is to port already developed software for sequential processors on the newly introduced multi- or many-core processors. To cope with the new architectural trends, the parallel computing industry has developed a variety of parallel programming languages to allow programmers to exploit the multiple execution contexts available in the new multi-core architectures. The first class of parallel programming languages like OpenMP and Posix threads are extensions of sequential programming models, suitable for systems with few processing cores, and are widely used in the industry. New parallel programming models have been invented in the last few years to better suit systems with hundred or thousands of cores. Languages such as OpenCL, CUDA or various streaming languages fit the second category.

Yet even the shift to parallel computing is not enough. Many-core chips suffer from high power density which restricts the number of cores that can be simultaneously active, a phenomenon called *dark silicon* [6, 7]. The dark silicon phenomenon puts limits on the prospect of building many-core chips with tens or hundreds of cores without significant degradation in efficiency. This inefficiency is promoting *heterogeneous parallel computing systems*.

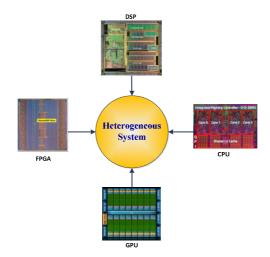

Instead of a parallel computing system built only from many-core chips, a heterogeneous computing system comprises multiple different computing components (Figure 1.1) each carefully optimized to efficiently execute a particular type of task. This heterogeneous parallel computing model presents an even greater challenge for developers. Now they must not only develop parallel applications, but they are responsible for deciding what types of processors to use for which calculations [6].

Heterogeneous systems development represents the best approach on energy-efficient high performance computing. However, it is a new technology that requires extensive research and effort mostly in developing tools and compilers to help software developers to deal with the large pool of architectural variables and parameters of heterogeneous systems. Other than the architectural differences of heterogeneous system components, their programming tools and languages exhibit

Figure 1.1: Heterogeneous System.

vast differences making it extremely difficult to develop applications that can be executed on all components. For example, porting an application on a heterogeneous system comprising MCPs, GPUs and FPGAs, requires the use of completely different programming languages; for example OpenMP for MCPs, CUDA for GPUs, and Verilog/VHDL for FPGAs

Recently, researchers in the parallel computing community have been moving towards unified programming models to support the heterogeneity of parallel computing platforms. *OpenCL* [22] is an industry-supported standard for building parallel applications that are portable across heterogeneous parallel systems. OpenCL adopts an architecture-agnostic computations model, promoting application portability across different platforms.

#### 1.1.2 FPGA-based Computing Platforms

The recent advances in FPGA technology have placed reconfigurable platforms on the map of heterogeneous computing. FPGA accelerators offer superior performance, power and cost characteristics compared to a homogeneous CPU-based platform, at the expense of complex and expensive software infrastructure. For instance, FPGAs have been shown to offer two orders of magnitude superior performance than conventional CPUs for a variety of data-intensive applications [8].

Research in the last few years provided strong evidence on FPGA high performance computing capabilities. Applications in medical imaging [9], networking [10], multimedia [11], and financial applications [12], have been successfully implemented on FPGA platforms achieving orders of magnitude speedup and energy-consumption reductions over CPU- and GPU-based solutions.

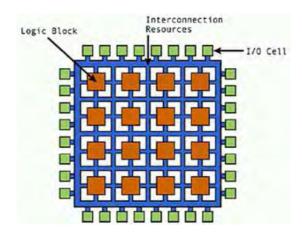

Distributed logic and memory components of FPGA devices bear a significant resemblance to many-core processors. FPGA reconfigurable fabric consists of a sea of programmable logic cells and interconnects organized in rows and columns (Figure 1.2). Recently, FPGA manufacturers have included hard IP cores, like multipliers and SRAM blocks, distributed within the logic cells to improve designs efficiency. The distributed memory blocks over the FPGA architecture, provide the necessary memory bandwidth for building parallel computing architectures.

Developing FPGA-based systems is a hard undertaking and a time consuming process. The designer requires firstly analyzing the problem under consideration, partition it into multiple tasks, each then implemented carefully to fulfill the performance requirements. The design then has to be implemented using a hardware description language like Verilog or VHDL before programming the FPGA device.

Even with FPGA-based computing being up to the expectations of the high performance community, the integration of FPGAs in heterogeneous systems composed of CPUs and GPUs is far from mainstream. The main obstacle in the way of FPGAs being used in heterogeneous platforms is the need for hardware expertise

Figure 1.2: FPGA fabric basic components.

to program the FPGA. The community of software programmers and especially programmers of parallel systems will resist a platform with its own programming language when the industry is moving towards unified higher-level programming models for multi-core and heterogeneous platforms. Using FPGAs in heterogeneous platforms ideally requires enabling FPGA programming using high level parallel programming languages like CUDA, and OpenCL.

## 1.2 Research Objective and Contribution

The problem of automatically generating system architectures from high level programming languages has been at the forefront of academic and industrial research in the last few decades. Generating system designs from high level programming languages such as C/C++ or Matlab has been investigated to increase design productivity and enable rapid design space exploration [13, 14, 15, 16, 17]. However, High Level Synthesis tools have not been so well adopted by the software engineer community because the design flow of the current commercial tools is more suited for the hardware rather than the software engineer. The designer is required to tune the application source code specifically for hardware design, and may have to intervene to specify low level details which may discourage most software engineers from using the technology. A successful high level synthesis tool targeting software engineers and parallel programmers will have to hide the architectural details from the programmer.

Using parallel programming models like OpenCL, to generate FPGA-based systems, open up system hardware design for the large community of software engineers to exploit the capabilities of high-end FPGA devices without the need for hardware expertise.

OpenCL programs express parallelism at its finest granularity. This is a particularly convenient feature for hardware generation, as the programmer explicitly exposes all available parallelism of the application. Exposing parallelism at its finest granularity allows hardware generation at different levels of granularity. Another favorable feature of OpenCL is the explicit expression of data movement in the form of buffer transfers between compute devices. Languages with C-like semantics, as well as traditional parallel programming models such as POSIX Threads or OpenMP,

express parallelism at a coarser granularity and at the same time ignore or obfuscate communication, thus placing the burden of re-discovering parallelism and communication patterns to an optimizing compiler and/or the user – usually with limited success.

Our research develops algorithms, and architectures to generate automatically hardware accelerators from OpenCL kernels. Our synthesis tool, Silicon OpenCL (SOpenCL), generates a hardware accelerator from a single OpenCL kernel using two phases: OpenCL to C source to source transformation and C to RTL generation. Our research concerns the second phase. A C function generated by the source to source transformation consists of one or more nested loops that encapsulate the computationally intensive parts of the OpenCL kernel.

The contributions [18, 19, 20] of our research can be summarized as follows:

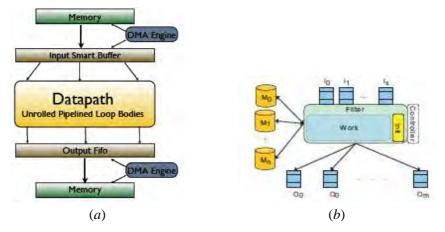

- 1. Code Transformations: The tool flow performs novel transformations specific for architectural synthesis. Bitwidth analysis transforms variable bitwidth from the standard size (char, int, etc.) into arbitrary sizes to minimize the amount of hardware resources. Predication replaces control dependencies with data dependencies, thus increasing the size of basic blocks and the potential of instruction schedulers to find an optimal instruction schedule. Code slicing decouples data movement from data computations, and overlaps their execution. A major transformation introduced in the tool flow is Code Clustering. SOpenCL analyzes patterns of instructions and produces application specific macroinstructions, where a macroinstruction consists of multiple basic arithmetic and logic operations. Macroinstructions provide a compact form of computation that can be implemented more efficiently than basic arithmetic and logic operations.

- 2. Architectural Template: SOpenCL utilizes an architectural template designed and configured to meet user performance requirements and fit the target device. The architecture of a hardware accelerator of an OpenCL kernel has a hierarchal structure which resembles the loop hierarchy in the generated C function. Each nested loop is allocated a single cluster of hardware which allows pipelining the nested loops execution. The architectural template

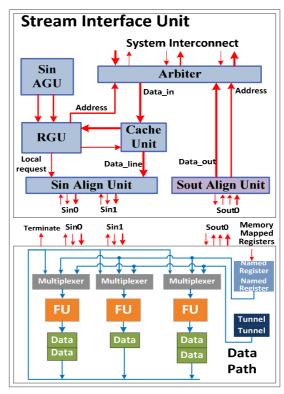

decouples and overlaps the execution of data computation and data movement by allocating separated modules for data computations (Datapath) and data movement to and from memories (Streaming Interface Unit).

3. Concurrent Execution Model: To exploit the separate hardware components in the architectural template, an asynchronous execution model is adopted. The operation of the streaming units and the computational datapaths is fully asynchronous, even across the boundaries of different loops and loop nests. Asynchronous execution model allows pipelined and parallel execution of multiple nested loops, and increases hardware utilization.

The current state of the tool produces a single accelerator per OpenCL kernel. The supported kernels may consist of arbitrary loop nests and shapes. They may contain synchronization and any kind of standard arithmetic operations. The tool flow also provides an IP library for floating point operators and math functions optimized to enhance the performance of the accelerator. OpenCL kernels that include dynamic memory allocation or function call are not supported.

#### 1.3 Thesis Structure

The structure of the thesis is as follows:

Chapter 2 covers the background material necessary to understand the proposed algorithms and design techniques. More precisely, Chapter 2 presents the framework and infrastructure used by our tool flow..

Chapter 3 introduces the proposed architectural template for architectural synthesis. It describes the skeleton of the template, its basic structure and how an OpenCL kernel is mapped on the template components. The chapter addresses the architectural techniques used in handling synchronization and exploiting data reuse to reduce memory access overhead. The execution model of OpenCL kernel on the generated hardware accelerator is also discussed.

Chapter 4 describes the low level transformations/optimizations and hardware generation methods applied on the OpenCL kernel source code to provide architectural optimizations. Transformations include bitwidth optimization, predication, code slicing and instruction clustering. Code slicing separates portions of

code responsible for addresses generation from computations to decouple and overlap their execution. Instruction clustering generates application specific instructions to build custom functional units. Later in the chapter we introduce methods used in taking architectural synthesis decisions. More precisely, scheduling instructions on allocated resources, data caching configurations, and synchronization/interconnect data channels generation. Two scheduling algorithms are described: *modulo scheduling* and *as soon as possible* scheduling.

Chapter 5 presents the experimental evaluation of the proposed techniques and architectural template. Finally, Chapter 6 completes this dissertation with the presentation of the conclusions and reference to future work.

## **CHAPTER 2**

# SILICON-OPENCL TOOL FLOW

#### 2.1 Tool Flow and Infrastructure

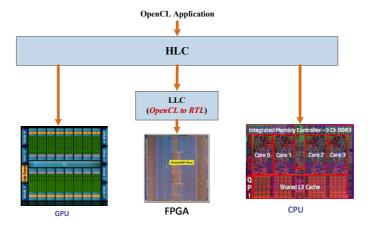

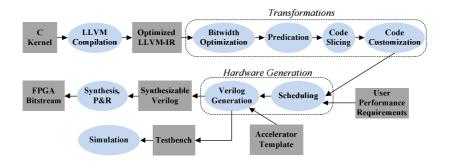

Silicon-OpenCL (SOpenCL) is an architectural synthesis CAD tool targeting heterogeneous parallel computing platforms (Figure 2.1). The objective is to allow a software programmer to develop an OpenCL application once, and deploy it on any platform, without the need for modifications. The tool consists of a two levels compilation process: High Level Compilation (HLC) and Low Level Compilation (LLC).

The high level compiler processes an OpenCL application and partitions its kernels as appropriate across the available computing platforms (CPU, GPU, and FPGA). The low level compiler processes OpenCL kernels selected to run on FPGA platforms. The task of the LLC is to compile an OpenCL kernel, and generate an equivalent hardware design that fits the target FPGA device and fulfills performance requirements. SOpenCL tool infrastructure also provides runtime environments for each of the target platforms to facilitate their integration and the execution of

Figure 2.1: Silicon-OpenCL Tool Flow.

#### OpenCL kernels.

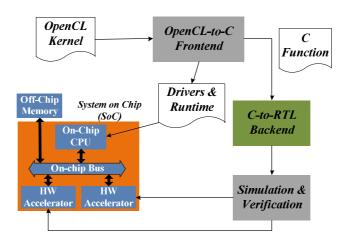

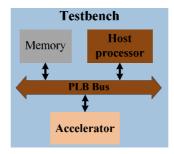

Figure 2.2 shows the low level compiler flow. The LLC converts unmodified OpenCL kernels into a system on chip (SoC) with hardware and software components. The tool flow generates a hardware accelerator for each OpenCL kernel in two phases: OpenCL-to-C transformation, and C-to-RTL. The tool flow also generates the runtime environment and drivers, in addition to the testbench generated for simulation and verification purposes. The OpenCL-to-C frontend developed by Daloukas [21] generates a C function from an OpenCL kernel by coarsening the computation granularity as will be detailed in section 2.3. The C-to-RTL backend developed in this thesis generates a hardware accelerator RTL description for each OpenCL kernel.

Figure 2.3 shows the C to RTL back end tool flow which-along with the front end is based on the LLVM compiler infrastructure. LLVM compiler translates the input C function into an assembly-like intermediate representation, called *LLVM-IR*. The LLVM compiler provides conventional optimizations and transformations such as dead code elimination, redundant code elimination, constants propagation, algebraic transformations, loop transformations, loop unroll, and loop invariant code motion. Given the LLVM-IR, the backend performs two sets of tasks, low level transformations and optimizations, and hardware allocation and generation.

Figure 2.2: SOpenCL Low Level Compiler (SOpenCL-LLC). (*C-to-RTL backend is the result of this thesis research*).

Figure 2.3: C-to-RTL backend.

### 2.2 OpenCL Programming Model

#### 2.2.1 Overview

OpenCL [22] is a programming framework for heterogeneous computing platforms. OpenCL was initially developed by Apple Inc. as a portable programming framework for the vast number of multi-core CPUs and GPUs. Apple submitted an initial proposal in collaboration with technical teams at AMD, IBM, Intel, and Nvidia, to the Khronos group. Within six months Khronos group released the first OpenCL specification for the public. OpenCL programming language is based on ISO C99 with some limitations and extensions. The language is extended to provide explicit representation of parallelism, synchronization and memory regions.

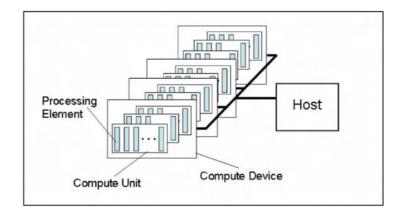

OpenCL programming framework was designed with software portability in mind. The vision is to write a single application that can run on a variety of potentially heterogeneous platforms, from embedded systems to workstations and supercomputers. The OpenCL platform model comprises a host processor and a number of compute devices (Figure 2.4). Each device consists of a number of compute units, which are subsequently divided into a number of processing elements. An OpenCL application consists of a host program and a number of kernel functions. The host part executes on the host processor and submits commands that can refer either to execution of a kernel function or to manipulation of memory objects. A kernel function contains the computational part of an application and is executed on the compute devices.

Figure 2.4: OpenCL Platform Model.

A key feature in OpenCL is that the compiler is built into the runtime system, which provides flexibility and portability, and allows OpenCL applications to select and use different compute devices in the system at runtime.

### 2.2.2 Computation Model

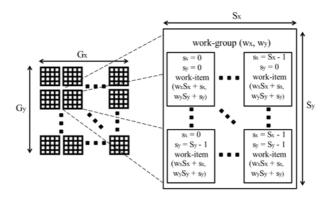

The work corresponding to a single invocation of an OpenCL kernel is called a work-item. Multiple work-items can be organized in a work-group. OpenCL allows for geometrical partitioning of the grid of computations to an N-dimensional space of work-groups, with each work-group being subsequently partitioned to an N-dimensional space of work-items, where  $1 \leq N \leq 3$  (Figure 2.5). Once a command that refers to execution of a kernel function is submitted, the host part of the application defines an abstract index space, with a maximum of 3 dimensions of work groups and 3 dimensions of work items in each work group. A work-item is identified

Figure 2.5: 2-dimensional computations grid geometry (N = 2).

by a tuple of IDs defining its position within the work group, as well as the position of the workgroup within the computation grid. Based on these IDs, a work-item is able to access different data (SIMD style) or follow a different path of execution.

Figure 2.6 shows an example of Chroma interpolation OpenCL kernel. Chroma interpolation computes sub-pixels from chrominance components in a video frame. Each work item (one kernel invocation) computes one sub-pixel by applying a 4-tap filter on 4 chrominance pixels. The filter output is then clipped to the value range [0,255]. The kernel utilizes 2-dimentional computations grid like the one shown in Figure 2.5. The  $get\_global\_id(0)$  and  $get\_global\_id(1)$  runtime functions return the unique global x- and y-coordinates of the work-item, respectively.

OpenCL also provides runtime functions to return local work-item coordinates within a work group (Figure 2.7). For example,  $get\_local\_id(0)$  and  $get\_local\_id(1)$  return the x- and y-coordinates (Sx and Sy in Figure 2.5) of the work-item within the work-group.

The programmer explicitly defines the dimensions of a single work group when she invokes the kernel function. The number of work groups is determined implicitly in the runtime depending on the size of the computation problem. For example, the chroma interpolation kernel of Figure 2.6 has 2-dimensional work group of size 4×4, i.e. 16 work-items, where each work-item processes a single pixel. The number of work groups depends on the grid size, i.e. the video frame size. For 640×480 VGA frame, the grid includes 80×60 work-groups.

Figure 2.6: Chroma Interpolation OpenCL kernel

Figure 2.7: Matrix Multiplication OpenCL kernel example.

### 2.2.3 Synchronization

OpenCL uses what is called a *relaxed memory consistency model* which means that different work-items may see a different view of global memory as the computation progresses. Synchronization is required to ensure data consistency within the work items of a work group, while reads and writes to all memory spaces are consistently ordered within work-items.

OpenCL programming model provides two types of synchronization functions among work-items inside a work-group, memory-fence and barrier function. A barrier function requires all work-items inside a work-group to rendevouz at the *barrier* call. In other words, every work-item in the same work group must execute the barrier function before any work-item is allowed to continue execution beyond the barrier command. A memory-fence only requires that loads and stores preceding the *mem\_fence* all be committed to memory. On the other hand, there is no synchronization mechanism among work-groups, which means that work-groups can be executed in parallel.

Figure 2.7, depicts an OpenCL kernel for naive matrix multiplication. Each workitem first prefetches an entry from each matrix and stores it in local memory. After the *barrier* function, each work item computes an entry in the output matrix. The *barrier* (CLK\_LOCAL\_MEM\_FENCE) function stalls the execution of every workitem in the work group before allowing any work-item to execute the last statements in the kernel. The barrier synchronization here is necessary to enforce memory dependencies between work-items in the same work group; loaded matrices entries by each work item are used by the rest of work items to perform their computations.

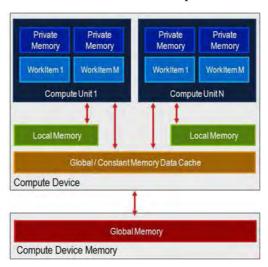

#### 2.2.4 OpenCL Memory Structure

OpenCL defines a memory hierarchy of four types: *global memory, constant memory, local memory,* and *private memory* (Figure 2.8). OpenCL standard only specifies the access level of different type of memory. Programmers can use memory region address qualifiers; **\_\_global, \_\_constant, \_\_local**, and **\_\_private** to specify the type of memory hosting data as in Figure 2.6 and Figure 2.7.

Global memory has the largest size on a compute device. Global memory is visible to all work-items in the computations grid. While the largest and visible to all work-items, global memory is considered the slowest memory. Constant memory is a read-only section of the global memory visible to all work-items. Constant memory can be associated with specialized hardware optimizations to broadcast data. Local memory is much faster than global memory, and is typically located on-chip. A local memory is a shared section of memory within the work-items of the same work-group. Synchronization of memory accesses in the local memory is the responsibility of the programmer. A private memory is used within a work-item, and implemented generally using registers in a GPU or CPU core. A private memory is fast and can be

Figure 2.8: OpenCL memory hierarchy.

used without the need for synchronization primitives. In situations where the compute device has inadequate number of registers, variables stored in private memory are spilled to global memory space causing significant performance drop.

### 2.3 OpenCL to C transformation

As explained in the previous section, OpenCL exposes parallelism at a fine level of granularity by allowing the programmer to embody the task executed by a single logical thread in an OpenCL kernel. For example, the OpenCL code for chroma interpolation (shown in Figure 2.6) describes the computation of a single loop iteration which comprises an OpenCL work-item in this case. Depending on performance requirements, and resource availability, any number of hardware accelerators can be generated spanning from a simple interpolator, executing a single thread per invocation, to an accelerator that produces the complete interpolated frame every time it is invoked. Between these two extremes, a hardware generation tool can generate any number of accelerators, each, potentially, being assigned a different amount of workload per invocation.

In order to enable efficient mapping of OpenCL kernel functions to the underlying platform while at the same time taking into account any hardware constraint, SOpenCL tool applies a series of source-to-source transformations in the high level compiler frontend (Figure 2.2) that collectively aim at coarsening the granularity of a kernel function from the work-item to the work-group level.

Daloukas [21] explains that the selection of a work-group as the preferred degree of granularity for logical threads serialization may seem arbitrary. However, taking synchronization within a work group into account, it will become evident that other options may present hard to overcome complications in the presence of synchronization operations or multiple exit points within the kernel. At the same time, work-group granularity is usually explicitly set by OpenCL programmers, often considering data reuse, or matching the work-group data footprint to the capacity of specific levels of the memory hierarchy. Therefore, introducing different degrees of work granularity at the runtime, despite being semantically correct, might introduce performance side-effects.

OpenCL-to-C frontend applies three source-to-source transformations: threads serialization, elimination of synchronization functions, and variable privatization, each one explained in the remainder of the chapter.

#### 2.3.1 Logical Threads Serialization

The main step in the OpenCL-to-C frontend is *logical thread serialization*. Workitems inside a work-group can be executed in any sequence, provided that no synchronization operation is present inside a kernel function. Based on this observation, execution of work-items is serialized by enclosing the instructions in the body of a kernel function into a *triple nested loop*, given that the maximum number of dimensions in the abstract index space within a workgroup is three. Each loop nest enumerates the work-items in the corresponding dimension, thus serializing their execution.

Threads serialization of kernel *Add\_3D* (Figure 2.9*a*) produces the C function in Figure 2.9b. Input argument *local\_size\_array* is an array of size 3, and is used to store the dimensions of the work group to be used as boundaries in the triple nested loop.

#### 2.3.2 Loop Fission

Thread serialization can lead to invalid execution of a kernel function if the OpenCL kernel body contains synchronization operations. In the presence of a barrier instruction, every work-item must execute that instruction before any work-item is

```

_kernel void Add_3D(__global int * A,

__global int * B,

__global int * C,

int * local_size_array,

_kernel void Add_3D(__global int * A,

int W, int H)

global int * B,

__global int * C,

triple nested loop

int i2, i1, i0;

for( i2 = 0; i2 < local size array[2]; i2++){

for( i1 = 0; i1 < local size array[1]; i1++){

int id0 = get_global_id(0);

for( i0 = 0; i0 < local size array[0]; i0++){

int id1 = get_global_id(1);

int id2 = get_global_id(2);

int pos = i2*W*H + i1*W + i0;

C[pos] = A[pos] + B[pos];

int pos = id2*W*H + id1*W + id0;

}

}

C[pos] = A[pos] + B[pos];

}

(a)

(b)

```

Figure 2.9: Logical Threads Serialization. (a) Add\_3D OpenCL kernel adds two 3D arrays. The three runtime functions return the coordinates (id0, id1, id2) of the pixel computed by a work-item. (b) C function after threads serialization.

allowed to continue its execution. However, in the modified C kernel function, every work-item finishes its execution before the next work-item is able to start. In order to ensure correct execution of the coarsened kernel function, the compiler applies *loop fission* transformation that facilitates logical thread serialization.

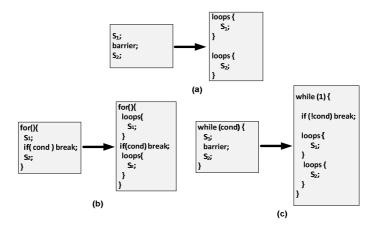

Loop fission is applied in order to enforce the execution ordering that is required by a synchronization instruction. A triple-nested loop enforces synchronization among work-items before its first and after its last iteration. Based on this observation, we partition the instructions of a kernel function into blocks such that no barrier instruction is present inside a block. Afterwards, we enclose each block into a triple-nested loop, Figure 2.10 depicts this transformation for the *MatrixMul* kernel of Figure 2.7. Since there is one synchronization statement, *barrier*, two triple nested loops are required to ensure correct execution of the C kernel function.

A similar problem occurs for kernel functions with multiple exit points, i.e. when *break, continue* or *return* statements are present. We treat each of the aforementioned instructions as an additional synchronization point and apply loop fission around it (Figure 2.11). For example, in Figure 2.11b, the *if*-statement works as a synchronization barrier. Hence, triple nested loops (*loops*) are created around each statement ( $S_1$  and  $S_2$ ).

#### 2.3.3 Variable Privatization

Loop fission presents a complication for variables that are defined in one triple-

Figure 2.10: Loop Fission example.

Figure 2.11: Barrier Elimination examples.

nested loop construct and used in another. A work-item that defines the value of a variable in the first loop cannot use it in a subsequent loop, as its contents will be polluted by the execution of subsequent work-items, thus violating semantics.

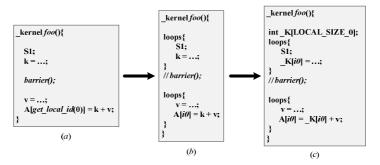

SOpenCL compilation infrastructure conducts a live-variable analysis to identify the variables that are live beyond the boundaries of the loops introduced by loop fission. Next, we apply variable privatization for these variables, namely we allocate them to a separate memory area for each logical thread. Each logical thread is therefore provided with a private copy of such variables.

Figure 2.12 shows an example of loop privatization. In Figure 2.12b, the variable k computed by each work-item (i.e. loop iteration) in the first nested loop, will be overwritten by other work-items (loop iterations). When the k variable is used in the second nested loop its value has been polluted with the last iteration of the first nested loop. Figure 2.12c shows the result of applying variable privatization on loop fission

Figure 2.12: Variable privatization example. (a) Original OpenCL kernel. (b) Loop fission output (wrong). (c) Variable privatization output (correct).

output. A local memory array ( $_K$ ) is allocated with size equal to the number of workitems per work group ( $LOCAL\_SIZE\_0$ ). Each work-item stores its k value in the allocated array at a unique position to be later used in the second nested loop.

For further details on the OpenCL compiler transformations, the interested reader should consult [21].

#### 2.3.4 Output C function structure

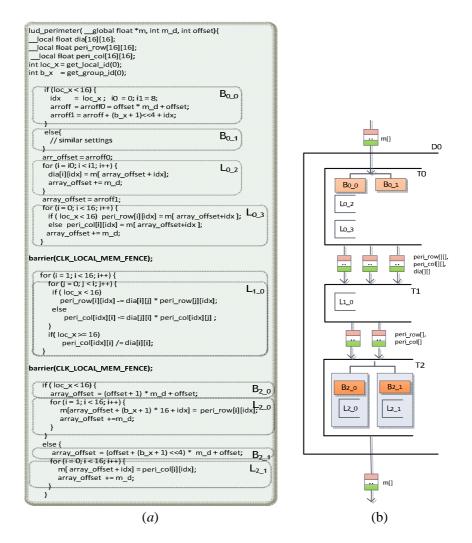

Figure 2.13*a* depicts an OpenCL kernel which implements LU Decomposition is used as a running example to explain the sequence of steps to generate the hardware accelerator. This kernel is part of the Rodinia benchmark suite [23].

LU Decomposition kernel consists of three parts, separated by barrier instructions. All work-items that execute the first part of the code, prefetch a segment of the input array m to three local buffers, and have to rendevouz to the first barrier before they proceed. The second part of the code performs the main LU Decomposition operation, and, likewise, forces all work-items to synchronize to the second barrier, before proceeding to the final writeback to array m.

Figure 2.13b depicts the block structure of the modified kernel function for our running example. The kernel code separated by barrier instructions is enclosed in triple nested loops  $(T_i)$ .

One may assume that transforming the parallel OpenCL representation into the sequential C representation, we lose the desirable features of OpenCL language, i.e. explicit parallelism and data movement. However, the specific structure of the generated C functions and the knowledge of what each portion of the function represents, we can ensure that the desirable features of OpenCL are preserved. Multiple nested loops in the C function indicate the existence of synchronization commands within the OpenCL kernel. Multiple nested loops have to be executed sequentially, but their execution can be pipelined.

The body of a triple nested loop represents the workload of a single work-item, which leads to the conclusion that multiple iterations of a triple nested loop can correspond to multiple work-items, and hence, can be executed in parallel and out of order.

Figure 2.13: OpenCL kernel for LU Decomposition with marked loops  $(L_{i,j})$  and basic blocks out of loops  $(B_{i,j})$ . In this kernel, a work-item (or thread) performs LU Decomposition for a 32x32 sub-matrix. Some parts of the code have been omitted for brevity.

Explicit local memory representations are transformed into local data arrays in the C function, and can be implemented as on-chip distributed memory blocks.

### 2.4 LLVM Compiler Infrastructure

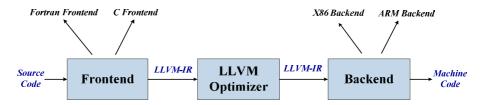

LLVM compiler infrastructure [24] has been developed to provide a machine independent framework for program optimization, analysis, and refactoring. To provide support for multiple programming languages and different target architectures, LLVM adapts a three-step compilation flow (Figure 2.14). The LLVM

Figure 2.14: LLVM compiler Infrastructure

compiler model provides a RISC-style, yet rich, intermediate representation (LLVM-IR) between the frontend, optimizer, and backend.

The clarity and completeness of the LLVM-IR, provides a simple way for conveying information between multiple analysis and transformation passes as well between the frontend and backend. Using LLVM-IR, the compiler framework is a collection of libraries of transformations and optimizations can be used to build a compiler for any language and target architecture. In particular, LLVM-IR is both well specified and the *only* interface to the optimizer. This property means that all you need to know to write a frontend for LLVM is what LLVM-IR is, how it works, and the invariants it expects.

#### 2.4.1 LLVM Intermediate Representation (LLVM-IR)

The LLVM-IR instruction set captures the key operations of ordinary processors but avoids machine-specific constraints such as physical registers, pipeline architecture, and low-level calling conventions. LLVM-IR provides an infinite set of typed virtual registers which can hold values of primitive types (boolean integer, floating point, and pointer). The virtual registers are in Static Single Assignment (SSA) form [58]. LLVM-IR is a load/store architecture: programs transfer values between registers and memory solely via load and store operations using typed pointers.

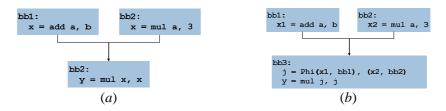

LLVM-IR uses SSA as its primary code representation (Figure 2.15). SSA is an Intermediate Representation (IR) used in several compilers (including LLVM compiler). In SSA each instruction is assigned a unique register name and each use of a register is dominated by its definition. In the example of Figure 4.4, the two assignments for the register x is transferred into two assignments on two different registers.

Figure 2.15: SSA Representation (a) Code portion without SSA representation. (b) Code with SSA representation.

A key feature of SSA IR is the Phi instruction which selects the proper value to pass to the next blocks, depending on the last control transfer event. In the example given, the assignment to register y does not read the values of the assignments for xI and x2 directly but, instead, the proper value is passed through the Phi instruction assignment.

Memory locations in LLVM-IR are not in SSA form because many possible locations may be modified at a single store through a pointer, making it difficult to construct a reasonably compact, explicit SSA code representation for such locations.

SSA form provides a compact *def-use* graph that simplifies many dataflow optimizations and enables fast, flow-insensitive algorithms to achieve many of the benefits of flow-sensitive algorithms without expensive dataflow analysis. Non-loop transformations in SSA form are further simplified because they do not encounter anti- or output dependences on SSA registers. Non-memory transformations are also greatly simplified because registers cannot have aliases.

Figure 2.16 shows an example of LLVM-IR generated for a C function that clips a value in the range [0, 255]. A function in LLVM-IR consists of one or more basic

```

define i8 @ClipValue(i16 %a) {

entry:

16-bit integer data type

%tmp1 = cmp lt i16 %a, 0;

br il %tmpl, label %exit, label %else

char ClipValue(short a) {

else:

char b = a;

%tmp2 = cmp gt i16 %a, 255;

br i1 %tmp1, label %exit, label %else2

if (a < 0) b = 0;

else if (a > 255) b = 255;

Instructions Basic Block

else2:

br label %exit

return b;

%tmp3 = phi [0, entry], [255, else], [%a, else2];

Input C program

ret i8 %tmp3

Output LLVM-IR

```

Figure 2.16: LLVM-IR Example.

blocks of instructions. A program in LLVM is represented as a module of code that includes one or more functions. A feature in LLVM-IR is its arbitrary bitwidth data type representation, which is convenient for hardware bitwidth optimizations.

#### 2.5 Related Work

There is a large body of literature that deals with conversion of an application written in a high level language to hardware. The majority of research efforts used a variation of C as their input programming language which was driven mainly by the existence of a large body of C programmers, and the extensive use of C in embedded applications. C-based architectural synthesis research can be classified into two categories: using a restricted format of C written in specific way, or extending extra language constructs and syntax to support hardware synthesis.

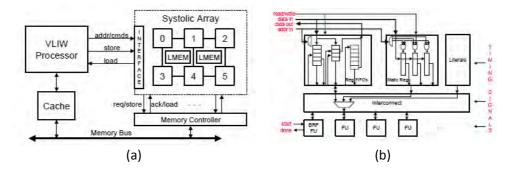

PICO-NPA [13], SPARK [25], Trident [26], and Streamroller [27] belong to first category. PICO-NPA is a synthesis system that generates non-programmable accelerators from a C function. PICO restricts a C function to consist only of a single perfectly nested loop. In addition to nested loops, PICO make use of C pragmas to pass application specific information to simplify program analysis. Those pragmas allow the user to declare no-standard data widths, to indicate that specific global variables are not live-in or not live-out. Also pragmas could be used to advise the compiler to create local memory for certain arrays, like lookup tables. PICO does not support recursion, and dynamic memory allocation.

SPARK and Trident impose no stylizations or modeling on the input C functions. The only restrictions in SPARK C model include function recursion and dynamic memory allocation. Trident imposes additional restrictions: the code cannot contain print statements, function arguments or returned values, calls to functions with variable-length argument lists, or arrays without a declared size.

Streamroller emulates the stream programming model by some extensions of the C language to capture parallelism and decouple communication from computation. The system takes as input the application written in C, expressed as a set of communicating kernels. The input program consists of two logical parts, a set of kernel specifications and system specification. A kernel is expressed as a single C

function. All inputs and outputs to the kernel have to be provided as arguments to the function. The body of the kernel has to be perfectly nested for loops. The system specification describes one "packet" forward flow through the pipeline. The system specification is expressed as a C function whose body contains a sequence of calls to the kernel functions.

The second category of C-based hardware synthesis research includes work that created new programming languages as variations of ANSI-C, such as Handel-C [28], Mitrion-C [29], haydn-C [30], and SA-C [31, 32] Handel-C retains most of the pure C syntax and sequential execution model. However, to support compilation for hardware, Handel-C supports several hardware implementation features like arbitrary bitwidth declarations of variables. Parallelism in Handel-C is supported through a "para" qualifier to declare a block of statements that will run in parallel. Handel-C provides a channel declaration to communicate between parallel blocks. RAMs and ROMs are declared in Handel-C like arrays, with exception that RAMs and ROMs are accessed once each clock cycle.

Haydn-C has many similarities to Handel-C. Like Handel-C, it uses parallel blocks of statements, VHDL-like components/entities to describe parallelism in the program. The Handel-C and Haydn-C are timed languages, i.e. require from the programmer to keep exact timing of the program execution, by defining the time execution of each expression as one clock cycle, and providing the user with a "delay" construct to control the timing of execution.

Mitrion-C main concept centers on parallelism and data dependencies and there is no order-of-execution; any operation may be executed as soon as its data-dependencies are fulfilled. To capture the custom features of hardware implementation, Mitrion-C enables the user to specify the exact variable precision by declaring the bit-width of the variable. Like other static single assignment languages, each statement in Mitrion-C is an expression, statements like FOR, WHILE loops return values, and each variable within a scope is assigned once. The single-assignment is required in Mitrion-C since statements within scope could run in parallel rather than sequential. In addition, since Mitrion-C targets FPGAs, it supports the use of RAM blocks and banks through a group of memory read/write functions.

SA-C differs from C in some important ways. It is an *expression-oriented*, functional language. Its scalar types include signed and unsigned integers and fixed point numbers with specified bit widths. It has no explicit pointers, and is non-recursive. It has true multidimensional arrays, including array sections similar to those in Fortran 90. It also allows any function, loop or conditional expression to return multiple values.

Other prior research based on C programming model chose to provide libraries of functions and types to support hardware synthesis instead of creating a new language. Stream-C [33] is a combination of annotations and library functions callable from C program. There are three distinguished objects declared in Stream-C program: process, stream and signal. Stream and signal carry data and control bits between processes. Processes are the computation kernels that implemented by hardware or host processor. Process declaration consists of head where the name and IN/OUT streams/signals are declared, and body encloses the computational operations. The body is written using callable functions and a subset of supported C.

Impulse CoDeveloper is an ANSI C synthesizer [34] based on the Impulse C language. Impulse C is distinct from standard C in that it provides a parallel streaming programming model for mixed processor and FPGA platforms. For this purpose, Impulse C includes extensions to C, in the form of functions and datatypes, allowing applications written in standard C to be mapped onto coarse-grained parallel architectures that may include standard processors along with programmable FPGA hardware. Using Impulse C, an application could be described as a collection of parallel, pipelined processes, each of which has been described using one or more C subroutines.

At the heart of the ImpulseC streaming programming model are processes and streams. Processes are independently synchronized, concurrently executing segments of an application. Hardware processes are written using a subset of standard C and perform the work of an application by accepting data, performing computations and generating outputs. In a typical application, data flows from process to process by means of buffered streams, or in some cases by means of messages and/or shared memories. The characteristics of each stream, including the width and depth of the generated FIFOs, may be specified in the C application.

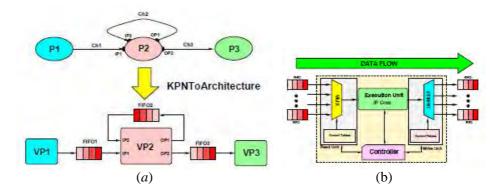

Another category of research efforts used the stream-programming model as their high level languages. In Proteus [35], a program consists of two objects: streams descriptors and stream data-flow graph (sDFG). A stream descriptor declares stream access patterns from main memory. The sDFG describes a computational kernel, and declares IN/OUT streams. Using those two objects a program can be written as a set of communicating sDFG blocks through streaming channels.

Optimus [36] takes programs written in StreamIt stream programming language. Programs in StreamIt are represented as graphs where nodes, called *filters* encapsulate computation, and edges represent FIFO communication. StreamIt is based on the synchronous dataflow (SDF) model of computation [50]. Each filter consists of a *work* function that repeatedly executes when sufficient data is available on its input FIFO (queue). The work function reads data from its input queue using *pop* operations, and writes data to its output queue using *push* operations. The work function can also inspect input without removing them from the FIFO using a *peek* operation.

Prior research has investigated the use of different programming models like MATLAB and Simulink. MATLAB and especially Simulink have traditionally been used for algorithm design. The availability of a mature tool with specialized modules (toolboxes, blocksets) along with the possibility of integrating C code makes the tool a very attractive development platform. Work in [16] presents a MATLAB-to- RTL compilation flow. One of the issues to be resolved in generating hardware from MATLAB is to figure out the type/shape of the variables since MATLAB variables have no notion of type or shape. To generate hardware, the compiler must determine the exact data type i.e. integer or floating point, or complex numbers etc. The compiler also needs to determine the shape i.e. how many dimensions the matrix (array) has, and what are the extents in each dimension.

The majority of current high level synthesis commercial tools use SystemC as input representation [14, 37, 38]. SystemC is a set of C++ classes and macros used to simulate concurrent processes, each described using plain C++ syntax. SystemC is closer to HDL languages VHDL and Verilog. A program in SystemC usually consists of several modules which communicate via ports. SystemC Modules include concurrent processes as the main computation elements. Modules communicate via

channels, which could be either wires or complex communication mechanisms like FIFOs or bus channels. SystemC libraries provide datatypes extensions like arbitrary bitwidth integer datatypes, and fixed point datatypes, in addition to C++ standard types.

Lately, research in architectural synthesis have focused on parallel programming languages such as FCUDA, a tool that converts CUDA kernels to synthesizable hardware [39]. CUDA is a parallel programming model developed by Nvidia for graphics processing. A CUDA kernel implicitly describes multiple CUDA threads that are organized in groups called thread-blocks. Thread-blocks are further organized into a *grid* structure similar to that of OpenCL. FCUDA is based on source-to-source transformation that generates a C function for each CUDA kernel. The generated C code is annotated with pre-processor directives (FCUDA pragmas) inserted by the FPGA programmer into the CUDA kernel. These directives control the FCUDA translation of the expressed parallelism in CUDA code into explicitly-expressed coarse-grained parallelism in the generated AutoPilot code. The FCUDA pragmas describe various FPGA implementation dimensions which include the number, type and granularity of tasks, the type of task synchronization and scheduling, and the data storage within on and off-chip memories.

The AutoPilot Compiler [15] generates RTL descriptions for each function in a C program. Each function is translated into an FPGA core. AutoPilot provides code directives to indicate parallel-code regions, and further unrolls inner-loops to run concurrently when no across iterations dependencies are detected. AutoPilot allocates all arrays onto local BRAMs. It also supports arbitrary bitwidth data types to achieve optimized hardware implementations.

Jääskeläinen et al. [40] introduce a compilation infrastructure based on LLVM to generate transport-triggered architectures from OpenCL codes in an approach seemingly similar to our work. The processors generated with their design flow are statically scheduled VLIW-style architectures with up to hundreds of programmer visible general-purpose registers. Parallelism at the granularity of work-items is exploited in order to overlap memory access latency with computations. They also introduce and use OpenCL extensions in order to code performance-critical parts of the kernels. Our approach is inherently different. We do not favor OpenCL

extensions, but perform extensive compile-time analysis instead, and granularity coarsening in order to avoid putting additional burden to the programmers.

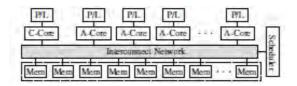

Altera Inc. started an initiative to build FPGA-based systems from OpenCL programs [41]. The concept of Altera's OpenCL-to-FPGA is similar to that of Jääskeläinen et al.; OpenCL threads are mapped on customized processing cores. The system is populated with many of the processing cores on which the entire computations grid is mapped. An embedded on-chip RISC processor (e.g. Nios) plays the role of host processor that manages OpenCL threads. The processing cores are either custom pipelines or a VLIW/Vector processor.

Finally, OpenRCL platform utilizes OpenCL to schedule fine-grain parallel threads to a large number of MIPS-like cores [42]. OpenRCL does not generate customized hardware accelerators, although each MIPS core can be configured to match application characteristics.

# CHAPTER 3

# ARCHITECTURAL TEMPLATE

## 3.1 Overview

In a conventional hardware design flow, application functionality and structure determine the target design architecture. A hardware designer performs firstly a thorough analysis of the application functionality to extract parallelism and data communication patterns. Based on the analysis output, the designer partitions the application into a hierarchal structure of parallel tasks and subtasks each implemented separately, and determines the communication network connecting the set of tasks. Hardware designers exploit all kinds of available parallelism in the application like instruction parallelism, data parallelism, pipeline parallelism, and task level parallelism. Moreover, each task implementation is optimized according to its specific computational patterns.

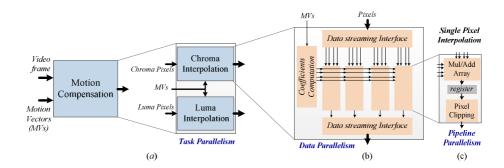

Figure 3.1 depicts the block diagram of a manual implementation of the motion compensation block in AVS video codec system [43]. A hardware designer typically partitions a complex task into multiple subtasks each performing a specific function: *chroma interpolation*, and *luma interpolation* (Figure 3.1a). Such partitioning exploits task level parallelism by concurrently executing chroma and luma interpolation, and pipeline parallelism by overlapping the execution of multiple blocks of data (called macroblocks in the context of video codecs). The designer may go further by partitioning each subtask into smaller blocks each performing a specific functionality exploiting more task parallelism, pipeline parallelism and data parallelism (Figure 3.1b). At the low level partitions, a hardware designer will exploit computation patterns to build efficient circuits to perform the basic computations (Figure 3.1c). Hardware designers traditionally design separated components for data streaming and interfacing to overlap I/O data communication and computations.

Figure 3.1: Motion Compensation Block Manual design.

In this work, the SOpenCL backend transforms a C function, corresponding to an OpenCL kernel, to synthesizable HDL based on an architectural template that can be instantiated to match the performance requirements of the application and the available FPGA resources. In the following sections we will describe the structure and components of the architectural template, and how the C function is mapped onto it.

# 3.2 High Level Architecture

### 3.2.1 Hierarchical Structure

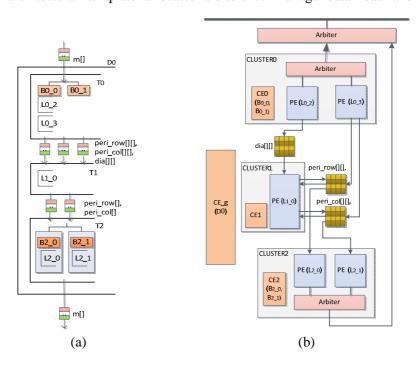

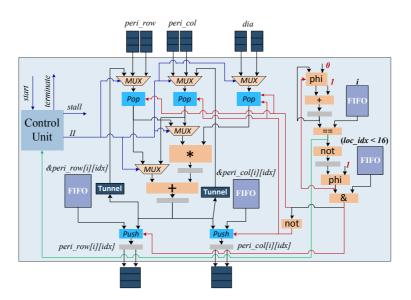

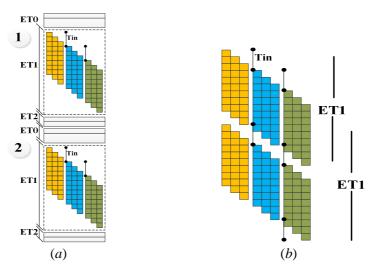

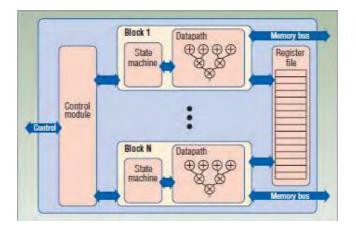

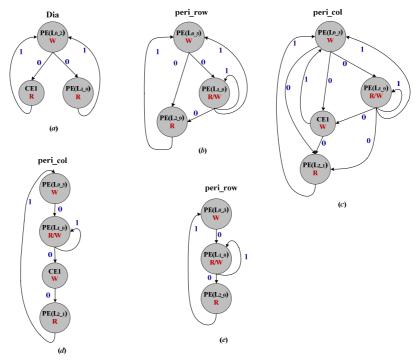

The use of an architectural template is necessary to relieve the programmer from specifying the tasks partitions and mapping by providing a systematic approach in partitioning and mapping the kernel code onto the hardware fabric while exploiting available parallelism. The proposed architectural template has a hierarchal structure that closely follows the computational hierarchy of the input kernel. Figure 3.2b shows the architecture of the hardware accelerator of the LU Decomposition kernel shown in Figure 3.2a. The architectural template is built mainly of two types of components: Processing Element (PE) and Control Element (CE). A PE is a customized architecture that executes an inner-most loop. A CE implements the functionality of the outer loops and loop invariant statements. Based on this classification, the kernel in Figure 3.2a translates into the accelerator of Figure 3.2b as follows:

• *Inner Loops*: Each of the inner loops  $\{L_{0_{-2}}, L_{0_{-3}}, L_{1_{-0}}, L_{2_{-0}}, \text{ and } L_{2_{-1}}\}$  is allocated a PE module.

- Nested Loops: Each of the nested loops {T0, T1, and T2} is allocated a CE module {CE0, CE1, and CE2}. Moreover, CE modules CE0 and CE2 are also used for processing outer loop basic blocks {B<sub>0\_0</sub>, B<sub>0\_1</sub>} and {B<sub>2\_0</sub>, B<sub>2\_1</sub>}, respectively.

- *Loop Invariant Code*: Loop invariant code outside any nested loops in the kernel body is allocated a CE module {*CE\_g*}.

In this hierarchal structure a *parent-child* relationship exists between a CE module and another CE or PE module. In addition to executing outer loops and loop invariant code, a parent CE initiates the execution of its children. For instance, module CE0 is responsible for controlling execution of PE modules  $PE(L_{0,2})$  and  $PE(L_{0,3})$ .

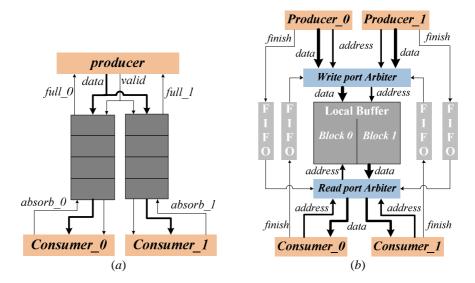

Local arrays in the kernel (*peri\_row*, *peri\_col*, and *dia* in Figure 3.2a) are each allocated a local memory implemented using dual port Block RAMs (BRAMs). Local memories could be either double buffered or work as a FIFO to enable pipeline parallelism of multiple PE and CE modules.

The architectural template allocates arbiters to manage data read and write

Figure 3.2: (a) Program structure of LU Decomposition kernel after coarsening the granularity to the equivalent of a work-group. (b) The block diagram of the automatically generated hardware accelerator for LU decomposition.

requests to global memories. Each separate memory port has its own arbitration logic. Multiple PE and CE modules that access the same global memory will compete to gain access to a global memory port.

The resemblance between the source code structure and the generated architecture provides several benefits:

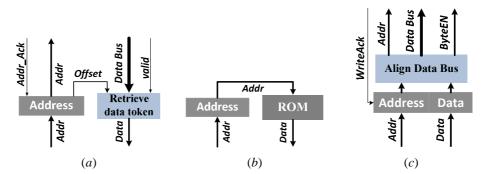

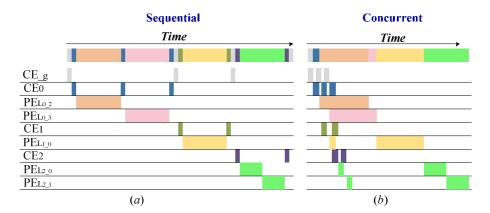

- Exploiting multi-level parallelism: Multiple nested loops can be pipelined and hence execute in parallel. Multiple PE modules are allowed executing in parallel if they are independent or can be pipelined if they have cross iteration dependencies.