# Design and Fabrication of an AMBA (ARM AHB-Lite Slave) Circuit Using CAD Tools at 350nm Technology

A thesis presented for the Faculty of the Department of Electrical and Computer Engineering in Partial Fulfillment of the Requirements for the Diploma of Science

Author:

Konstadinos Mourtziapis

Supervisors:

Dr. John Moondanos

Dr. Christos Sotiriou

Department of Electrical and Computer Engineering UNIVERSITY OF THESSALY Volos, Greece July, 2015

#### UNIVERSITY OF THESSALY

#### Department of Electrical and Computer Engineering

## Design and Fabrication of AMBA (ARM AHB-Lite Slave) Circuit Using CAD Tools at 350nm Technology

$\begin{array}{c} by\\ Mourtziap is\ Konstadinos \end{array}$

Graduate Thesis

for

the degree of

Diploma of Science in Computer and Communication Engineering

Approved by the two member inquiry committee at 10<sup>th</sup> of July 2015

Dr. Christos Sotiriou

Dr. John Moondanos

### Declaration of Authorship

I, Mourtziapis Konstadinos, declare that this thesis titled, 'Design and fabrication of AMBA (ARM AHB-lite slave) circuit using CAD tools at 350nm technology' and the work presented in it are my own. The research was carried out wholly or mainly while in candidature for the graduate degree of Diploma of Science in Computer and Communication Engineering, at the University of Thessaly, Department of Electrical and Computer Engineering, Volos, Greece. No part of this thesis has been previously submitted for a degree or any other qualification at this University or any other institution. Wherever I have consulted or quoted from the work of others, it is always attributed and the source is given. The main sources of help are referenced in the Bibliography section of this thesis.

.....

Mourtziapis Konstadinos

© Copyright by Mourtziapis Konstadinos 2015 All rights reserved

### Acknowledgements

I would like to express my wholehearted gratitude to my supervisor, Dr.John Moondanos, who trusted me in dealing with this thesis. He did not lose hope in me even in the midst of many hardships. His patience, expertise and advising, contributed to my graduate experience and finally this thesis completion. I strongly appreciate his in depth knowledge and skills. The development of this project would not have been possible without his assistance.

Furthermore, I would like to thank my co-advisor Dr. Christos Sotiriou for his assistance and support he provided at all levels of this thesis.

Moreover, i would like to thank Ioanna for her moral and technical support that she gave me in order to complete my thesis.

Finally, I have to thank my family for their endless and invaluable moral support that offered me all those academic years.

Mourtziapis Konstadinos Volos, 2015

### Contents

| Declaration of Authorship  Dedications  Acknowledgements  Contents  List of Tables  List of Figures  List of Listings  Abbreviations  Abstract  1 Introduction 1.1 Motivation 1.2 Thesis Goals 1.3 Thesis Sructure  2.1 Brief ICs History 2.2 VLSI Design Flow 2.1 Brief ICs History 2.2 VLSI Design Flow 2.2.1 Design Specification 2.2.2 RTL Description 2.2.3 Front End Flow 2.2.3.1 RTL simulation 2.2.3.2 Synthesis 2.2.3.3 Post-synthesis verification 2.2.3.4 Static Timing Analysis 2.2.4 Back End Flow 2.2.4.1 Layout generation 2.2.4.2 Physical Verification 2.2.3. Design for Test |    |                                         |                                                                            |                                                                                         |                              |                                                    |                                                |                                       |               |                                 |                                    |          |    |      |  |      |      |              |      |  |      | Pa | ıge                                            |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|-----------------------------------------|----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|------------------------------|----------------------------------------------------|------------------------------------------------|---------------------------------------|---------------|---------------------------------|------------------------------------|----------|----|------|--|------|------|--------------|------|--|------|----|------------------------------------------------|

| Acknowledgements  Contents  List of Tables  List of Figures  List of Listings  Abbreviations  Abstract  1 Introduction 1.1 Motivation 1.2 Thesis Goals 1.3 Thesis Sructure  2 Literature Review 2.1 Brief ICs History 2.2 VLSI Design Flow 2.2.1 Design Specification 2.2.2 RTL Description 2.2.3 Front End Flow 2.2.3 Front End Flow 2.2.3.1 RTL simulation 2.2.3.2 Synthesis 2.2.3.3 Post-synthesis verification 2.2.3.4 Static Timing Analysis 2.2.4 Back End Flow 2.2.4.1 Layout generation 2.2.4.2 Physical Verification 2.3.3 Design for Test                                            | D  | eclara                                  | ation o                                                                    | of Autho                                                                                | orsl                         | hip                                                |                                                |                                       |               |                                 |                                    |          |    |      |  |      |      |              |      |  |      |    | i                                              |

| Contents  List of Tables  List of Figures  List of Listings  Abbreviations  Abstract  1 Introduction 1.1 Motivation 1.2 Thesis Goals 1.3 Thesis Sructure  2 Literature Review 2.1 Brief ICs History 2.2 VLSI Design Flow 2.2.1 Design Flow 2.2.1 Design Specification 2.2.2 RTL Description 2.2.3 Front End Flow 2.2.3 Front End Flow 2.2.3.1 RTL simulation 2.2.3.2 Synthesis 2.2.3.3 Post-synthesis verification 2.2.3.4 Static Timing Analysis 2.2.4 Back End Flow 2.2.4.1 Layout generation 2.2.4.2 Physical Verification 2.2.4.2 Physical Verification                                    | D  | edica                                   | tions                                                                      |                                                                                         |                              |                                                    |                                                |                                       |               |                                 |                                    |          |    |      |  |      |      |              |      |  |      |    | ii                                             |

| List of Tables  List of Figures  List of Listings  Abbreviations  Abstract  1 Introduction 1.1 Motivation 1.2 Thesis Goals 1.3 Thesis Sructure  2 Literature Review 2.1 Brief ICs History 2.2 VLSI Design Flow 2.2.1 Design Specification 2.2.2 RTL Description 2.2.3 Front End Flow 2.2.3.1 RTL simulation 2.2.3.2 Synthesis 2.2.3.3 Post-synthesis verification 2.2.3.4 Static Timing Analysis 2.2.4 Back End Flow 2.2.4.1 Layout generation 2.2.4.2 Physical Verification 2.2.4.2 Physical Verification 2.3 Design for Test                                                                 | A  | cknov                                   | wledge                                                                     | ments                                                                                   |                              |                                                    |                                                |                                       |               |                                 |                                    |          |    |      |  |      |      |              |      |  |      |    | iii                                            |

| List of Listings  Abbreviations  Abstract  1 Introduction 1.1 Motivation 1.2 Thesis Goals 1.3 Thesis Sructure  2 Literature Review 2.1 Brief ICs History 2.2 VLSI Design Flow 2.2.1 Design Specification 2.2.2 RTL Description 2.2.2 RTL Description 2.2.3 Front End Flow 2.2.3.1 RTL simulation 2.2.3.2 Synthesis 2.2.3.3 Post-synthesis verification 2.2.3.4 Static Timing Analysis 2.2.4 Back End Flow 2.2.4.1 Layout generation 2.2.4.2 Physical Verification 2.3 Design for Test                                                                                                          | Co | onten                                   | $_{ m nts}$                                                                |                                                                                         |                              |                                                    |                                                |                                       |               |                                 |                                    |          |    |      |  |      |      |              |      |  |      |    | iv                                             |

| List of Listings  Abbreviations  Abstract  1 Introduction 1.1 Motivation 1.2 Thesis Goals 1.3 Thesis Sructure  2 Literature Review 2.1 Brief ICs History 2.2 VLSI Design Flow 2.2.1 Design Specification 2.2.1 Design Specification 2.2.2 RTL Description 2.2.2 RTL Description 2.2.3 Front End Flow 2.2.3.1 RTL simulation 2.2.3.2 Synthesis 2.2.3.3 Post-synthesis verification 2.2.3.4 Static Timing Analysis 2.2.4 Back End Flow 2.2.4.1 Layout generation 2.2.4.2 Physical Verification 2.2.4.2 Physical Verification                                                                     | Li | st of                                   | Tables                                                                     | 5                                                                                       |                              |                                                    |                                                |                                       |               |                                 |                                    |          |    |      |  |      |      |              |      |  |      |    | vii                                            |

| Abstract  1 Introduction 1.1 Motivation 1.2 Thesis Goals 1.3 Thesis Sructure  2 Literature Review 2.1 Brief ICs History 2.2 VLSI Design Flow 2.2.1 Design Specification 2.2.2 RTL Description 2.2.3 Front End Flow 2.2.3 Front End Flow 2.2.3.1 RTL simulation 2.2.3.2 Synthesis 2.2.3.3 Post-synthesis verification 2.2.3.4 Static Timing Analysis 2.2.4 Back End Flow 2.2.4.1 Layout generation 2.2.4.2 Physical Verification 2.3 Design for Test                                                                                                                                            | Li | st of                                   | Figure                                                                     | es                                                                                      |                              |                                                    |                                                |                                       |               |                                 |                                    |          |    |      |  |      |      |              |      |  |      | •  | viii                                           |

| Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Li | st of                                   | Listin                                                                     | $\mathbf{g}\mathbf{s}$                                                                  |                              |                                                    |                                                |                                       |               |                                 |                                    |          |    |      |  |      |      |              |      |  |      |    | x                                              |

| 1 Introduction 1.1 Motivation 1.2 Thesis Goals 1.3 Thesis Sructure  2 Literature Review 2.1 Brief ICs History 2.2 VLSI Design Flow 2.2.1 Design Specification 2.2.2 RTL Description 2.2.3 Front End Flow 2.2.3.1 RTL simulation 2.2.3.2 Synthesis 2.2.3.3 Post-synthesis verification 2.2.3.4 Static Timing Analysis 2.2.4 Back End Flow 2.2.4.1 Layout generation 2.2.4.2 Physical Verification 2.3 Design for Test                                                                                                                                                                           | A۱ | bbrev                                   | viation                                                                    | S                                                                                       |                              |                                                    |                                                |                                       |               |                                 |                                    |          |    |      |  |      |      |              |      |  |      |    | xi                                             |

| 1.1 Motivation 1.2 Thesis Goals 1.3 Thesis Sructure  2 Literature Review 2.1 Brief ICs History 2.2 VLSI Design Flow 2.2.1 Design Specification 2.2.2 RTL Description 2.2.3 Front End Flow 2.2.3.1 RTL simulation 2.2.3.2 Synthesis 2.2.3.3 Post-synthesis verification 2.2.3.4 Static Timing Analysis 2.2.4 Back End Flow 2.2.4.1 Layout generation 2.2.4.2 Physical Verification 2.3 Design for Test                                                                                                                                                                                          | Αl | ostra                                   | ct                                                                         |                                                                                         |                              |                                                    |                                                |                                       |               |                                 |                                    |          |    |      |  |      |      |              |      |  |      | 2  | kiii                                           |

| 2.2.3.3       Post-synthesis verification         2.2.3.4       Static Timing Analysis         2.2.4       Back End Flow         2.2.4.1       Layout generation         2.2.4.2       Physical Verification         2.3       Design for Test                                                                                                                                                                                                                                                                                                                                                 |    | 1.1<br>1.2<br>1.3<br><b>Lite</b><br>2.1 | Motiva<br>Thesis<br>Thesis<br>erature<br>Brief I<br>VLSI<br>2.2.1<br>2.2.2 | Action Goals Sructure  Review Cs Histor Design Fl Design S RTL Design Eront En          | y ry low Spe escr nd         |                                                    | · · · · · · · · · · · · · · · · · · ·          | · · · · · · · · · · · · · · · · · · · |               |                                 |                                    |          |    | <br> |  | <br> | <br> | <br>         | <br> |  | <br> |    | 1<br>3<br>3<br>3<br>4<br>5<br>6<br>6<br>7<br>7 |

| 2.3.1 Scan Chain insertion - Multiplexed Flip-Flop Style                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |                                         | Desigr<br>2.3.1                                                            | 2.2.3.2<br>2.2.3.3<br>2.2.3.4<br>Back En<br>2.2.4.1<br>2.2.4.2<br>a for Test<br>Scan Ch | Sy<br>Pond I<br>La<br>Ponair | ynth<br>fost-<br>tatio<br>Flow<br>ayou<br>hysi<br> | nesis<br>synt<br>c Tir<br>v .<br>ut go<br>ical | thes<br>min<br><br>ener<br>Ver        | is vag A rati | vering<br>Ana<br><br>on<br>atio | fica<br>lysi<br>· ·<br>· ·<br>on · | tio<br>s | on | <br> |  | <br> | <br> | <br><br><br> | <br> |  | <br> |    | 7<br>7<br>8<br>8<br>8<br>9<br>9<br>10          |

#### CONTENTS

|   | 2.5             | 2.4.1 AMS 350nm Standard Cell Library       1         EDA Tools       1 | 2  |

|---|-----------------|-------------------------------------------------------------------------|----|

|   |                 | 2.5.1 Deal With Problems                                                | 3  |

| 3 | $\mathbf{AR}$ I | M AMBA AHB                                                              | 4  |

|   | 3.1             | General on ARM AMBA                                                     | 5  |

|   |                 | 3.1.1 Design Principles                                                 | 5  |

|   |                 | 3.1.2 AMBA Protocol Specifications                                      | 5  |

|   | 3.2             | ARM AMBA AHB-Lite                                                       | 6  |

|   |                 | 3.2.1 Introduction to AHB-Lite slave                                    | 9  |

|   |                 | 3.2.1.1 About the protocol                                              | 9  |

|   |                 | 3.2.1.2 Master                                                          | 0  |

|   |                 | 3.2.1.3 Slave                                                           | 0  |

|   |                 | 3.2.1.4 Decoder                                                         | 1  |

|   |                 | 3.2.1.5 Mutiplexor                                                      |    |

|   |                 | 3.2.1.6 Operation                                                       |    |

|   |                 | 3.2.2 Signal Description                                                |    |

|   |                 | 3.2.2.1 General Signals                                                 |    |

|   |                 | 3.2.2.2 Master Signals                                                  |    |

|   |                 | 3.2.2.3 Slave Signals                                                   |    |

|   |                 | 3.2.2.4 Decoder Signals                                                 |    |

|   |                 | 3.2.2.5 Multiplexor Signals                                             |    |

|   |                 | 3.2.3 AHB-Lite Slave Transfers                                          |    |

|   |                 | 3.2.3.1 Basic Transfers                                                 |    |

|   |                 | 3.2.3.2 Transfer Types                                                  |    |

|   |                 | 3.2.3.3 Transfer Size                                                   |    |

|   |                 | 3.2.3.4 Burst Operation                                                 |    |

|   |                 | 1                                                                       |    |

|   |                 |                                                                         |    |

|   |                 | 3.2.4 Slave Response Signaling                                          |    |

|   |                 | 3.2.4.1 Slave Transfer Responses                                        |    |

|   |                 | 3.2.5 Data Buses                                                        |    |

|   |                 | 3.2.5.1 Data Buses                                                      |    |

|   |                 | 3.2.6 Clock and Reset                                                   |    |

|   |                 | 3.2.6.1 Clock                                                           |    |

|   |                 | 3.2.6.2 Reset                                                           | 3  |

| 4 | From            | nt End Flow                                                             | 1  |

| - | 4.1             | ARM Specifications, Circuit Description/Architecture                    |    |

|   | 4.2             | RTL Coding                                                              |    |

|   | 1.2             | 4.2.1 Modifications                                                     |    |

|   |                 | 4.2.2 Code Fragments                                                    |    |

|   | 4.3             | Functional Simulation                                                   |    |

|   | 4.0             | 4.3.1 Test Bench                                                        |    |

|   | 4.4             | Logic Synthesis                                                         |    |

|   | 4.4             |                                                                         |    |

|   |                 | 1                                                                       |    |

|   |                 | 9                                                                       |    |

|   |                 | 4.4.2.1 Analyze and Elaborate                                           |    |

|   |                 | 4.4.2.2 Read File                                                       |    |

|   |                 | 4.4.3 Define Design Environment                                         | ٠J |

#### CONTENTS

|          |       | 4.4.4 Set Design Constraints                    | 32         |

|----------|-------|-------------------------------------------------|------------|

|          |       | 4.4.5 Design Rule Constraints                   | 33         |

|          |       | 4.4.6 Design Optimization Constraints           | 33         |

|          |       | 4.4.7 Compile strategy                          | 35         |

|          |       | 4.4.7.1 Top-Down Hierarchical compile method 6  | 66         |

|          |       | 4.4.7.2 Bottom-Up Hierarchical compile method 6 | 66         |

|          |       | 4.4.8 Optimizing the Design                     | 37         |

|          |       | 4.4.8.1 Architectural Optimization              | 37         |

|          |       | 4.4.8.2 Logic-Level Optimization                | 37         |

|          |       | 4.4.8.3 Gate Level Optimization                 | 37         |

|          | 4.5   |                                                 | 70         |

|          |       |                                                 | 70         |

|          |       |                                                 | 71         |

|          |       |                                                 | 71         |

|          | 4.6   |                                                 | 71         |

|          | 4.7   |                                                 | 73         |

|          | 4.8   |                                                 | 75         |

|          |       |                                                 |            |

| <b>5</b> | Bac   |                                                 | 7          |

|          | 5.1   | 1                                               | 78         |

|          |       | 5.1.1 I/O File                                  | 30         |

|          |       | 0 1                                             | 34         |

|          | 5.2   | 1                                               | 36         |

|          | 5.3   | Power Plan                                      | 38         |

|          | 5.4   | Placement and Routing                           | 90         |

|          |       | 5.4.1 Pre-CTS optimization                      | )1         |

|          | 5.5   | Clock Tree Synthesis                            | 93         |

|          | 5.6   | Power Analysis                                  | 96         |

|          | 5.7   | Verification                                    | 98         |

|          | 5.8   | Design Finishing                                | 0(         |

|          | 5.9   | Static Timing Analysis                          | )2         |

|          | 5.10  | Signoff Formal Verification                     | )4         |

| 6        | Res   | ults 10                                         | 15         |

| U        | ICS   | intes .                                         | ,0         |

| 7        | Con   | nclusion and future work 10                     | 9          |

|          | 7.1   | Conclusion                                      | -          |

|          | 7.2   | Future Work                                     | 1          |

| 8        | Δnr   | pendix A 11                                     | 7          |

| J        | 8.1   | Design Compiler Results                         |            |

|          | 8.2   | TetraMAX ATPG Results                           |            |

|          | 8.3   | SoC Encounter Results                           |            |

|          | 8.4   | Tempus STA Results                              |            |

|          | 0.4   | Tempus DIA Results                              | ,U         |

| Bi       | bliog | graphy 15                                       | <b>i</b> 1 |

### List of Tables

| 3.1  | Global Signals              | 2 |

|------|-----------------------------|---|

| 3.2  | Master Signals              | 3 |

| 3.3  | Slave Signals               | 4 |

| 3.4  | Decoder Signals             | 4 |

| 3.5  | Multiplexor Signals         | 5 |

| 3.6  | Transfer type encoding      | 8 |

| 3.7  | Transfer size encoding      | 8 |

| 3.8  | Burst signal encoding       | 9 |

| 3.9  | HRESP signal                | 1 |

| 3.10 | Transfer response           | 2 |

| 4.1  | Library variables           | 4 |

| 4.2  | Wire load models comparison | 2 |

| 5.1  | Global Signals              | 0 |

| 6.1  | Final Results               | 6 |

| 6.2  | Power Results               | 6 |

| 6.3  | Area Results                | 6 |

| 6.4  | Run time Results            | 7 |

| 6.5  | Library process comparison  | 7 |

| 6.6  | Library process comparison  | 7 |

| 6.7  | Library process comparison  | 8 |

### List of Figures

| 1.1  | Electronic systems example                                                                                             |

|------|------------------------------------------------------------------------------------------------------------------------|

| 2.1  | Moore's Law                                                                                                            |

| 2.2  | Design Flow                                                                                                            |

| 2.3  | Non scan vs. Multiplexed Flip-Flop Style                                                                               |

| 2.4  | Non-scan vs. Scan mode                                                                                                 |

| 3.1  | AHB-lite single master system                                                                                          |

| 3.2  | AHB-Lite components                                                                                                    |

| 3.3  | AHB-Lite block diagram                                                                                                 |

| 3.4  | Master interface                                                                                                       |

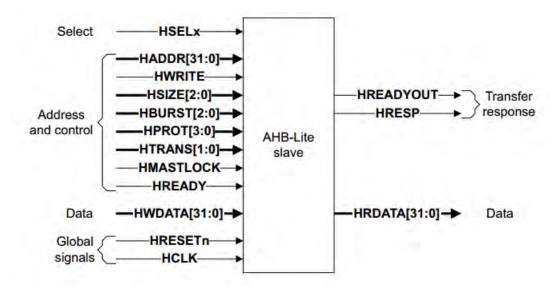

| 3.5  | Slave interface                                                                                                        |

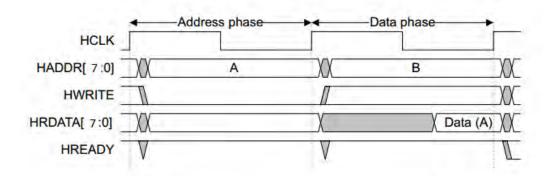

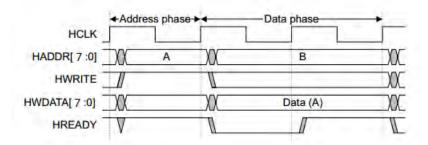

| 3.6  | Read transfer                                                                                                          |

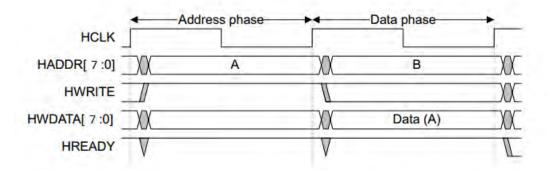

| 3.7  | Write transfer                                                                                                         |

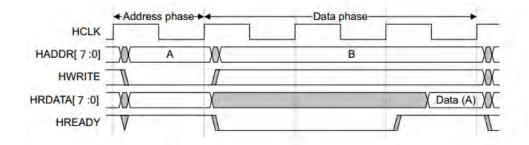

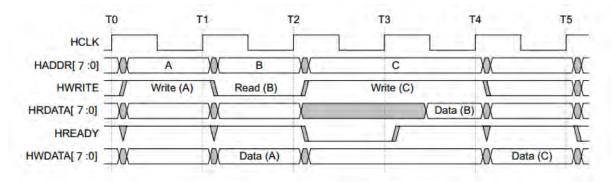

| 3.8  | Read transfer with two wait states                                                                                     |

| 3.9  | Write transfer with one wait state                                                                                     |

| 3.10 | Multiple transfers                                                                                                     |

| 0.10 |                                                                                                                        |

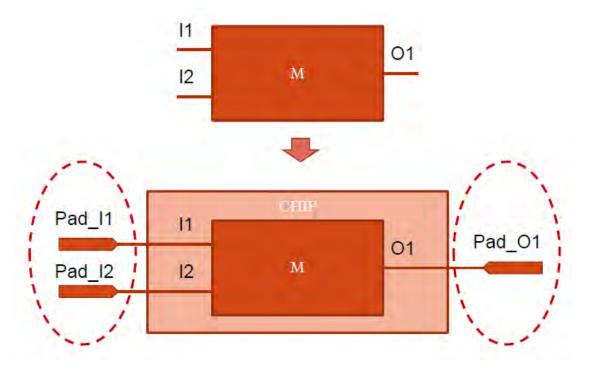

| 4.1  | From pins to pads                                                                                                      |

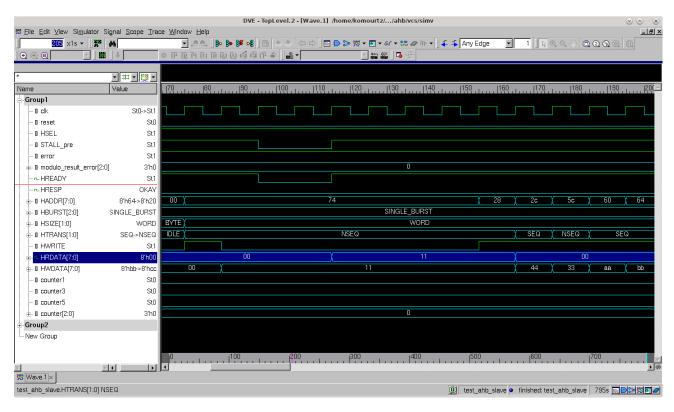

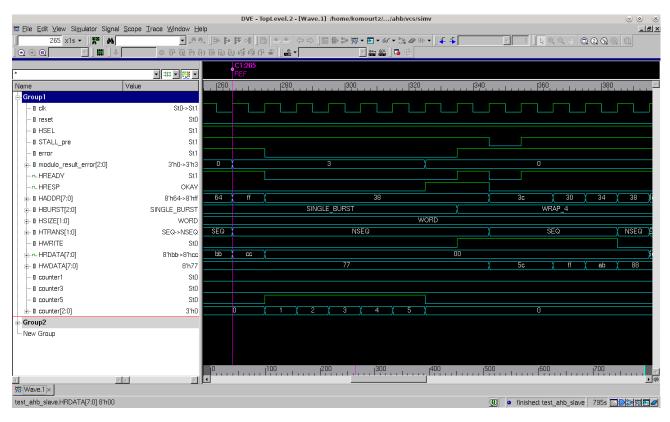

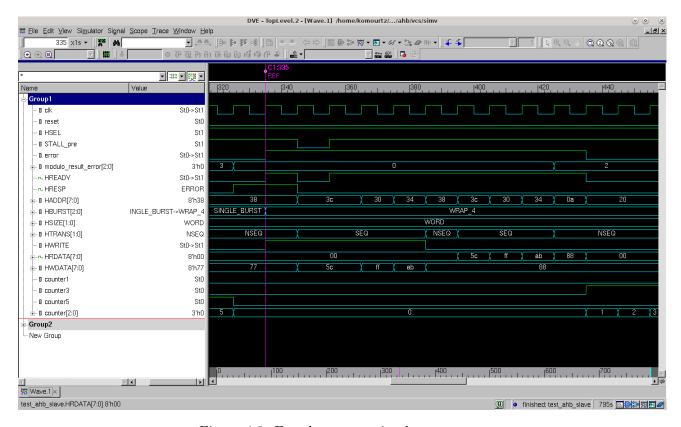

| 4.2  | Synopsys VCSMX initial waveform                                                                                        |

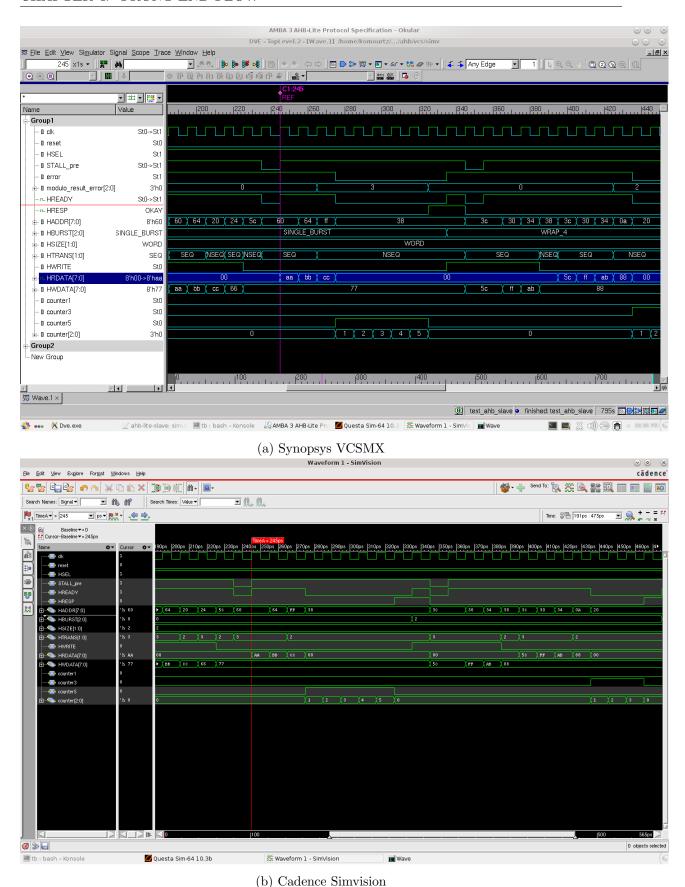

| 4.3  | Synopsys VCSMX vs Cadence Simvision initial waveform                                                                   |

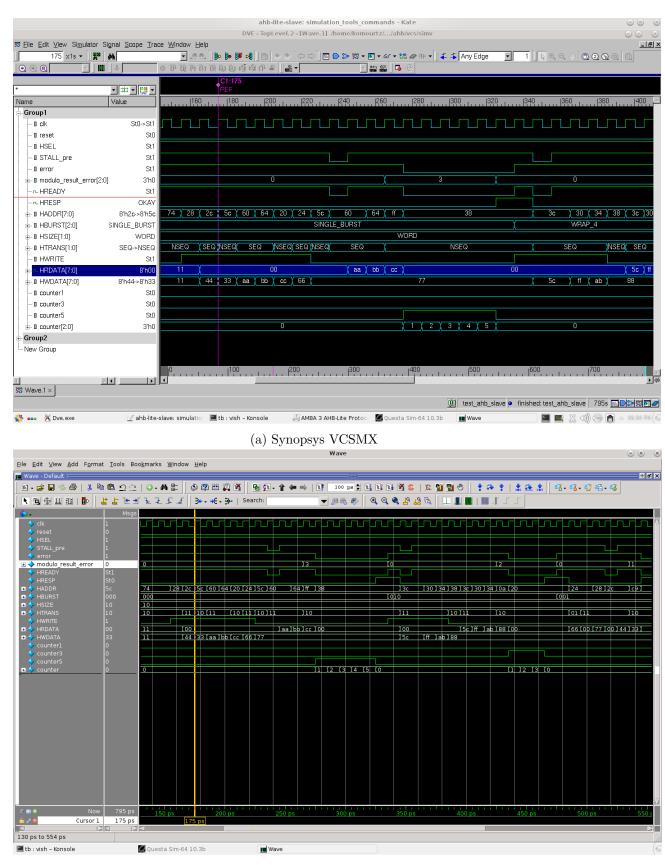

| 4.4  | Synopsys VCSMX vs Cadence Simvision initial waveform                                                                   |

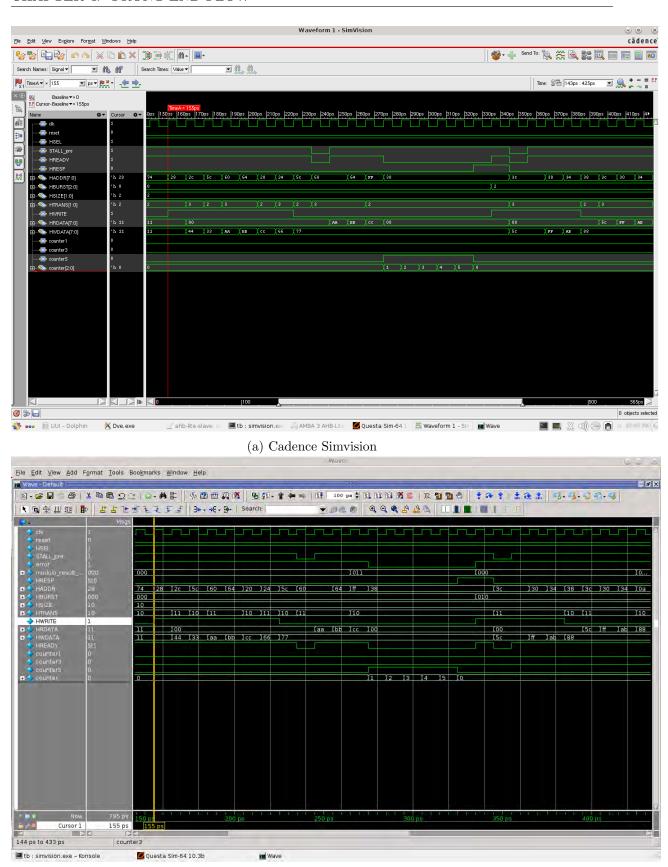

| 4.5  | Cadence Simvision vs Mentor Graphics Questasim initial waveform 45                                                     |

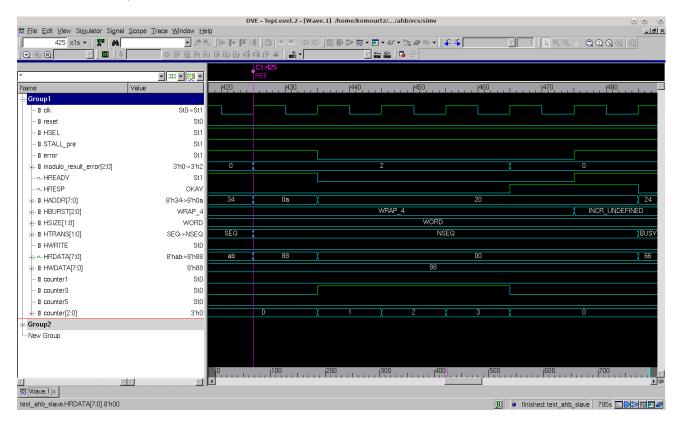

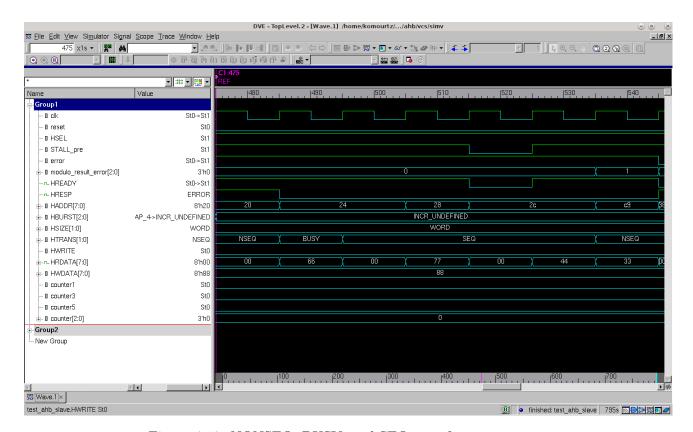

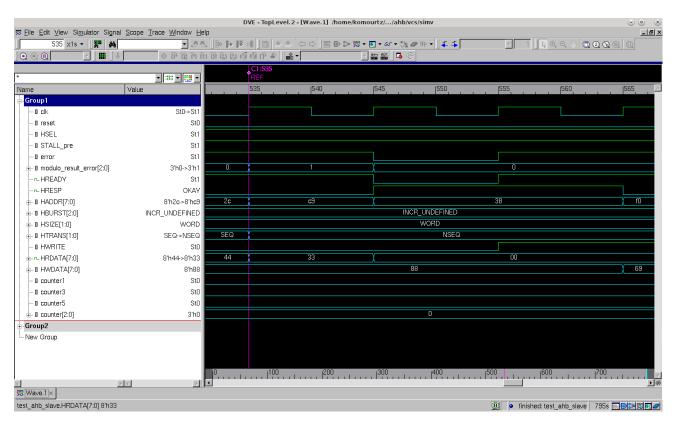

| 4.6  | Undefined length bursts, INCR                                                                                          |

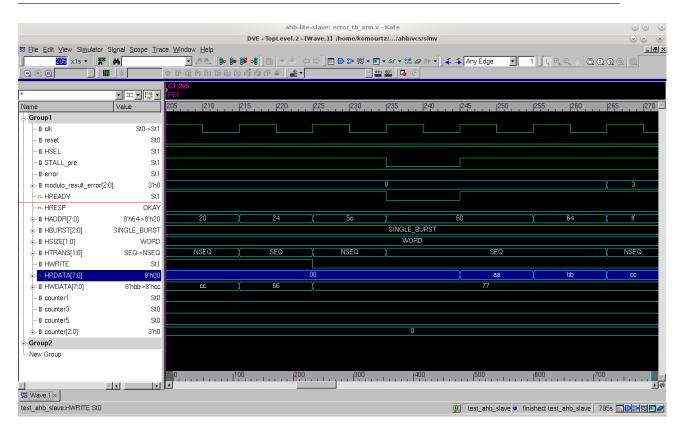

| 4.7  | Error response with five wait cycles                                                                                   |

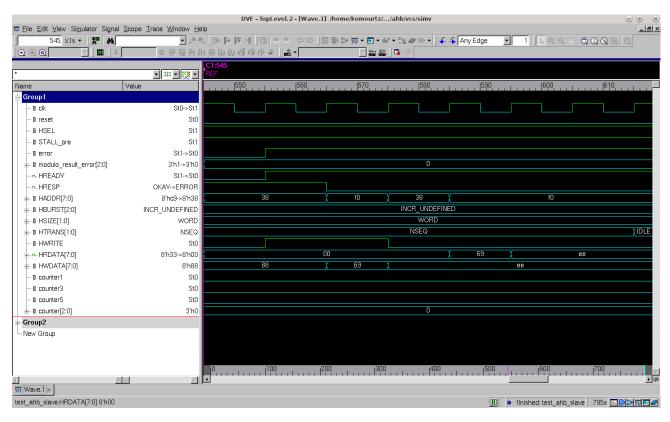

| 4.8  | Four-beat wrapping burst                                                                                               |

| 4.9  | Error response with three wait cycles                                                                                  |

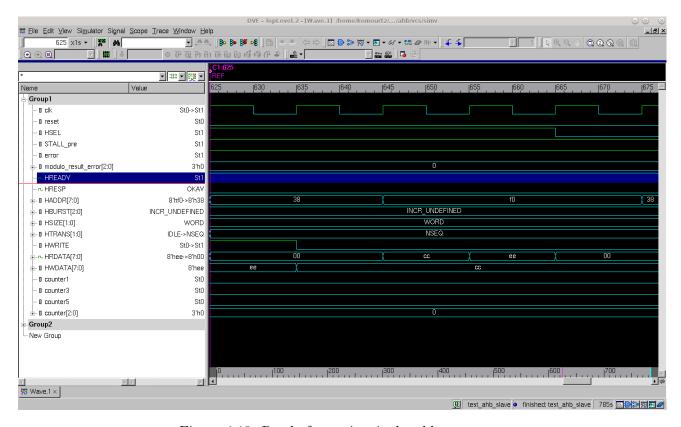

| 4.10 | NONSEQ, BUSY, and SEQ transfer types                                                                                   |

| 4.11 | Error response with no wait cycles                                                                                     |

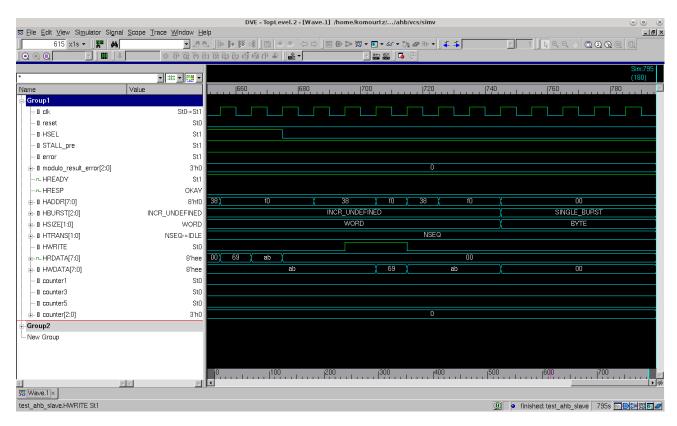

| 4.12 | Read after write with two addresses                                                                                    |

| 4.13 | Read after write single address                                                                                        |

| 4.14 | $HSEL = 0 \dots \dots$ |

| 4.15 | Synopsys Design Compiler                                                                                               |

| 4.16 | Libraries different flavors                                                                                            |

|      | Corelib 2x1 Nand Gate                                                                                                  |

|      | Corelibd 2x1 Nand Gate                                                                                                 |

|      |                                                                                                                        |

|      | Corelib Nand 5Volts 2x1                                                                                                |

|      | Corelib Nand 5Volts 2x1                                                                                                |

#### LIST OF FIGURES

| 4.22 | Wire load models                                              |  |  |  |       | 62  |

|------|---------------------------------------------------------------|--|--|--|-------|-----|

|      | B Driving characteristics                                     |  |  |  |       |     |

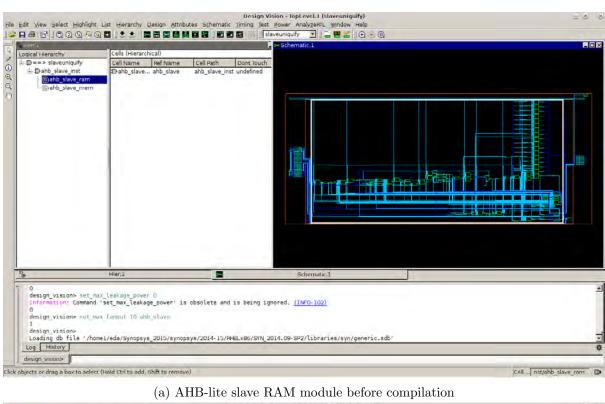

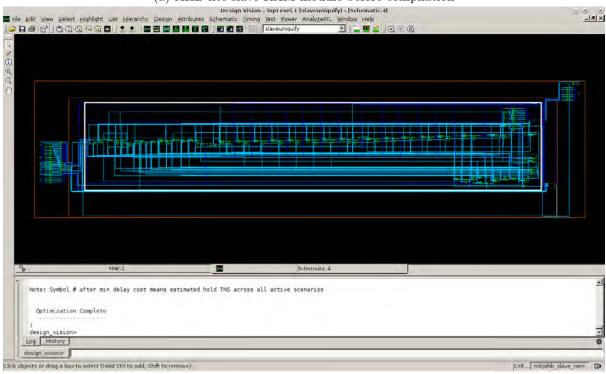

| 4.24 | A AHB-lite slave RAM module before vs after compilation       |  |  |  |       | 69  |

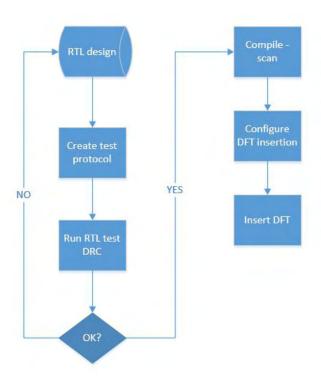

| 4.25 | 5 DFT insertion flow                                          |  |  |  |       | 70  |

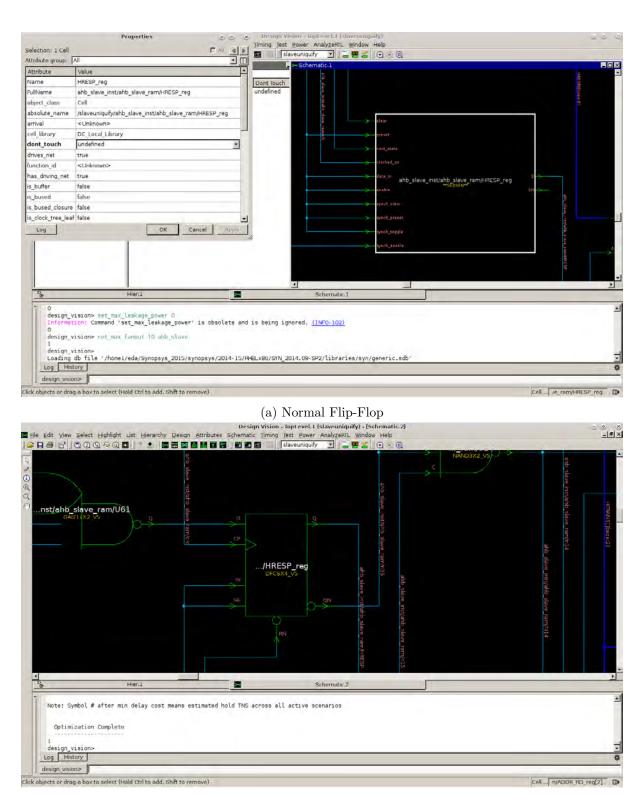

| 4.26 | 8 Register vs Scan Register                                   |  |  |  |       | 72  |

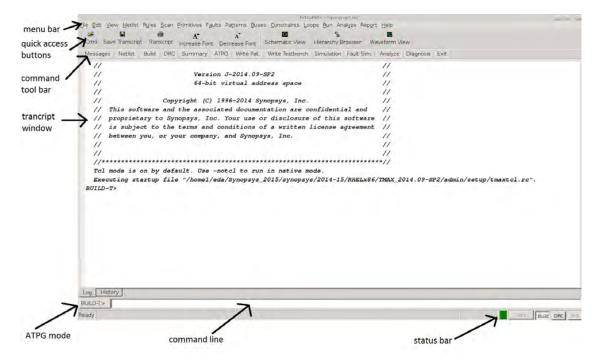

| 4.27 | Synopsys TetraMax ATPG Init Screen                            |  |  |  |       | 73  |

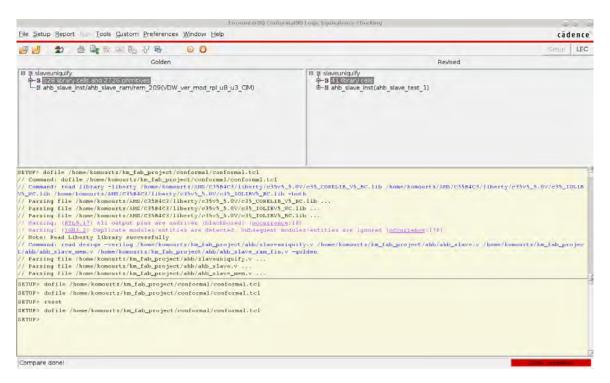

| 4.28 | 3 Cadence Conformal GUI mode                                  |  |  |  |       | 76  |

| 5.1  | Standard cell interconnection                                 |  |  |  |       |     |

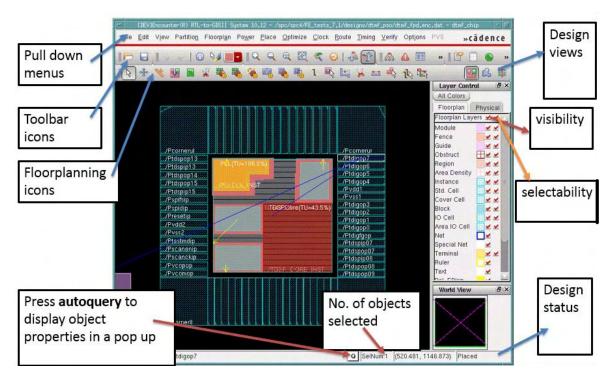

| 5.2  | SoC EDI initial GUI                                           |  |  |  |       |     |

| 5.3  | c35 IOLIB Cells 3.3V                                          |  |  |  |       | 81  |

| 5.4  | c35 IOLIBV5 Cells 5.0V                                        |  |  |  |       | 82  |

| 5.5  | Wafer Cross                                                   |  |  |  |       |     |

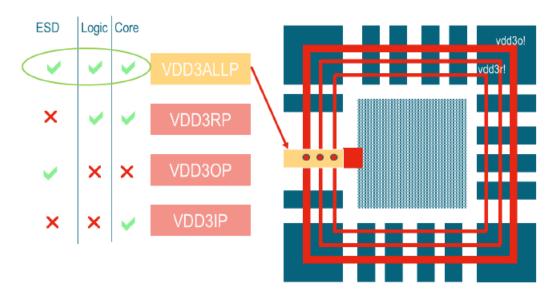

| 5.6  | Power Buses for the pad limited C35 IO cells                  |  |  |  |       | 83  |

| 5.7  | Design Import                                                 |  |  |  |       | 84  |

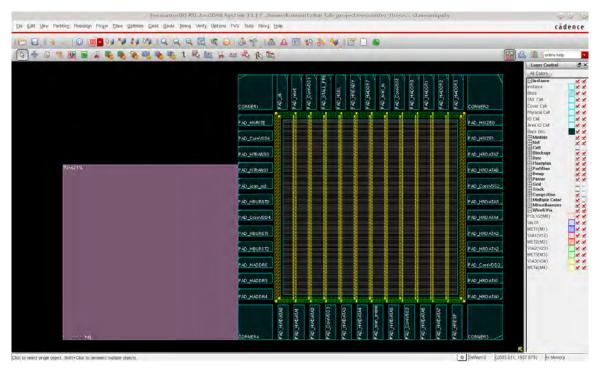

| 5.8  | Floorplan                                                     |  |  |  |       | 86  |

| 5.9  | Floorplan dimensions                                          |  |  |  |       |     |

|      | Power Plan                                                    |  |  |  |       |     |

| 5.11 | Power Pads                                                    |  |  |  |       | 89  |

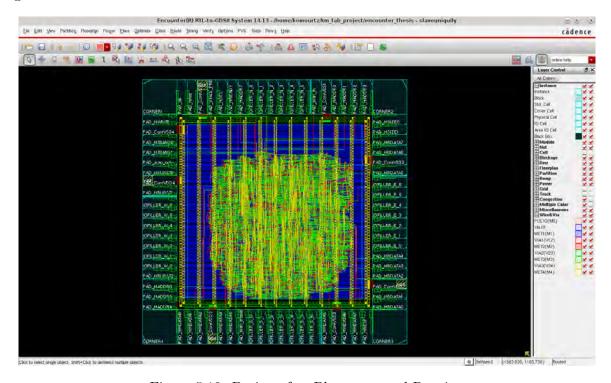

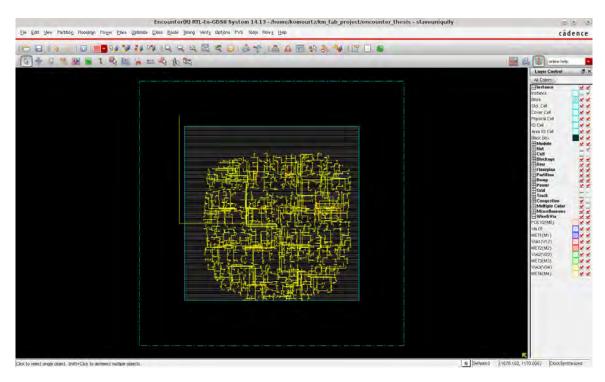

|      | 2 Design after Placement and Routing                          |  |  |  |       | 91  |

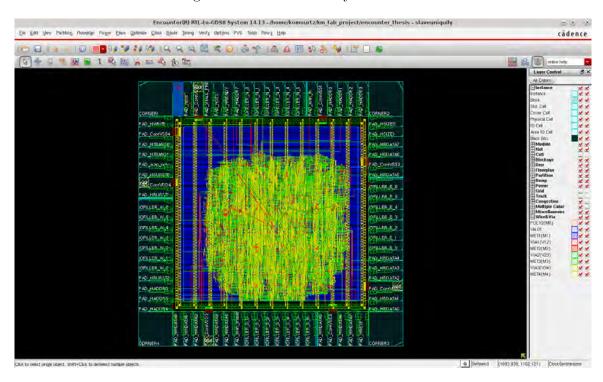

| 5.13 | B Design after Placement and Routing Optimization (Pre CTS) . |  |  |  |       | 92  |

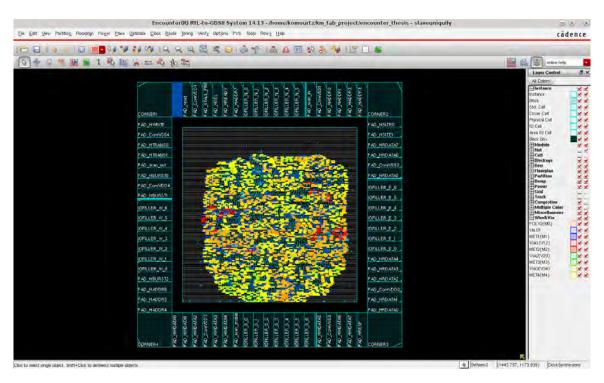

| 5.14 | 4 Clock Tree Synthesis no.1                                   |  |  |  |       | 93  |

| 5.15 | 6 Clock Tree Synthesis no.2                                   |  |  |  |       | 94  |

| 5.16 | 6 Clock Tree Synthesis display min max paths                  |  |  |  |       | 94  |

| 5.17 | 7 Clock Tree Synthesis phase delay                            |  |  |  |       |     |

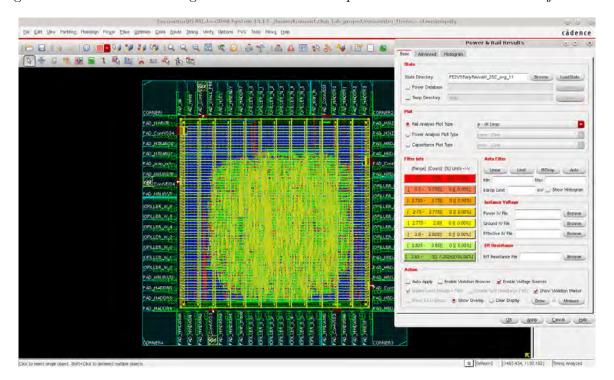

|      | 3 Static Power Analysis IR drop                               |  |  |  |       |     |

|      | Auto Power Analysis IR drop                                   |  |  |  |       |     |

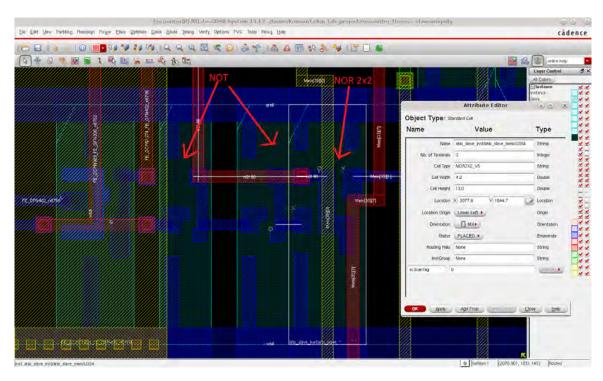

|      | Wire edit example                                             |  |  |  |       |     |

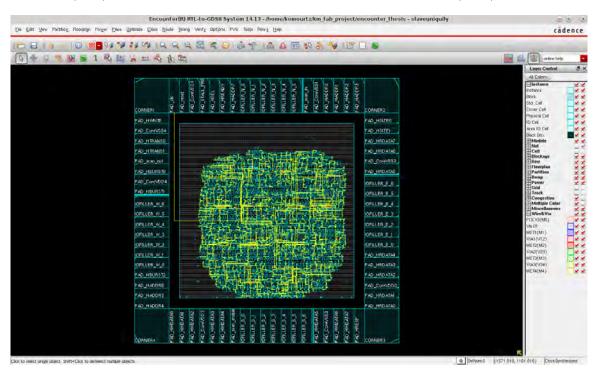

| 5.21 | Design Finishing filler cells                                 |  |  |  |       | 100 |

|      | 2 Design Finishing filler cells                               |  |  |  |       |     |

| 5.23 | B Routed Signals Closer look                                  |  |  |  |       | 101 |

|      | 4 Cadence Tempus initial GUI with necessary files             |  |  |  |       |     |

| 5.25 | 6 Cadence Tempus setup time histogram                         |  |  |  |       | 103 |

| 5.26 | 6 Cadence Tempus hold time histogram                          |  |  |  | <br>• | 103 |

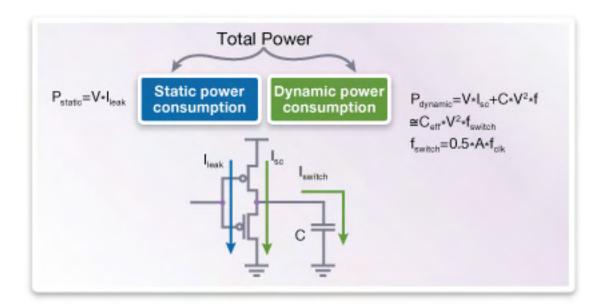

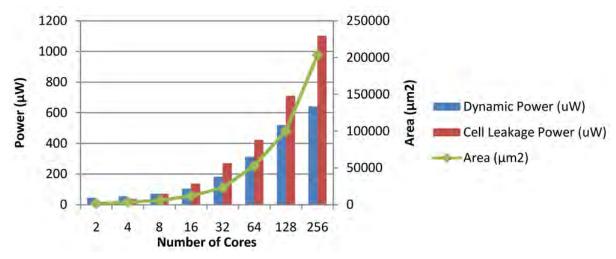

| 7.1  | Total circuit power                                           |  |  |  |       | 112 |

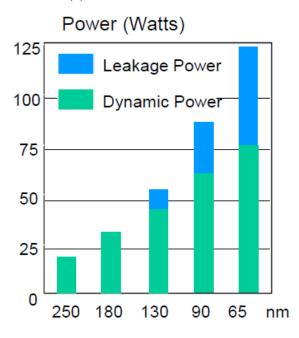

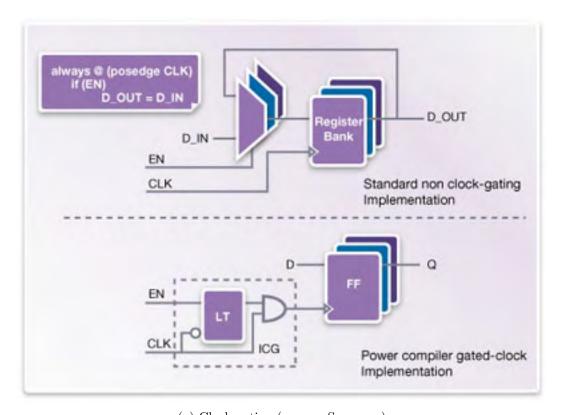

| 7.2  | Power distribution with technology scaling                    |  |  |  |       | 113 |

| 7.3  | Synopsys VCSMX vs Cadence Simvision initial waveform          |  |  |  |       | 114 |

| 7.4  | Advanced low-power techniques                                 |  |  |  |       | 115 |

### Listings

| 4.1   | ahb_slave_mem.v                 | 36 |

|-------|---------------------------------|----|

| 4.2   | ahb_slave_ram_read              | 37 |

| 4.3   | ahb_slave_ram_write             | 38 |

| 4.4   | ahb_slave_ram.v                 | 38 |

| 4.5   | ahb_slave_ram_signals           | 39 |

| 4.6   | ahb_slaveuniquify               | 10 |

| 4.7   | .synopsys_dc.setup              | 54 |

| powe  | ${ m er}$ -part.txt             | 13 |

| slave | uniquify_postRoute_hold.summary | 18 |

#### Abbreviations

ACE AXI Coherency Extensions. 15

**AHB** Advanced High-performance Bus. xii, 3, 15–22, 24, 25, 32, 33, 35, 36, 60, 89

AMBA Advanced Microcontroller Bus Architecture. xii, 3, 15, 19, 36, 89, 130

AMS Austria Microsystems. xii, 11, 89

APB Advanced Peripheral Bus. 15, 19

**ARM** Advanced RISC Machines. xii, 3, 6, 15, 35, 36, 89

**ASB** Advanced System Bus. 15

ASCII American Standard Code for Information Interchange. 83

ASIC Application Specific Integrated Circuit. 11, 15

ATB Advanced Trace Bus. 15

ATPG Automatic Test Pattern Generation. 12, 63, 65, 89

AXI Advanced Extensible Interface. 15

**BDD** Binary Decision Diagram. 66

CHI Coherent Hub Interface. 15

**CPU** Central Processing Unit. 15

CTS Clock Tree Synthesis. xii, 2, 8, 77

CUT Circuit Under Test. 9, 10

**DFT** Design For Testability. xii, 2, 9, 60, 63, 130

**DRC** Design Rule Check. 9, 12, 55, 59, 62, 64, 77, 79–81, 90

**DUT** Device Under Test. 9, 37

**EDA** Electronic Design Automation. xii, 2, 3, 5, 7, 8, 12, 13, 36, 37, 83, 85, 87, 89

**ERC** Electrical Rule Checking. 9

FSM Finite State Machine. 66

**GDS** Graphic Data System. 3, 8, 12, 80, 81, 83, 87, 89, 90

**GPU** Graphics Processing Unit. 15

HDL Hardware Description Language. 7, 37, 51, 59

IC Integrated Circuit. xii, 2, 5, 6, 11, 15, 130

${\bf iLs}$  Internet Learning Series. 13

**IP** Intellectual Property. 3, 15

LEC Logic Equivalence Checking. 66

LEF Library Exchange Format. 69

LSI Large Scale Integration. 5

LVS Layout vs. Schematic. 9

MMMC Multi Mode Multi Corner. 69

MSI Medium Scale Integration. 5

RTL Register Transfer Level. xii, 3, 7, 12, 35–37, 49, 50, 60, 66, 67, 69, 71, 89, 130

SDC Synopsys Design Constraints. 69

SDF Standard Delay Format. 12

**SoC** System on Chip. xii, 2, 3, 5, 8, 12, 15, 35, 71, 72, 77, 78, 81, 83–85, 89, 90, 130

SPEF Standard Parasitic Exchange Format. 83

SSI Small Scale Integration. 5

STA Static Timing Analysis. 8, 83, 90

SVF Serial Vector Format. 11

TCL Tool Command Language. 12, 69

TSMC Taiwan Semiconductor Manufacturing Company. 11

**UUT** Unit Under Test. 7

VLSI Very Large Scale Integration. xii, 3, 5, 89

### Περίληψη

Η σχεδιαστική πολυπλοκότητα των Integrated Circuit (IC) (ολοκληρωμένων κυκλωμάτων) έχει αυξηθεί ραγδαία σε σχέση με τα πρώτα κυκλώματα στα τέλη της δεκαετίας του 50, όπου ο αριθμός των τρανζίστορ ήταν πού μικρότερος. Στις μέρες μας, τα System on Chip (SoC) κυκλώματα περιέχουν εκατομμύρια ή δισεκατομμύρια τρανζίστορ και όχι μόνο η εμπειρία του σχεδιαστή αλλά και η μεθοδολογία σχεδίασης με εργαλέια Electronic Design Automation (EDA) χρειάζεται για να καταλήξουμε στην κατασκευή ενός ολοκληρωμένου κυκλώματος.

Ο στόχος αυτής της διπλωματικής είναι η σχεδίαση και υλοποίηση σε τεχνολογία 350nm Austria Microsystems (AMS) ενός Advanced RISC Machines (ARM) Advanced Microcontroller Bus Architecture (AMBA) Advanced High-performance Bus (AHB)-lite slave με την χρήση εργαλείων CAD των τριών μεγαλύτερων κατασκευαστών (Cadence, Synopsys, Mentor Graphics) ακολουθώντας την τυπική βιομηχανική ροή σχεδίασης. Κατά τα διάφορα βήματα της σχεδιαστικής ροής Very Large Scale Integration (VLSI) (συμπεριφορά και επαλήθευση των προδιαγραφών του κυκλώματος, σύνθεση και εξαγωγή του τελικού layout), θα δείξουμε πως αντιμετωπίσαμε τα προβλήματα που προέκυψαν (Εισαγωγή Design For Testability (DFT), Κάλυψη λαθών, σύνθεση δέντρου ρολογιού, κτλ.)

Ξεκινώντας απο τον κώδικα Register Transfer Level (RTL) τον οποίο βρήκαμε στο website opencores, το τελικό αποτέλεσμα θα είναι ένα πλήρως λειτουργικό κύκλωμα Advanced RISC Machines (ARM) Advanced Microcontroller Bus Architecture (AMBA) Advanced High-performance Bus (AHB)-lite slave που θα σταλεί για κατασκευή στις 27<sup>th</sup> Ιουλίου σύμφωνα με Europractice 2015 MPW run schedule. Τέλος, η περίοδος του ρολογιού θα είναι στα 80,64 MHz (12.4ns), το τελικό μέγεθος 6,76mm² και η τάση που θα λειτουργεί το κύκλωμα θα είναι 3,3 Volts.

#### Abstract

Integrated Circuit (IC) design complexity has increased radically since the first designs in the late 50s, with a few transistors. Nowadays, System on Chip (SoC) designs contain million or even billion transistors and not only the experience of the designer, but also Electronic Design Automation (EDA) tools and a design methodology is needed in order to reach at the fabrication of a chip.

The goal of this thesis is the design and implementation in 350nm Austria Microsystems (AMS) technology of an Advanced RISC Machines (ARM) Advanced Microcontroller Bus Architecture (AMBA) Advanced High-performance Bus (AHB)-lite slave using Electronic Design Automation (EDA) tools from all three big vendors (Cadence, Synopsys, Mentor Graphics) following a typical industrial tool flow. During the different steps of the Very Large Scale Integration (VLSI) design flow (behavioral specification and verification, synthesis and layout generation), it will be shown how to deal with the design issues that arise: (Design For Testability (DFT) insertion, test coverage, Clock Tree Synthesis (CTS), etc.)

Starting from the Register Transfer Level (RTL) code originating from opencores website, the final result is a fully functional and tested Advanced RISC Machines (ARM) Advanced Microcontroller Bus Architecture (AMBA) Advanced High-performance Bus (AHB)-lite slave circuit with no violations of any kind that will be sent for fabrication at  $27^{\text{th}}$  of July according to Europractice 2015 MPW run schedule. Finally, the clock frequency of the circuit will be at 83.3 MHz, the final area will be  $7mm^2$  and the voltage that will operate will be at 5 Volts.

### Chapter 1

### Introduction

In the past people used technology as a tool for making survival an easier endeavor. Nowadays we are witnessing a shift in the role technology is playing in our society and may continue to play for generations to come. Every human out there in this age simply cannot imagine his life without technology and an internet connection. Some applications of technology evolution are helpful for humanity such as bio medical implants, others main concern is the improvement of living such as home applications while others are purely for entertainment such as smart phones, personal computers, tablets, smart TVs. As mentioned before there are many different electronic systems out there (Figure 1.1). In the scheme of continuous development, electronic devices becoming more and more complex (which sometimes means difficult to use), rather than the first Integrated Circuit (IC) developed in the late 50s with a few transistors design all by hand to current Integrated Circuit (IC) [4] and System on Chip (SoC) [6] with billions of transistors. The key point to that evolution was the development of Electronic Design Automation (EDA) tools. Another challenge that we have to face nowadays is the "shrinking" of the transistors. This "shrinking" is necessary because we want to place billions of transistors to a small area at the size of the head of a nail. The field of this thesis is to examine the parts(synthesis, Clock Tree Synthesis (CTS), Design For Testability (DFT), power distribution,...) of a puzzle that we have to solve in order to fabricate a chip.

Figure 1.1: Electronic systems example

#### 1.1 Motivation

Nowadays, many new companies started to develop their own Intellectual Property (IP) such as ARM [7] and provide them to other companies that needed to integrate them to their electronic devices. These IPs are developed with the help of Electronic Design Automation (EDA) tools in order to achieve the desired performance, power and area requirements. The EDA tools run algorithms developed from the experience of designers in the field of VLSI and they automate many parts of the design process that could take years if SoCs designed by hand. So, the need for people who know to handle these tools as well as having the relevant VLSI background is necessary to help the technology and our living become better.

#### 1.2 Thesis Goals

The main goal of this thesis is to complete a VLSI design flow at the 350nm technology node with the latest versions of EDA tools which legally provided for academic use from Europractice agreement my department has, in order to set up a design environment for more complex designs. My secondary goals are:

- Ensure that after the modifications done, the circuit works perfectly and it has the same functionality as the one that is integrated in ARM [7] SoCs.

- Send the circuit after the design flow for fabrication to a foundry that cooperate with Europractice.

#### 1.3 Thesis Sructure

This thesis is divided in six main Chapters which include:

- Chapter 2 provides the necessary background information in order the reader fully understands the development and the final results of this project. First of all, it gives the basic knowledge about methodology and tools used in the design, as well a sort description of the design library that is used.

- Chapter 3 presents the ARM [7] AMBA AHB protocol, explaining the functionality of the signals that compose the specific circuit this thesis is about.

- Chapter 4 is about the front end flow of the design. This includes at the beginning RTL coding and modifications needed to be done in order the circuit will be functional during simulations. Afterwards, is described the logic synthesis part of the flow and the constraints applied to the circuit. Finally, is described the scan chain insertion and test vectors extraction and the final tape-out checks.

- Chapter 5 presents the back end flow of the design starting from importing the design to the back end tool and finishing with the GDSII extraction which was sent for fabrication to the foundry.

- Chapter 6 and 7, summarizes the work done, the problems faced and the results generated and points to possible future work.

### Chapter 2

### Literature Review

#### 2.1 Brief ICs History

Opinions diverge on who inverted the first IC: Jack Kilby of Texas Instruments or Robert Noyce of Fairchild Semiconductor. The matter is that both of them contributed to achieve the birth of IC in 1958 and initiate a revolution in the circuit design field. Starting with Small Scale Integration (SSI) devices, with tens of transistors in the early 1960s, and Medium Scale Integration (MSI) devices, with hundreds of transistors in the late 1960s, were relatively simple to test. However, in the 1970s, Large Scale Integration (LSI) devices, with thousands and tens of thousands of transistors, created a number of challenges when testing these devices. In the early 1980s, Very Large Scale Integration (VLSI) devices with hundreds of thousands of transistors were introduced. Steady advances in VLSI technology have resulted in devices with hundreds of millions of transistors and many new challenges for developers and designers.

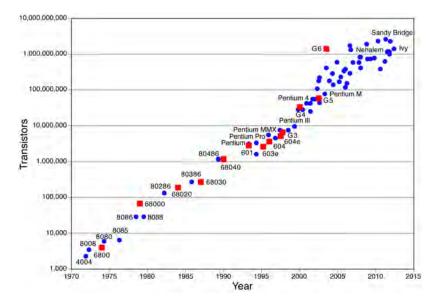

Following the so-called Moore's law [Moore 1965] (Figure 2.1), the scale of ICs has doubled every 18 months. A simple example of this trend is the progression from SSI to VLSI devices. In the 1980s, the term "VLSI" was used for chips having more than 100,000 transistors and has continued to be used over time to refer to chips with millions and now hundreds of millions of transistors. The first designs were designed by hand with the aid of microscopes and based only on the experience of the designer, but the more the transistors inside the circuits increase the more impracticable was the design without any help. This help is known as Electronic Design Automation (EDA) tools and was an essential part of the next evolution step in IC, the Very Large Scale Integration (VLSI) age, which was initiated at the early 80s with circuits including hundreds of thousands of transistors.

Nowadays, this number increased beyond several billion transistors and we reached to System on Chip (SoC) age, what makes clear the need of EDA tools and the methodology or design flow that allows managing huge designs like that. This is a direct result of the steadily decreasing dimensions, referred to as feature size, of the transistors and interconnecting wires from tens of microns to tens of nanometers, with current submicron technologies based on a feature size of less than 100 nanometers (14 nm). The reduction in feature size has also resulted in increased operating frequencies and clock speeds; for example, in 1971, the first microprocessor ran at a clock frequency of 108 KHz, while current commercially available microprocessors commonly run at several gigahertz. [19]

Figure 2.1: Moore's Law

#### 2.2 VLSI Design Flow

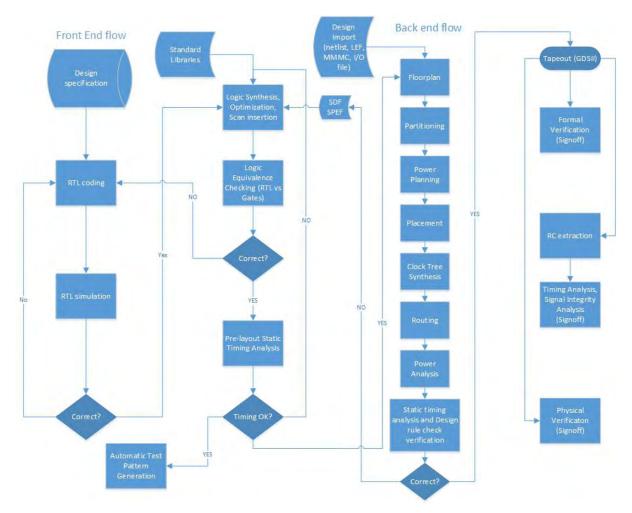

As described in the previous section, the need for a methodology was needed in order to create a full design flow that would allow us to handle big designs. In this section, we will present this methodology as was developed through the years from many industries to get a final error-free chip. The diverse steps of the full design flow are shown in Figure 2.2

Figure 2.2: Design Flow

#### 2.2.1 Design Specification

Design Specifications are the first step of the Design flow. They describe the functionality, interface and the architecture of the digital IC circuit to be designed. They also contain block diagrams of the circuit, signal description and some examples of waveforms in order to understand the functionality of the circuit. Finally in some design specification we may find a pseudo-code description of some functionality of the circuit. In this project the design specifications taken from ARM [7] website.

#### 2.2.2 RTL Description

Register Transfer Level (RTL) of a models the design in terms of the flow of digital signals between registers and logical operations performed on those signals. Register Transfer Level (RTL) abstraction is used in Hardware Description Language (HDL) like verilog to create a high-level representation of the circuit, from which lower-level representations are ultimately actual wiring can be derived. A synchronous circuit consists of two kinds of elements: registers and combinational logic. Registers (usually implemented as D flip-flops) synchronize the circuit's operation to the edges of the clock signal, and are the only elements in the circuit that have memory properties. Combinational logic performs all the logical functions in the circuit and it typically consists of logic gates. [5]

#### 2.2.3 Front End Flow

Front End Flow of the design consists of RTL simulation and Logic synthesis of the circuit.

#### 2.2.3.1 RTL simulation

After the RTL description of the design we have to check its functionality and if the code we composed works fine and gives us the behavior of the circuit according to the specifications. To achieve that we create test benches. Test bench is a specification written in verilog that plays the role of a complete simulation environment for the analyzed system (Unit Under Test (UUT)). A test bench contains both the UUT as well as stimuli for the simulation. The UUT is instantiated as a component of the test bench and the architecture of the test bench specifies stimuli for the UUT's ports, usually as waveform assigned to all output and bidirectional ports of the UUT. The entity of a test bench does not have any ports as this serves as an environment for the UUT. All the simulation results are reported using the assert and report statements. The correctness of the behavior is checked by a simulation program (Modelsim from Mentor Graphics, Simvision from Cadence or VCS from Synopsys) using test benches.

#### 2.2.3.2 Synthesis

After checking the correctness of the RTL, the next step is synthesis. Synthesis is the process in which the circuit is converted from a high-level description of design into an optimized gate-level representation. Synthesis includes the following parts:

- RTL Synthesis, Library Mapping: The code written in verilog HDL format is translated to a netlist representation of interconnected gates such as AND, OR, NOT, macro cells such as MUXes, adders and registers which mapped to the gates defined in the target library.

- **Design Constraints:** The designer after importing the design in the EDA synthesis tool has to set constraints such as timing, area and power that the design should meet in order to agree with the specifications given at the beginning.

#### 2.2.3.3 Post-synthesis verification

This step has to do with the post synthesis verification of the design. After getting the verilog netlist exported from EDA synthesis tool, we have to check the correctness of the circuit and if the synthesized netlist is the same in terms of logic with the initial RTL code we wrote. This can be done with running again testbenches that have been used before and checking the design with logic equivalence checking EDA tools.

#### 2.2.3.4 Static Timing Analysis

After we check the design for its behavioral and structural correctness, we have to do some final timing tests. A Static Timing Analysis (STA) can be run to check if the circuit meets the constraints we set in the section 2.2.3.2. If not, we should return to synthesis part of the flow to set new constraints that can reach the design requirements.

#### 2.2.4 Back End Flow

Back end flow is the flow that produces the final files which will sent to the foundry in order to fabricate a System on Chip (SoC). We take the netlist exported from the front end flow and we generate the final Graphic Data System (GDS)II file.

#### 2.2.4.1 Layout generation

In the next steps is briefly described the main back end flow:

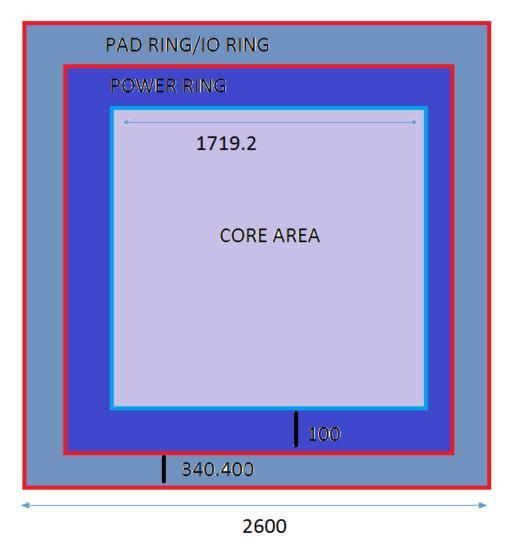

- Floorplaning: The first thing to do is to import the design and configure the floorplan of the design. The design is imported in hierarchical modules and we have to customize the area that is given from the EDA tool to perform the placement of these modules in this area.

- **Placement:** At this stage, modules are decomposed into standard cells and they placed inside the area we defined before. The EDA tool performs iterations with the aid of integrated algorithms which places the standard cells in a way to minimize the wire length of the design, the area the design should take and to decrease as much as possible the delay on the critical paths and achieve the best possible results in timing.

- Routing: Moving on, the placed cells need to be interconnected. There are two types of routing, global routing and detailed routing. Global routing allocates routing resources that are used for connections. Detailed routing assigns routes to specific metal layers and routing tracks within the global routing resources.

- Clock Tree Synthesis and Timing Analysis: After place and routing the design the static timing analysis reports will show us if the timing requirements of our design is accomplished or not. If not, Clock Tree Synthesis (CTS) may save the day. The goal of Clock Tree Synthesis (CTS) is to minimize skew and insertion delay. Clock is not propagated before CTS. After CTS hold slack should improve. The clock signal has to reach to all sequential elements of the circuit at the same time in order to achieve a correct functionality and avoid clock inaccuracy problems: clock skew and clock jitter.

- Power Analysis and finishing: During this step we check our final design in terms of power distribution before we proceed to tape-out.

#### 2.2.4.2 Physical Verification

Physical verification checks the correctness of the generated layout design. This includes verifying that the layout:

- Complies with all technology requirements Design Rule Check (DRC)

- Is consistent with the original netlist Layout vs. Schematic (LVS)

- Has no antenna effects Antenna Rule Checking

- This also includes density verification at the full chip level. Cleaning density is a very critical step in the lower technology nodes

- Complies with all electrical requirements Electrical Rule Checking (ERC)

Some of these physical verification steps may offered by the foundry while others needed to be done from the designer.

#### 2.3 Design for Test

Design For Testability (DFT) stands for IC design techniques that add certain testability features to a hardware product design. The premise of the added features is that they make it easier to develop and apply manufacturing tests for the designed hardware. The purpose of manufacturing tests is to validate that the product hardware contains no manufacturing defects that could, otherwise, adversely affect the product correct functioning. The tests generally are driven by test programs that execute in Automatic Test Equipment (ATE). In addition to finding and indicating the presence of defects (i.e., the test fails), tests may be able to log diagnostic information about the nature of the encountered test fails. The diagnostic information can be used to locate the source of the failure. In other words, the response of vectors(patterns) from a good circuit is compared with the response of vectors(using same patterns) from a Device Under Test (DUT). If the response is the same or matches, the circuit is good. Otherwise, the circuit is not manufactured as it is intended to do so.

DFT has two main parts:

- Controllability: It is the ability to control the nodes in a circuit by a set of inputs. For a given set of input and output pins, when we give the system a set of input test vectors, we should be able to control each node we want to test. The higher the degree of controllability, the better.

- Observability: It is the ease with which we can observe the changes in the nodes (gates). Like in the previous case the higher the observability, the better. What I mean by saying higher is that, we can see the desired state of the gates at the output in lesser number of cycles.

The most common method for delivering test data from chip inputs to internal Circuit Under Test (CUT)s, and observing their outputs, is called scan-design. In scan-design, registers (flip-flops or latches) in the design are connected in one or more scan chains, which are used to gain access to internal nodes of the chip. Test patterns are shifted in via the scan chain(s), functional clock signals are pulsed to test the circuit during the "capture cycle(s)", and the results are then shifted out to chip output pins and compared against the expected "good machine" results. [2]

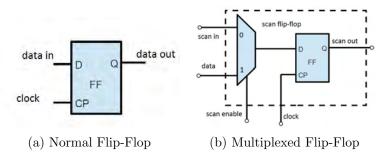

#### 2.3.1 Scan Chain insertion - Multiplexed Flip-Flop Style

The most common method for delivering test data from chip inputs to internal Circuit Under Test (CUT)s, and observing their outputs, is called scan-design. There are two methodologies:

- Partial Scan: Only some Flip-Flops are changed to Scan-FF.

- Full Scan: Entire Flip Flops in the circuit are changed to these special Scan FF. This does mean that we can test the circuit 100%.

If a design contains sequential components (like flip/flops), the design compiler can be used to replace these components with what is known as 'scan-cells.' A common example is replacing a d-flop-flop with a multiplexed flip-flop (a flip flop with a MUX in front of it). A multiplexed input allows us to load test data into a flip/flop as opposed the regular data, simply by using the 'select line' of the mux. When the select is low, the normal data that was meant to go into the flip-flop passes through to Q, but when the select is high, test data propagates through the flip-flop to the Q output(Figure 2.3).

Figure 2.3: Non scan vs. Multiplexed Flip-Flop Style

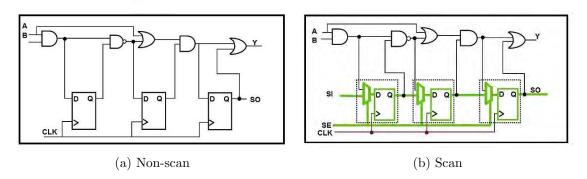

By replacing all of the flip-flops in a large design (assuming there are flip-flops throughout the design) with multiplexed flip-flops (scan-cells), we can increase the observability/controllability of all the non-sequential logic throughout the chip. The 'test data-input' and the 'select' lines of the scan-cells are wired to input pins; this creates what is known as a scan-chain. Now the user can put the chip into 'scan-mode' and load data into all the scan-cells. One can think of all the flip-flops in the design as having been stitched together into a giant 'shiftregister' allowing data to be inputted in at 1 pin (serially) and being able to move test data all over the chip, making the non-sequential portions of the design more observable/controllable then they were before (Figure 2.4).

Figure 2.4: Non-scan vs. Scan mode

Straightforward application of scan techniques can result in large vector sets with corresponding long tester time and memory requirements. Test compression techniques address this problem, by decompressing the scan input on chip and compressing the test output. The output of a scan design may be provided in forms such as Serial Vector Format (SVF), to be executed by test equipment.

#### 2.4 Standard Cell Design

As mentioned in the section 2.2 the goal of fabricating a chip is to produce the final layout of the design. There are two ways to do that, so IC physical design is categorized into:

- Full Custom: Designer has full flexibility on the layout design, no predefined cells are used. That means that the designer has to generate the layout of each standard cell specifications he will afterwards use at his design. This approach allows maximizing the performance of the circuit, but it is a time-consuming process if we want to apply it to big designs.

- **Semi Custom:** Pre-designed library cells are used. These pre-designed library cells or standard cells, created by using a full custom technique from foundries and developers, can be seen by the designer in abstract logic representation (logic gates, buffers, flip-flops, etc.) In this case the designer has flexibility in placement of the cells and routing focusing on the high-level aspect of the design.

In this thesis, the second way is used, so a library containing the standard cells should be provided. The library that has been used in this design is explained at the next section.

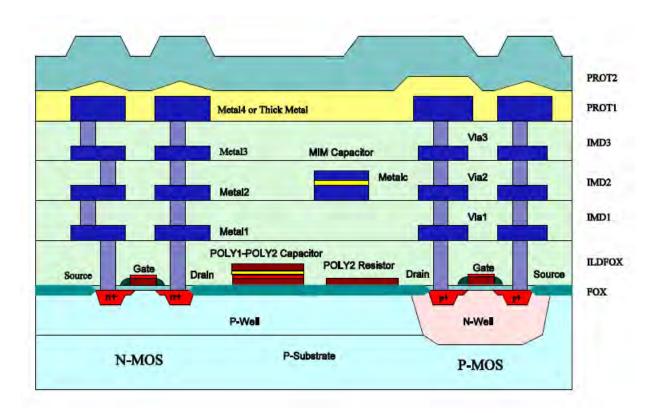

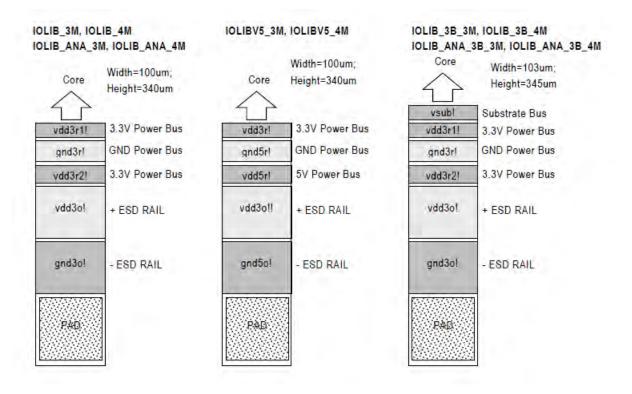

#### 2.4.1 AMS 350nm Standard Cell Library

The AMS C35B4C3 [9] (**Key specification:** C35B4C3 2P/4M 3.3V CMOS 4 Metal, Mixed Signal, PIP, high-res poly, 5V periphery) library from Austria micro systems used in this thesis is a 350nm standard cell library. AMS 350nm CMOS process family is fully compatible to the 350nm mixed signal base process licensed from Taiwan Semiconductor Manufacturing Company (TSMC). The high density CMOS standard cell library optimized for synthesis and 3 and 4 layer routing guarantees highest gate densities. Peripheral cell libraries are available for 3.3 V and 5 V with high driving capabilities and excellent ESD performance. Qualified digital macro blocks (RAM, diffusion programmable ROM and DPRAM) are available on request. A variety of high performance analog-to-digital and digital-to-analog converters can be provided for integration on the same Application Specific Integrated Circuit (ASIC). Digital, Analog and Mixed Signal Systems. The features of the library are:

- 350nm CMOS polycide-gate process

- Four unrestricted layers of metal

- Second layer of poly for linear capacitors and linear resistors

- Peripheral cells with high driving capability

- High performance digital and mixed signal capabilities

and some general characteristics are:

- p substrate

- Pseudo twin-well CMOS

- stacked contact, via, via2, via3

- Minimum Feature Size: 350nm gates

- Supply Voltage: CMOS 3.3 V; periphery up to 5.5 V

- Gate Delay: 0.10 ns (NAND2 typical)

The library contained all the necessary files for all the tools described in the section below.

#### 2.5 EDA Tools

In this section we give a brief presentation of EDA tools that have been used during the VLSI design flow:

- Simulation: Questasim(version 10.4) from Mentor Graphics, VCSMX (version 2014.12) from Synopsys and Simvision (Incisive suite version 14.10) from Cadence. These three tools provides the designer the ability to verify the functionality of the circuit at logic level. They also include timing information through Standard Delay Format (SDF) file, they support multi-language simulation (VHDL, Verilog, System Verilog) as well as Tool Command Language (TCL) scripting, among other features.

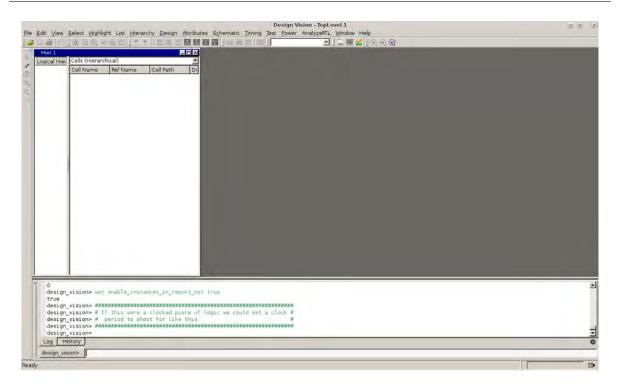

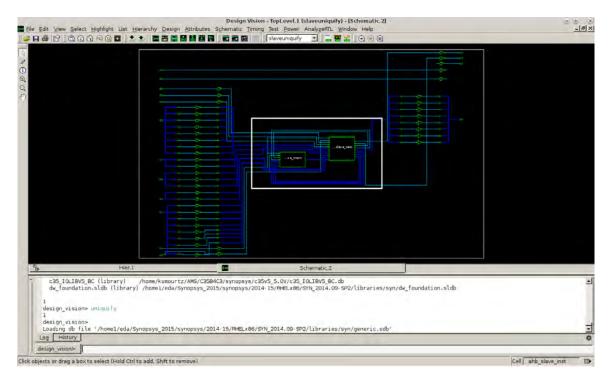

- Synthesis: Design Compiler (version 2014.09-SP2) from Synopsys. It is the most commonly used EDA tool for that purpose. Design Compiler transform the RTL code given from an abstract description to logic gate circuit mapped with the standard cell library that the designer decides to provide. It offers a robust environment that faces successfully design challenges such as: timing, area, power, scan chain insertion.

- Automatic Test Pattern Generation (ATPG): TetraMax (version 2014.09-SP2) from Synopsys. The tool provides accurate measurements for test coverage of the design and it exports the test vectors that will be used to test the design after the fabrication process.

- Logic Equivalence Checking: Conformal (version 14.10) from Cadence. After synthesis and after layout generation, the netlists exported needed to be tested for their logic equivalence with the initial RTL code. An error in this stage means that the final netlist has not the same functionality as the initial RTL code, so we need to fix these errors or rerun synthesis and back-end flow from scratch.

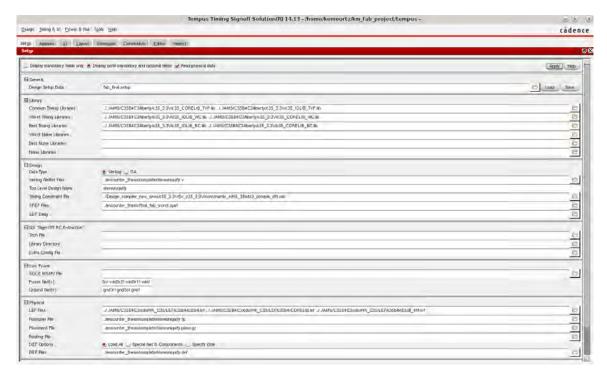

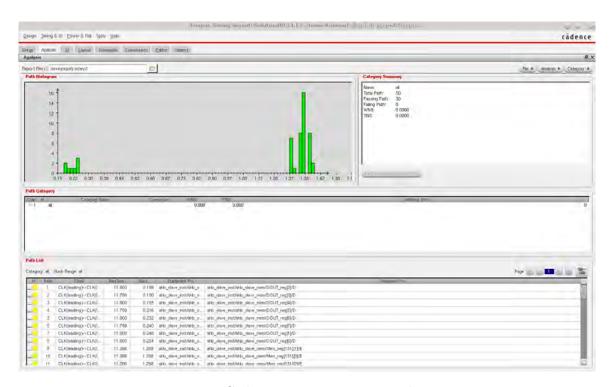

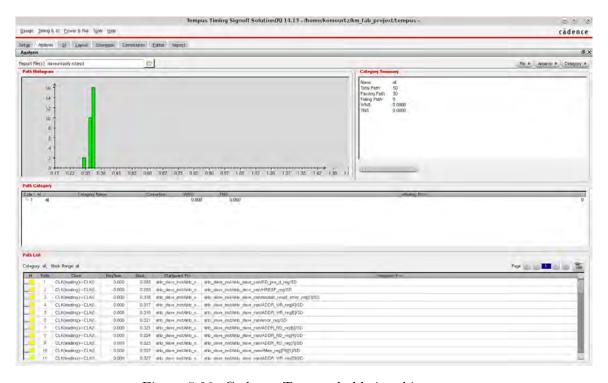

- Static Timing Analysis: Tempus (version 14.10) from Cadence and PrimeTime (version 2014.12) from Synopsys. For more accurate results in terms of timing after syntheis and after layout generation these two tools were used in order to ensure that the final design has no timing violation and it is ready to send to the foundry for fabrication.

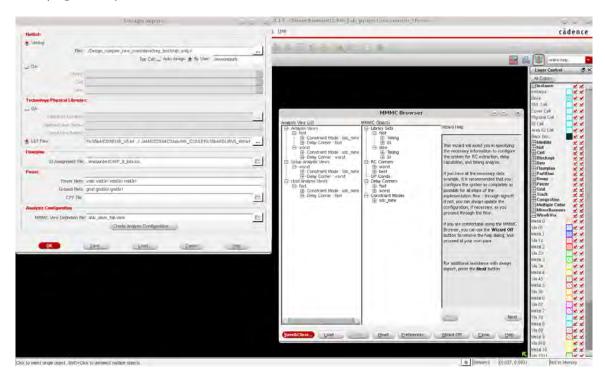

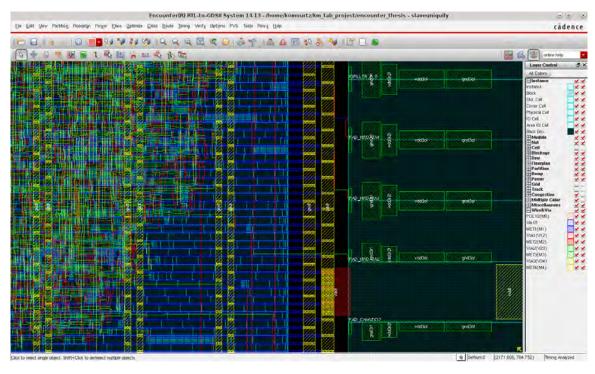

- Layout generation: System on Chip (SoC) Encounter (version 14.13) from Cadence completes the VLSI design flow. It performs floorplanning, power planning, placement, routing, clock tree synthesis, power analysis, DRC checks, in order to produce the final Graphic Data System (GDS)II file for the final tape-out of the circuit. The GDSII file is afterwards send to the foundry in order to begin the fabrication process of the System on Chip (SoC)

#### 2.5.1 Deal With Problems

All these tools described before are delivered with their huge documentation and manuals but they just describe each command of each tool with no direction for the design flow at least the minimum one that has to be followed. This problem applies to all EDA tools from three biggest vendors used in this thesis (Synopsys, Cadence and Mentor graphics) because they are expensive programs, mostly used in companies, and therefore, it is difficult to get information about how to solve specific problems. The first help came from the department because of the agreement it has with Europractice which legally provides the latest versions of EDA tools for academic use, as well as official tutorials, labs sessions and lectures from Cadence and Synopsys. After spending many hours of training sessions, there were still some issues i faced that many google searches helped me to solve. Summarizing the main help provided by:

- Synopsys tools: After checking the manuals, Solvenet can be used. It is the online resource for Synopsys tool support and downloads, that offers access to the Synopsys knowledge data base containing up-to-date product manual, webinars and labs.

- Cadence tools: Cadence provides lab and lecture sessions to universities that have an agreement through Europractice. iLs provides lab sessions that covers pretty much the whole design flow with Cadence EDA tools.

- For Mentor Graphics Modelsim some tutorials and scripts from google search were very useful and helped me understand in short time the tool.

- The rest of the problems solved from google search some other websites/forums that can be really helpful for clarifying some concepts. A small sample of them are: www.edacafe.com, www.edaboard.com, www.deepchip.com.

### Chapter 3

### ARM AMBA AHB

#### 3.1 General on ARM AMBA

The ARM [7] Advanced Microcontroller Bus Architecture (AMBA) is an open-standard, on-chip interconnect specification for the connection and management of functional blocks in System on Chip (SoC) designs. It facilitates development of multi-processor designs with large numbers of controllers and peripherals. Since its inception, the scope of AMBA has, despite its name, gone far beyond micro controller devices. Today, AMBA is widely used on a range of ASIC and SoC parts including applications processors used in modern portable mobile devices like smartphones. AMBA is a registered trademark of ARM Ltd. AMBA was introduced by ARM in 1996. The first AMBA buses were Advanced System Bus (ASB) and Advanced Peripheral Bus (APB). In its second version, AMBA 2, ARM added AMBA Advanced Highperformance Bus (AHB) that is a single clock-edge protocol. In 2003, ARM introduced the third generation, AMBA 3, including AXI to reach even higher performance interconnect and the Advanced Trace Bus (ATB) as part of the CoreSight on-chip debug and trace solution. In 2010 the AMBA 4 specifications were introduced starting with AMBA 4 AXI4, then in 2011 extending system wide coherency with AMBA 4 ACE. In 2013 the AMBA 5 Coherent Hub Interface (CHI) specification was introduced, with a re-designed high-speed transport layer and features designed to reduce congestion [1].

#### 3.1.1 Design Principles

The important aspect of a SoC is not only which components or blocks it houses, but also how they interconnect. AMBA is a solution for the blocks to interface with each other [?]. The objective of the AMBA specification is to:

- facilitate right-first-time development of embedded microcontroller products with one or more CPUs, GPUs or signal processors

- be technology independent, to allow reuse of IP cores, peripheral and system macrocells across diverse IC processes

- encourage modular system design to improve processor independence, and the development of reusable peripheral and system IP libraries

- minimize silicon infrastructure while supporting high performance and low power on-chip communication.

#### 3.1.2 AMBA Protocol Specifications

The AMBA specification defines an on-chip communications standard for designing high-performance embedded micro-controllers. It is supported by ARM Limited with wide cross-industry participation. A simple transaction on the AHB consists of an address phase and a subsequent data phase (without wait states: only two bus-cycles). Access to the target device is controlled through a MUX (non-tristate), thereby admitting bus-access to one bus-master at a time. AHB-lite protocol is a subset of AHB formally defined in the AMBA 3 specification. This design simplifies the design with a single master [1].

#### 3.2 ARM AMBA AHB-Lite

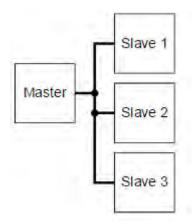

AHB-Lite [7] is a subset of the full AHB specification and is intended for use in designs where only a single bus master is used. This can either be a simple single master system, as show in Figure 3.1, or a multi-layer AHBsystem where there is only one AHB master per layer.

Figure 3.1: AHB-lite single master system

AHB-Lite simplifies the AHB specification by removing the protocol required for multiple bus masters, and includes:

- request and grant protocol to the arbiter

- SPLIT and RETRY responses from slaves.

Masters designed to the AHB-Lite interface specification can be significantly simpler in terms of interface design, compared to a full AHB master. AHB-Lite enables faster design and verification of these masters and the addition of a standard off-the-shelf bus mastering wrapper can be used to convert an AHB-Lite master for use in a full AHB system.

Any master that is already designed to the full AHB specification can be used in an AHB-Lite system with no modification. The majority of AHB slaves can be used interchangeably in either an AHB or AHB-Lite system. This is because AHB slaves that do not use either the SPLIT or RETRY response are automatically compatible with both the full AHB and the AHB-Lite specification. It is only existing AHB slaves that do use SPLIT and RETRY responses that require an additional standard off-the-shelf wrapper to be used in an AHB-Lite system. Any slave designed for use in an AHB-Lite system works in both a full AHB and an AHB-Lite design.

The AHB-Lite specification differs from the full AHB specification in the following ways:

- It is a single-master system. There is only one source of address, control, and write data, so no master-to-slave multiplexor is required.

- There is no arbitration. The AHB-Lite master always has control of the bus.

- There is no master HBUSREQ output. If such an output exists on a master, it is left unconnected.

- There is no master HGRANT input. If such an input exists on a master, it is tied HIGH.

- There is no SPLIT or RETRY slave responses. The AHB-Lite master deals only with a slave ERROR response.

- The AHB-Lite lock signal HMASTLOCK, compared with HLOCK for full AHB, and it has the same timing as the address bus and other control signals. If a master has an HLOCK output, it can be retimed to generate HMASTLOCK.

- The AHB-Lite lock signal, HMASTLOCK, must remain stable throughout a burst of transfers, in the same way that other control signals must remain constant throughout a burst.

Using the AHB-Lite interface makes the bus transfers generated by the AHB-Lite file reader easier to understand and easier to debug. Because the AHB-Lite is a single master protocol, an AHB-Lite master always has control of the bus. Unlike AHB, AHB-Lite has no request phase. Consequently, the AHB-Lite bus might be subject to wait states during the request phase of the AHB bus.

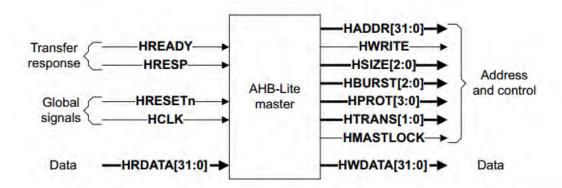

An AHB-Lite master has the same signal interface as a full AHB bus master, except that it does not support HBUSREQx and HGRANTx. The Lock functionality is still required because the master might be performing a transfer to a multi-port slave. The slave must be given an indication that no other transfer should occur to the slave when the master requires locked access. An AHB-Lite master is not required to support either the SPLIT or RETRY response and only the OKAY and ERROR responses are required, so the AHB-Lite master interface does not require the HRESP input.

The **advantage** of using the AHB-Lite protocol is that the bus master does not have to support the following cases:

- Losing ownership of the bus. The clock enable for the master can simply be derived from the HREADY signal on the bus.

- Early terminated bursts. There is no requirement for the master to rebuild a burst due to early termination, because the master always has access to the bus.

- SPLIT or RETRY transfer responses. There is no requirement for the master to retain the address of the last transfer to be able to restart a previous transfer.

A standard wrapper is available to **convert** an AHB-Lite master to make it a full AHB master. This wrapper adds support for the features described in AHB-Lite advantages. Because the AHB-Lite master has no bus request signal available, the wrapper generates this directly from the HTRANS signals.

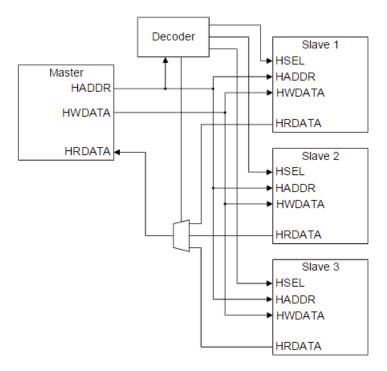

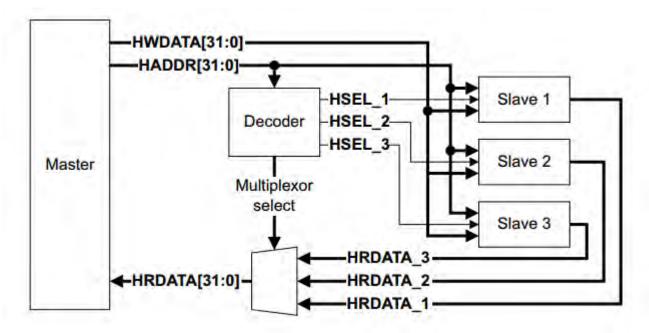

AHB slaves that do not use either the SPLIT or RETRY response can be used in either a full AHB or AHB-Lite system. Any slave that does use SPLIT or RETRY responses can be used in an AHB-Lite system by adding a standard wrapper. This wrapper provides the ability to store the previous transfer in the case of a SPLIT and RETRY response and restart the transfer when appropriate. This wrapper is very similar to that required to convert an AHB-Lite master for use in a full AHB system. For compatibility with Multi-layer AHB, it is required that all AHB-Lite slaves still retain support for early terminated bursts. Figure 3.2 shows a more detailed block diagram, including Decoder and slave-to-master multiplexor connections.

Figure 3.2: AHB-Lite components

#### 3.2.1 Introduction to AHB-Lite slave

#### 3.2.1.1 About the protocol

AMBA AHB [1]-Lite addresses the requirements of high-performance synthesizable designs. It is a bus interface that supports a single bus master and provides high-bandwidth operation.

AHB-Lite implements the features required for high-performance, high clock frequency systems including:

- burst transfers

- single-clock edge operation

- non-tristate implementation

- wide data bus configurations, 64, 128, 256, 512, and 1024 bits.

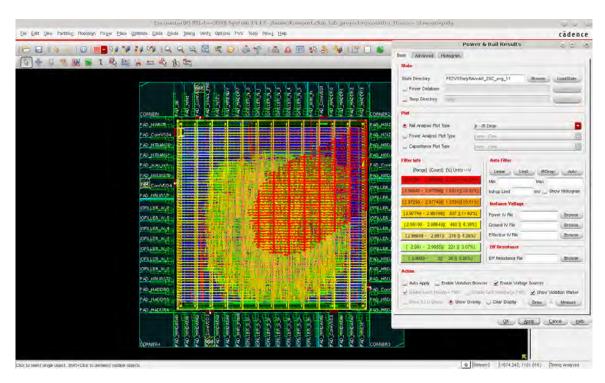

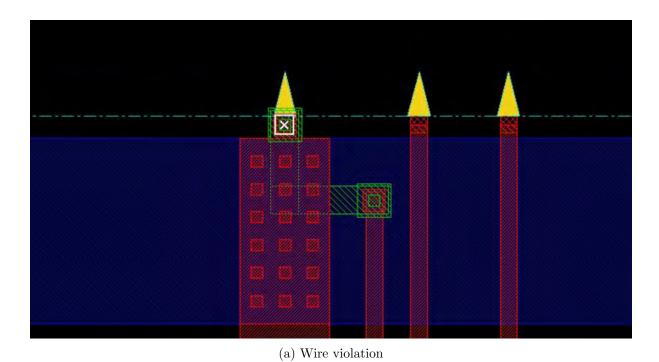

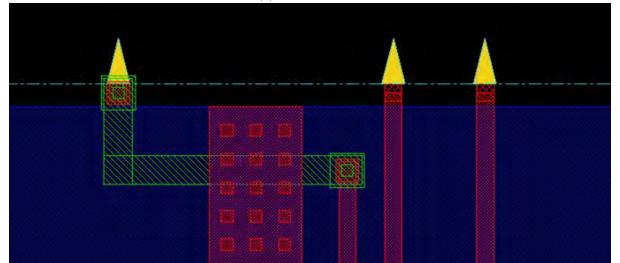

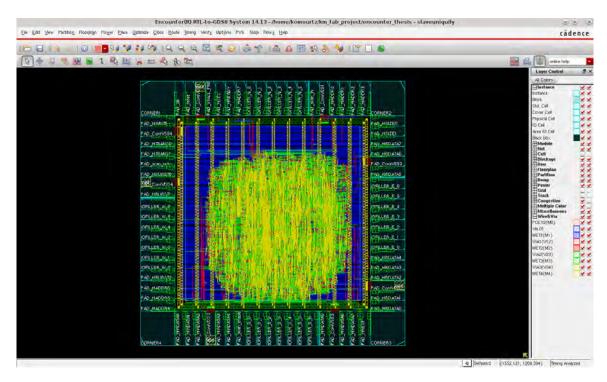

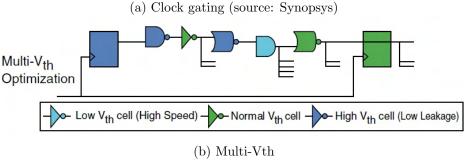

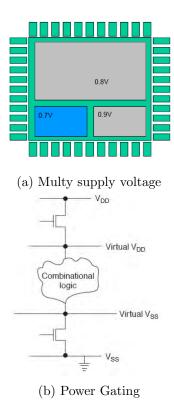

The most common AHB-Lite slaves are internal memory devices, external memory interfaces, and high bandwidth peripherals. Although low-bandwidth peripherals can be included as AHB-Lite slaves, for system performance reasons they typically reside on the AMBA Advanced Peripheral Bus (APB). Bridging between this higher level of bus and APB is done using a AHB-Lite slave, known as an APB bridge.