# ΠΑΝΕΠΙΣΤΗΜΙΟ ΘΕΣΣΑΛΙΑΣ

ΤΜΗΜΑ ΜΗΧΑΝΙΚΩΝ ΗΛΕΚΤΡΟΝΙΚΩΝ ΥΠΟΛΟΓΙΣΤΩΝ, ΤΗΛΕΠΙΚΟΙΝΩΝΙΩΝ & ΔΙΚΤΥΩΝ

# Σχεδίαση και υλοποίηση συστήματος client-server για τη συλλογή δεδομένων από πειραματικές διατάξεις επιταχυντών σωματιδίων του CERN

Επιβλέποντες:

επίκουρος καθηγητής

Χρήστος

ΑΝΤΩΝΟΠΟΥΛΟΣ

Συγγραφέας:

Αθανάσιος ΤΟΠΑΛΟΥΔΗΣ

Αναπληρωτής καθηγητής Νικόλαος ΜΠΕΛΛΑΣ

# **Acknowledgements**

By the end of this Thesis, I would like to thank the section leader of BE-BI-SW section at CERN and my personal supervisor Lars Jensen for the professional guidance and the confidence he showcased in my skill set during my studentship at CERN.

I would also like to thank the project leader of the fast beam intensity measurements (FBCT) for the LHC, Dr. David Belohrad for his guidance and excellent cooperation on the FBCT project for the LHC.

Furthermore, I would like to thank Michael Ludwig for the time he spent talking with me about the existing implementation of the FBCT servers in the LHC – system A and B – along with other general matters that helped me evolve personally.

In addition, I would like to thank my supervisors of this Thesis Christos D. Antonopoulos and Nikolaos Bellas for taking over the difficult part of the remote supervision of this Thesis, their excellent cooperation and their suggestions and corrections on this work.

Last but not least, I would like to thank my family, Theodoros, Chrysi, Christos and Alexandros who helped me form a solid ground to evolve my personality and Eirini who showed me how to do it.

# Περίληψη

Ένα από τα μεγαλύτερα ερευνητικά κέντρα στον τομέα της Φυσικής Υψηλών Ενεργειών (High Energy Physics) είναι ο Ευρωπαϊκός Οργανισμός Πυρηνικής Έρευνας (CERN) που έχει σαν κύριο σκοπό να μελετήσει τα θεμελιώδη στοιχεία της ύλης καθώς και της δυνάμεις που ασκούνται αναμεταξύ τους επιταχύνοντας σωματίδια μέσα από μια αλληλουχία επιταχυντών (accelerator complex) και οδηγώντας τα σε συγκρούσεις. Το CERN χρειάζεται διάφορα διαγνωστικά εργαλεία που μετράνε τα χαρακτηριστικά της δέσμης σωματιδίων προκειμένου να ελέγξει το σύμπλεγμα των επιταχυντών του και ένα από αυτά είναι το σύστημα μέτρησης Fast Beam Current Transformer (FBCT), το οποίο μετράει την ένταση της δέσμης.

Λόγω του ότι το υπάρχον υλικό (hardware) του FBCT συστήματος δεν έχει σχεδιαστεί με τον καλύτερο δυνατό τρόπο οπότε και δεν εκμεταλλεύεται όλες του τις δυνατότητες, χρειάστηκε να αλλάξει. Ως εκ τούτου, το υλικό ξανασχεδιάστηκε και απλοποιήθηκε ώστε να αυξήσει τις δυνατότητες του και να αποτελέσει τη βάση ενός ενιαίου συστήματος μέτρησης FBCT, το οποίο θα μπορεί να χρησιμοποιηθεί τόσο στις γραμμικές όσο και στις μη γραμμικές (δακτύλιοι) εγκαταστάσεις του συμπλέγματος των επιταχυντών του CERN. Ακολουθώντας αυτές τις αλλαγές, στη παρούσα διπλωματική προτείνουμε την υλοποίηση ενός client-server λογισμικού συστήματος που θα ελέγχει το FBCT σύστημα που είναι εγκατεστημένο στον Super Proton Synchrotron (SPS) επιταχυντή. Επιπλέον, μελετούμε το σχεδιασμό και την υλοποίηση ενός ενιαίου client-server λογισμικού συστήματος, το οποίο θα αντικαταστήσει τα υπάρχοντα στον Large Hadron Collider (LHC) επιταχυντή, καθώς και θα συνοδέψει μελλοντικές εγκαταστάσεις του FBCT συστήματος στο σύμπλεγμα των επιταχυντών του CERN.

## **Abstract**

One of the biggest research centers in the domain of High Energy Physics (HEP) is the European Organization for Nuclear Research or CERN Laboratory whose main goal is to accelerate particles through a sequence of accelerators – accelerator complex – and bring them into collision in order to study the fundamental elements of matter and the forces acting between them. For controlling the accelerator complex, CERN needs several diagnostic tools to provide information about the beam's attributes and one such system is the Fast Beam Current Transformer (FBCT) measuring system that provides beam intensity information.

The current hardware of the FBCT system is not well designed and thus the entire system is not benefiting from all of its capabilities and hence, a renovation is required. As a result, the hardware was redesigned and simplified in order to increase its capabilities and provide the base of a unified FBCT measuring system that could be installed in both kinds of the CERN's accelerator complex's parts, linear and nonlinear (rings). Following the above changes, this Thesis is proposing the implementation of an operational client-server software solution to control the FBCT installation in the Super Proton Synchrotron (SPS) accelerator, as well as studying the design and implementation of a unified client-server software scheme that can replace the operational ones in the Large Hadron Collider (LHC) and can accompany further installations of the FBCT measuring system, elsewhere in the CERN accelerator complex.

# **Table of Contents**

| T | able of Fig | gures                                                   | 7  |

|---|-------------|---------------------------------------------------------|----|

| T | able of Tal | oles                                                    | 9  |

| 1 | Introdu     | ction                                                   | 10 |

| 2 | Backgr      | ound                                                    | 12 |

|   | 2.1 Ge      | neral Background                                        | 12 |

|   | 2.1.1       | CERN                                                    | 12 |

|   | 2.1.2       | CERN's structure                                        | 12 |

|   | 2.1.3       | The CERN accelerator complex                            | 14 |

|   | 2.1.4       | Control Center                                          | 15 |

|   | 2.1.5       | Bunches                                                 | 15 |

|   | 2.1.6       | Beam Charge Measurements [8]                            | 15 |

|   | 2.1.7       | FESA Framework                                          | 16 |

|   | 2.2 Ha      | rdware Architecture                                     | 18 |

|   | 2.2.1       | Fast Beam Current Transformer (FBCT) measurement system | 18 |

|   | 2.2.2       | Firmware                                                | 20 |

|   | 2.2.3       | Driver Background                                       | 25 |

|   | 2.3 Th      | e FBCTs in the SPS                                      | 25 |

|   | 2.3.1       | Software Architecture                                   | 25 |

|   | 2.3.2       | Previous Implementation                                 | 26 |

|   | 2.4 Th      | e FBCTs in the LHC                                      | 28 |

|   | 2.4.1       | Software Architecture                                   | 28 |

|   | 2.4.2       | Existing Implementation                                 | 28 |

| 3 | Our Im      | plementation                                            | 30 |

|   | 3.1 His     | gh level                                                | 30 |

|   | 3.1.1       | Wrapper - Design                                        | 30 |

|   | 3.1.2       | Tester - Design                                         | 30 |

|   | 3.1.3       | DabInfo - Design                                        | 31 |

|   | 3.1.4       | SPS                                                     | 31 |

|   | 3.1.5       | LHC                                                     | 36 |

|   | 3.2 Te      | chnical Implementation                                  | 44 |

| 3.2.1        | Wrapper – Common Implementation | 44 |

|--------------|---------------------------------|----|

| 3.2.2        | Tester – Common Implementation. | 45 |

| 3.2.3        | DabInfo – Implementation        | 46 |

| 3.2.4        | SPS                             | 48 |

| 3.2.5        | LHC                             | 52 |

| 4 Results.   |                                 | 64 |

| 4.1 SPS      | S                               | 64 |

| 4.2 LH       | C                               | 65 |

| 5 Conclus    | ions and Future Work            | 67 |

| 5.1 Con      | nclusions                       | 67 |

| 5.1.1        | SPS                             | 67 |

| 5.1.2        | LHC                             | 67 |

| 5.2 Fut      | ure Work                        | 68 |

| Bibliography | y                               | 69 |

# **Table of Figures**

| Figure 2-1: CERN's Logo [22]                                                              | 12    |

|-------------------------------------------------------------------------------------------|-------|

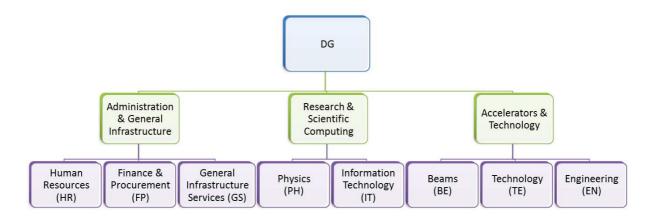

| Figure 2-2: CERN's structure (source: Laura Saulnier, TECH induction 2012)                | 13    |

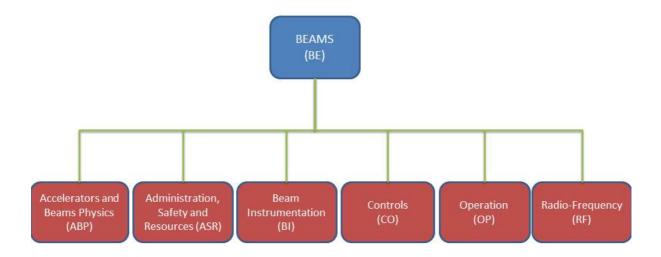

| Figure 2-3: Beams Department's Structure                                                  | 13    |

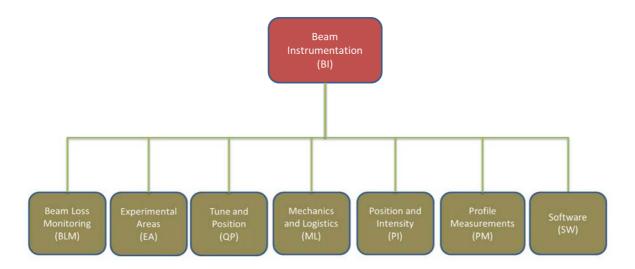

| Figure 2-4: Beam Instrumentation's structure                                              | 14    |

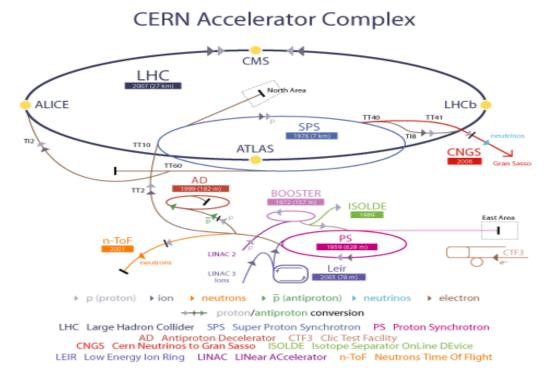

| Figure 2-5: CERN Accelerator Complex [6]                                                  | 14    |

| Figure 2-6: FESA's service supplies [9]                                                   | 17    |

| Figure 2-7: Block schematic of the FBCT measurement system [10]                           | 19    |

| Figure 2-8: SPS FBCT's VME64x crate – on the left with green lights is the FEC, on the    | right |

| of the FEC the DAB is installed and in the middle of the crate the BOBR is visible        | 20    |

| Figure 2-9: table's 2-3 Legend                                                            | 21    |

| Figure 2-10: FESA Framework Interface                                                     | 26    |

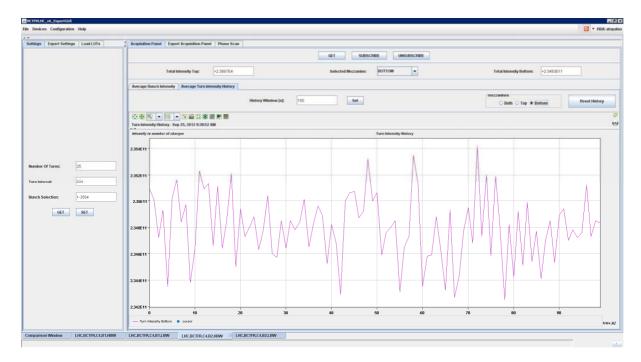

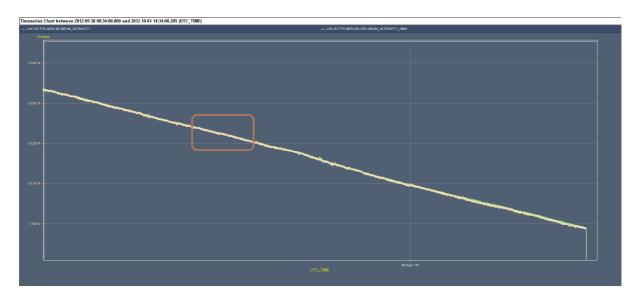

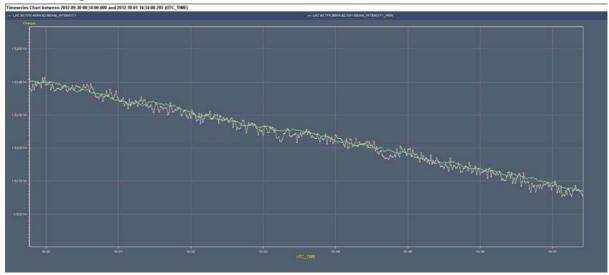

| Figure 2-11: Total Intensity History from beam1 of the LHC, System B                      | 29    |

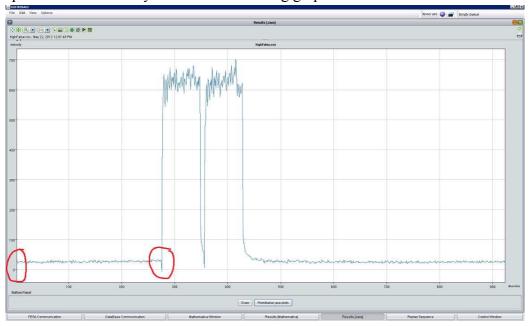

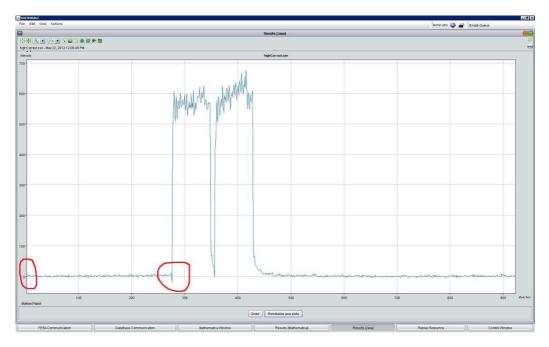

| Figure 3-1: ROSALI plot with error in BLR                                                 | 32    |

| Figure 3-2: ROSALI plot with correct BLR                                                  | 32    |

| Figure 3-3: Data flow between front-end server and GUI client                             | 34    |

| Figure 3-4: BFCTSR_ExpertGUI UML Class Diagram                                            | 35    |

| Figure 3-5: Acquisition schedule in respect with number of turn and turn interval         | 36    |

| Figure 3-6: Data Process Sequence                                                         | 36    |

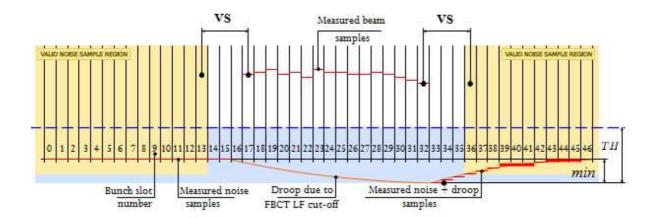

| Figure 3-7: An example of the BLR algorithm with VS=3. Only the yellow region is          |       |

| considered as noise [17]                                                                  | 38    |

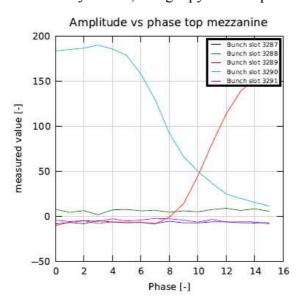

| Figure 3-8: phase scan                                                                    | 39    |

| Figure 3-9: BCTFRLHC_v6 expert GUI UML class diagram (without comparison window           | w)    |

|                                                                                           |       |

| Figure 3-10: Comparison Window UML class diagram (part of the BCTFRLHC_v6 expe            | rt    |

| GUI)                                                                                      | 43    |

| Figure 3-11: Bunch Selection Transformation from string to a set of hexadecimal           |       |

| Figure 3-12: Sign correction of the data in the code                                      |       |

| Figure 3-13: example code for ASCII parsing                                               |       |

| Figure 3-14: example run of the dabInfo in the lab                                        | 48    |

| Figure 3-15: Upper part of the BFCTSR_EpertGUI                                            |       |

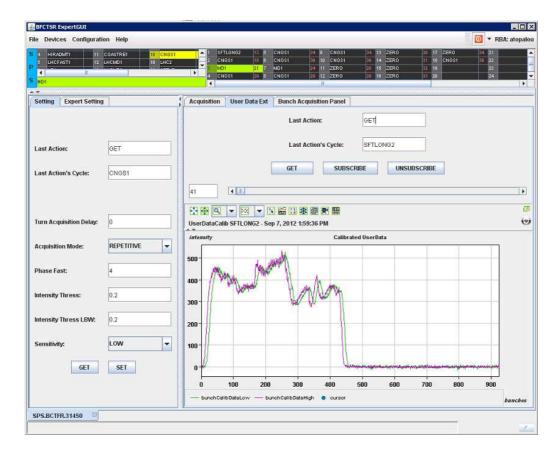

| Figure 3-16: BFCTSR Expert GUI – Acquisition Tab                                          |       |

| Figure 3-17: BFCTSR Expert GUI – UserData Tab                                             |       |

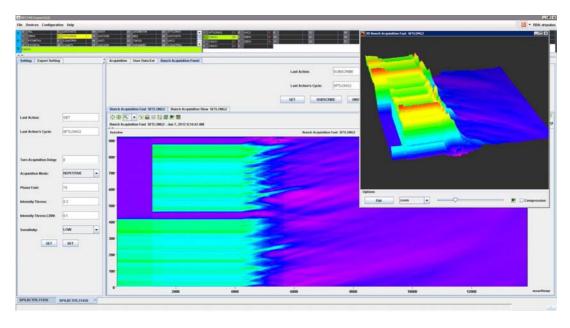

| Figure 3-18: BFCTSR Expert GUI – BunchAcquisition Tab                                     |       |

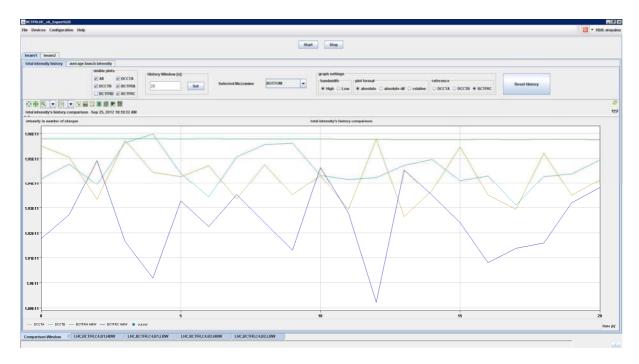

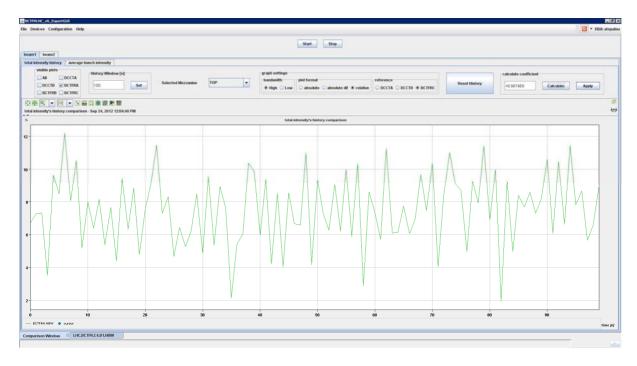

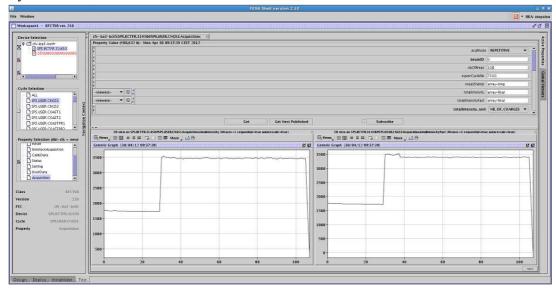

| Figure 3-19: Comparison Window - total intensity history for beam 1                       |       |

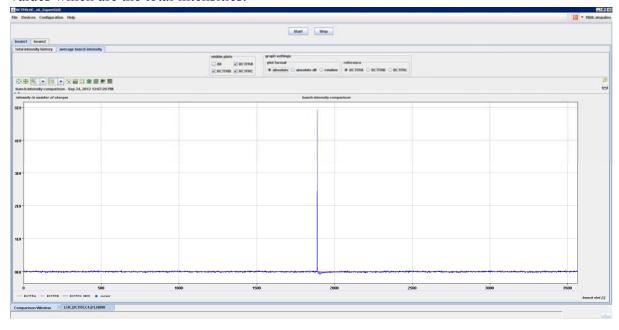

| Figure 3-20: Comparison Window - total intensity history - absolute difference - for beam | 1 1   |

|                                                                                           |       |

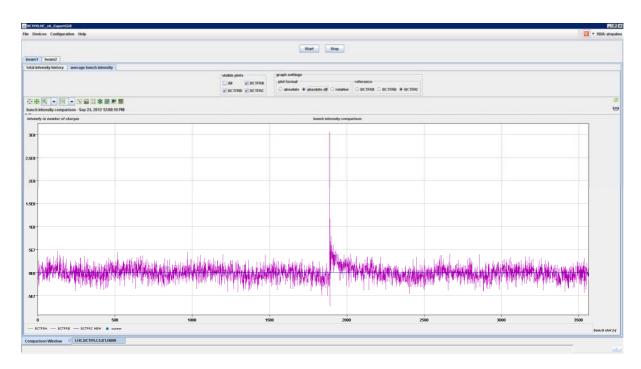

| Figure 3-21: Comparison Window - total intensity history - relative difference for beam 1 |       |

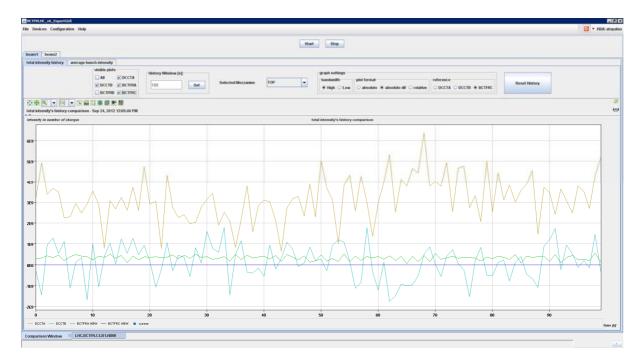

| Figure 3-22: Comparison Window - average bunch intensity for beam 1                       |       |

| Figure 3-23: Comparison Window - average bunch intensity - absolute difference for bear   | m 1   |

|                                                                                           | 59    |

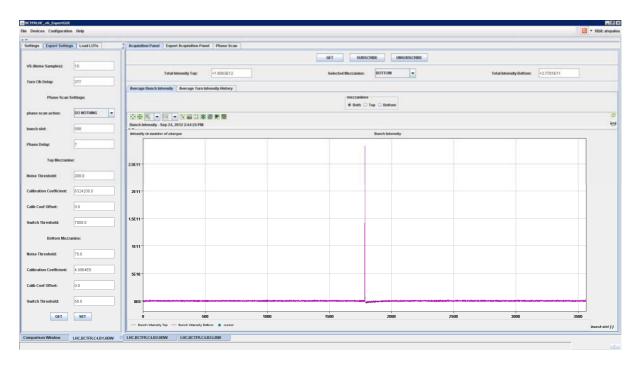

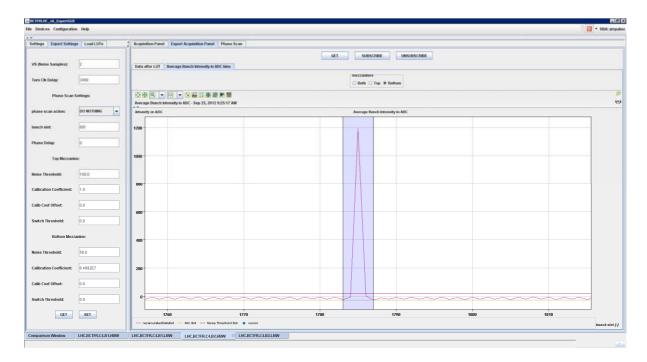

| Figure 3-24: BCTFRLHC_v6_ExpertGUI - Acquisition Panel / Average Bunch Intensity -       |     |

|------------------------------------------------------------------------------------------|-----|

| Expert Settings Panel                                                                    | 59  |

| Figure 3-25: BCTFRLHC_v6_ExpertGUI - Acquisition Panel / Average Turn Intensity          |     |

| History - Settings Panel                                                                 | 60  |

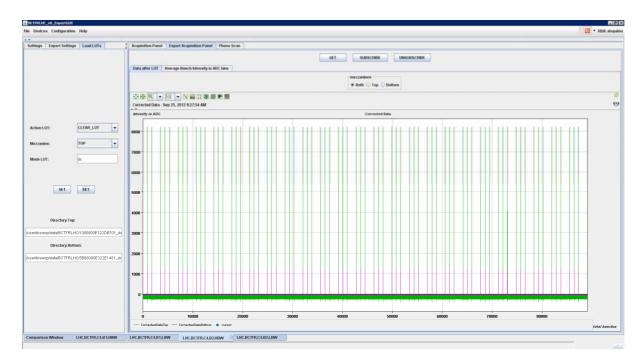

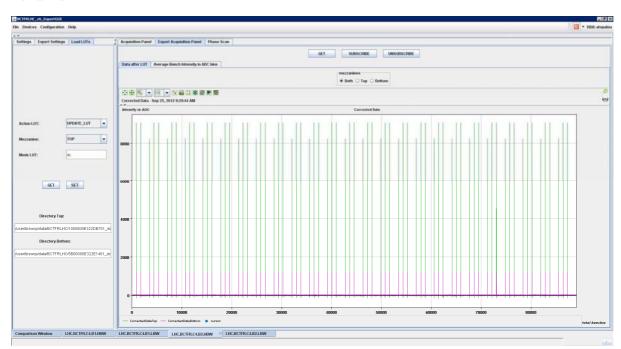

| Figure 3-26: BCTFRLHC_v6_ExpertGUI - Expert Acquisition Panel / Data after LUT -         |     |

| cleared LUT for top mezzanine                                                            | 61  |

| Figure 3-27: BCTFRLHC_v6_ExpertGUI - Expert Acquisition Panel / Data after LUT -         |     |

| updated LUT for top mezzanine                                                            | 61  |

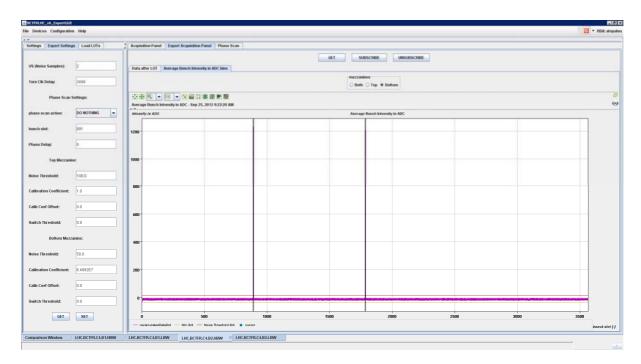

| Figure 3-28: BCTFRLHC_v6_Epxert Acquisition / Average Bunch Intensities in ADC bins      | 3 - |

| Expert Settings                                                                          | 62  |

| Figure 3-29: BCTFRLHC_v6_EpxertGUI - Zoom at the Expert Acquisition panel / Averag       | e   |

| Bunch Intensity in ADC bins tab                                                          | 62  |

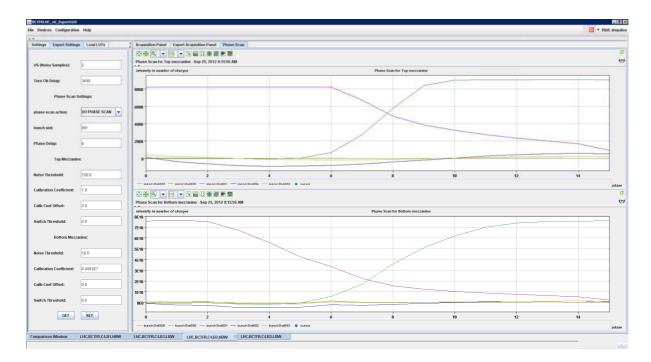

| Figure 3-30: BCTFRLHC_v6_ExpertGUI - Phase Scan                                          | 63  |

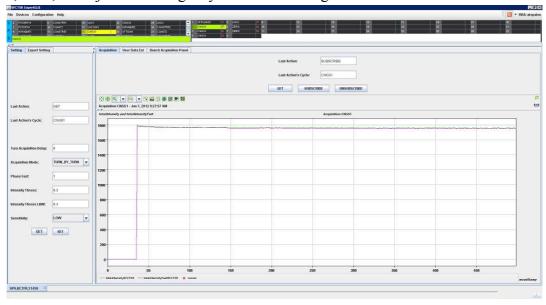

| Figure 4-1: Total Intensity Measurement with FBCT for the SPS, CNGS1 cycle,              |     |

| REPETETIVE mode with the previous version of the server                                  | 64  |

| Figure 4-2: Total Intensity Measurement with the FBCT in the SPS, CNGS1 cycle,           |     |

| TURN_BY_TURN mode                                                                        | 65  |

| Figure 4-3: Beam's 2 low gain total intensity comparison among system A, B and C in the  |     |

| LHC                                                                                      | 66  |

| Figure 4-4: Beam's 2 high gain total intensity comparison among system A, B and C in the |     |

| LHC                                                                                      | 66  |

# **Table of Tables**

| 2-1: FESA's data types [9]               | 17 |

|------------------------------------------|----|

| 2-2: FESA's data attributes [9]          | 17 |

| 2-3: Original firmware register map [15] |    |

| 2-4: New firmware register map [15]      | 23 |

#### 1 Introduction

The European Organization for Nuclear Research or CERN Laboratory is one of the biggest research centers in the domain of particle physics [1]. Its main activity is to accelerate ion or proton particles through its accelerator complex to their nominal energies and make them collide at one of the four collision points [7] in order to study the fundamental constituents of matter as well the forces acting between them.

The acceleration of the particles can only be achieved if the Radio Frequency (RF) field is correctly oriented with the accelerating cavity as they pass through it. Since this happens at well specified moments of the RF cycle, particles travel around the accelerator complex at well-defined bunches [7].

For an accelerator's control to be effective, numerous of diagnostic tools are needed to provide information about the beam's attributes [8]. Several measurement technics exist providing such information and thus making the control of the CERN accelerator complex effectively feasible. One such technic uses AC-coupled Fast Beam Current Transformers (FBCTs) at first stage to integrate the current of each individual bunch inside a synchronized integration window and provide continuously 40MHz bunch charges (in bits) [18], whereas, at second stage it implements data treatment in a Field-Programmable Gate Array (FPGA).

The latter uses its firmware to store and/or reload at any time the device configuration in order to implement four acquisition modes, single *capture* – which measures the intensity for the specified bunch slots over a specified number of turns, *turn sum* – which measures the total intensity of all bunch slots available (depending on the accelerator) over one turn, *slot sum* – which measures the total intensity for a given bunch slot over a specified number of turns – and *sum sum* – which measures a *turn sum* and then sums up these values using the *slot sum* measurement mode in order to produce one total intensity value [16].

In addition to the hardware part, there is also the software layer, which is responsible to control the device and to implement any data processing required that is not done by the firmware. Such data processing may be, averaging, data calibration – the transformation of the data from the measured values in number of bins to number of charges – and data publishing.

There is one FBCT system installed in the Super Proton Synchrotron (SPS) accelerator and three in the Large Hadron Collider (LHC) that provide both bunch-by-bunch and total turn-by-turn beam intensity information. The FBCTs in the SPS ring are widely being used at beam's injection time to observe the beam losses at that critical part of its journey as well at the machine protection beam dump occasions in order to analyze the causes of such dumps. As for the LHC ring, only two – system A and B – out of the three FBCT installations are currently operational and being used by a large number of clients interested in both measurement information – bunch-by-bunch and turn-by-turn.

The original FBCT firmware – FIMDAB – was designed and developed by several people using different technologies. As a result, several design errors worsens the mean time between failures – MTBF – of the entire measuring system, making the maintenance of the latter extremely difficult. Hence, in order to properly develop the FBCT system C, it was decided that a cleanup was necessary, moving all the data treatment from the hardware to the

software side. Therefore a new version of the firmware was designed and developed implementing only the *capture* acquisition mode leaving the software controlling the FBCT installations, responsible for all the data processing.

The whole idea behind this migration is to implement one data acquisition system – both hardware and software – that can be installed in the CERN accelerator complex and will be independent of the ring installed, which is not the current case, in order to make it generic and more easily maintainable.

As the new version of the firmware is already implemented, this Thesis is trying to describe the software solutions that need to accompany the hardware changes as well to propose new ideas as far as the data treatment is concerned. This document is divided in two large blocks: the first one introduces the theoretical and technical background whereas the second describes the proposed software implementation and outlines its performance evaluation.

In the first part, a brief introduction to the Organization and some fundamental knowledge concerning the FBCTs is given in chapter 2.1. In addition, in chapter 2.2 we describe the hardware architecture and in chapters 2.3 and 2.4, the existing software implementations for the FBCTs in the SPS and LHC accordingly.

In the second part, we provide our software design in chapter 3.1 and its technical implementation in chapter 3.2, along with the results of our proposals in chapter 4.

Finally, chapter 5 presents the conclusions of this work and directions for future work.

# 2 Background

In the previous section we discussed the need for the software design and implementation that controls the FBCT systems at CERN. In order to deploy our suggestion though, we need to analyze some basic ideas that are related to the FBCTs.

Hence, we begin with the general information about CERN and other key aspects needed for the rest of this document and we continue with the hardware architecture where all the details relative to the hardware are given and finish this section with the description of the software implementations for the SPS and LHC rings that used to be or are operational.

#### 2.1 General Background

In this section we analyze from scratch the basic information about CERN, its structure and accelerator complex because we are going to use this information for the deployment of our solution. Furthermore, we briefly describe the Control Center and how the particles travel through the rings. Subsequently, we analyze the need of measuring the beam's attributes as well the different ways to do it. Lastly, we introduce the design framework that was used for the existing and the previous software implementations as well as ours.

#### 2.1.1 **CERN**

The Conseil Européen pour la Recherche Nucléaire or European Organization for Nuclear Research, well known as CERN Laboratory is one of the biggest scientific research centers whose main area of research is particle physics - the study of the fundamental constituents of matter and the forces acting between them.

It was founded in 1954 as one of Europe's first joint ventures and now it counts 20 member states. It is placed on the Franco-Swiss border near Geneva and it uses the world's largest and most complex scientific instruments in order to accelerate the particles, almost to the speed of light, before cause them to collide and study the fundamental laws of Nature [1].

Figure 2-1: CERN's Logo [22]

#### 2.1.2 CERN's structure

The highest authority in the Organization is the CERN Council. It is formed by two representatives of each member state, one as his/her government's administration

representative and one to represent the national scientific interests. Each member state has one single vote and in most of the cases a simple majority is needed for a decision to be taken.

The Council is responsible for all the important decisions that have to do with scientific, administrative and technical matters. It is it that appoints the Director General who manages the CERN Laboratory through a structure of Departments which can be seen at fig.2-2. [2]

Figure 2-2: CERN's structure (source: Laura Saulnier, TECH induction 2012)

The author belongs to Beams Department (BE) [3] and hence a little more emphasis will be given to it and its structure. The BE is responsible for everything that has to do with the beam of particles and its control while circulating through the CERN accelerator complex (see chapter: 2.1.3). In order to do that it is divided into six groups as it is visible in fig. 2-3.

Figure 2-3: Beams Department's Structure

Each group is subdivided into sections. Again we will focus in our group, Beam Instrumentation (BI). The BI group is responsible to study, design, build and maintain all the instruments that allow the observation of the particle beams and its parameters which are important for its normal behavior in the CERN accelerator complex. [4] Its structure can be

seen in fig. 2-4. The author belongs to the Software section (SW), the section responsible for providing the software needed for developing, testing, diagnosing, maintaining and controlling all the instruments provided by the group. [5]

Figure 2-4: Beam Instrumentation's structure

#### 2.1.3 The CERN accelerator complex

The accelerator complex at CERN is a succession of linear and circular particle accelerators which can reach increasingly higher energies. Each accelerator receives the beam of particles from the previous in the complex chain, boost its speed and finally inject it to the next one in the sequence.

Figure 2-5: CERN Accelerator Complex [6]

There are two types of particles that travel through the CERN accelerator complex, protons and ions.

The protons are obtained by stripping orbiting electrons from hydrogen atoms. They are accelerated in the linear accelerator (LINAC2) before they are injected into the PS Booster. After Booster they are transferred to the Proton Synchrotron (PS) which is before Super Proton Synchrotron (SPS) in the complex sequence. Finally they are injected into the Large Hadron Collider (LHC) both in a clockwise and anticlockwise direction where they are accelerated to their nominal energy of 7 TeV before they start collide at one of the four collision points. [7]

The ions on the other hand, start from a source of vaporized lead and enter their own linear accelerator (LINAC3) before they are injected into the Low Energy Ion Ring (LEIR) from which they follow the same root as the protons to reach their maximum acceleration.

The complex also includes the Antiproton Decelerator (AD) which separates the antimatter particles while they are still in low energies, and the On-Line Isotope Mass Separator (ISOLDE) facility which is used as a unique source of low-energy beams of radioactive isotopes. The complex also feeds the CERN neutrinos to Grand Sasso (CNGS) project which creates and sends neutrino beams to Grand Sasso National Laboratory (LNGS) in Italy in order to detect the so called neutrino "oscillation", the transformation from one type of neutrino to another. Last but not least is the Compact Linear Collider (CLIC) study, an international project working on a machine to collide electrons and positrons (anti-electrons). [6]

#### 2.1.4 Control Center

The CERN Control Center (CCC) combines all the control rooms for the accelerator complex as well as the technical infrastructure under one roof. It consists of 39 operation stations organized in four different areas, the Large Hadron Collider, the Super Proton Synchrotron, the Proton Synchrotron complex and the technical infrastructure. [3]

#### 2.1.5 Bunches

The particles travel around the CERN accelerator complex in well-defined bunches. That is because they can only be accelerated if the Radio Frequency (RF) field has a correct orientation when they pass through an accelerating cavity and that happens at well specified moments during the RF cycle. [7]

Under nominal operation, each LHC's proton beam has 3564 bunches and SPS's 924, with each bunch containing about 10<sup>11</sup> protons.

## 2.1.6 Beam Charge Measurements [8]

An effective accelerator's control requires numerous types of diagnostic tools which provide information about the beam's attributes and they are commonly known as *beam diagnostics*. There are several measurement techniques which can be divided in two large categories, the intercepting and the non-intercepting measurements.

The first group, as it is revealed by its name, intercepts with the beam in order to achieve the measurements and thus cause the destruction of the beam or a significant loss of its energy, whereas the second group bases its measurements in the electric or magnetic field coupling of the beam to the measuring instrument.

The charge measurement, often called *beam intensity measurement*, is a process which integrates the actual measured quantity, the beam current, over a specific area of interest (ROI) and divides that integral, the beam charge as it is called, by the elementary charge to result in the number of particle beam's charges.

The beam intensity measurement is very useful to determine the intensity loss at injection, acceleration and extraction time or even the beam's lifetime while circulating in the accelerator. Furthermore, it enters the luminosity equation.

What is important in this kind of measurements is the device that couples to the beam and provides the approximation of the beam's current. There can be several different such devices. The most used of the intercepting DC devices are the Faraday cups. The non-intercepting AC devices are the electrostatic pickups, the Wall Current Monitors (WCMs) and the Fast Beam Current Transformers (FBCTs). The non-intercepting DC devices are the DC Current Transformers (DCCTs), the Superconducting QUantum Interference Devices (SQUIDs) and the Cryogenic Current Comparators (CCCs).

In this document we will focus only on the FBCTs, the devices that function in a bandwidth of few Hz up to GHz and on the contrary with all the other similar devices, can be absolutely calibrated. For more information see chapter 2.2 where the hardware is analyzed in more detail.

#### 2.1.7 FESA Framework

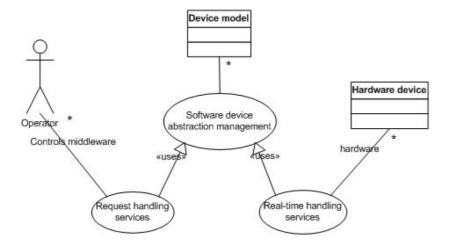

"The Front-End Software Architecture (FESA) is a comprehensive framework for designing, coding and maintaining LynxOS/Linux equipment-software that provides a stable functional abstraction of accelerator device." [9]

The Model of a FESA class is encoded as an XML Schema which enforces a specific grammar for the design of the class providing a partial yet generic solution for the equipment specialist. In this way and after the design of the class is well defined, the FESA user can generate a large part of the C++ code for his equipment saving a lot of time and effort. The FESA classes are identified by the combination of their name and version.

Figure 2-6: FESA's service supplies [9]

The Interface is a list of so-called Properties that defines the services that are available to the outside world and are remotely accessible by the clients of the FESA class, for example clients from the control room as well as middle-tier software layer. The Properties should be attached to a server action (request) which can be of type GET or SET and either default, meaning that the code for that actions is auto generated, or complex for which the equipment specialist must provide the code himself.

The Data, the Device-Data and Global-Data, are defined in such a way that provide at any given time, a concrete snapshot of the device state. The data can be of any standard type that can be supported from both C++ and Java, scalars or arrays up to two dimensions. There is also the possibility for the equipment specialist to define his own types, the persistency of the data or any multiplexing criterion for them.

| C++ Scalar type    | Array type  |

|--------------------|-------------|

| bool               | bool        |

| signed char (byte) | signed char |

| short              | char        |

| long               | short       |

| longlong           | long        |

| float              | long long   |

| double             | float       |

|                    | double      |

Table 2-1: FESA's data types [9]

| Persistency | Purpose                                 | Multiplexing | Purpose         |

|-------------|-----------------------------------------|--------------|-----------------|

| FINAL       | database constant                       | NONE         | not multiplexed |

| PERSISTENT  | periodic backup into persistent storage | USER         | cycle user      |

| VOLATILE    | RAM data                                | PARTICLE     | particle-type   |

|             |                                         | DESTINATION  | beam-target     |

Table 2-2: FESA's data attributes [9]

The basic work-units of a FESA class are called actions and can be either of real-time or server type. The real-time actions are triggered by events which are synchronized with the CERN's central timing system or by interrupts and they implement most of the equipment's functionality. They can also be attached to properties so that the latter can be notified at any update of the device's state. On the other hand, the server actions implement the client's request-handling and they are mostly responsible for the communication between the outside world and the device and that is exactly why they are attached most of the times with a property. For both real-time and server actions the equipment specialist must provide the C++ code himself, except for the default GET/SET server actions.

Once one has finished with his FESA design, should declare all the instances his class would have. This is a very important part of the design procedure since lot of work and duplicated code can be avoided. One instance means one module with its own initial values. All the instances (the modules the device can handle) are accessible inside the FESA class by iterating the *deviceCollection*, an array accessible everywhere in the class.

A FESA class, to which we will refer as 'server' from now on, is organized after its generation, in five files as follows: COMMON, GENERATED CODE, REALTIME, SERVER and TEST.

The REALTIME and the SERVER files are used to store and distinguish the actions based on their type as described above.

The GENERATED CODE file holds all the declaration of the fields that describe the device. Furthermore, all the generated code for the simple GET/SET actions is stored here.

The COMMON file is used to store any custom made class that could be used by both real-time and server actions.

Last but not least is the TEST file. In there, some diagnostic tests are stored as well as the executable files that would start the server. There may be more than one executable file depending on how many instances of the server there are, which depend on how many different places in the Ring, the device is placed.

#### 2.2 Hardware Architecture

After giving the general information that is going to be needed in next sections, we are describing the hardware installation for the FBCTs. The latter consists of a detailed description of the ring installation as well as the one on the surface. Furthermore, we analyze the firmware – original and newer version – along with the driver needed to access it since they are widely used by the software and lots of the changes imposed to it derives from the changes of the firmware.

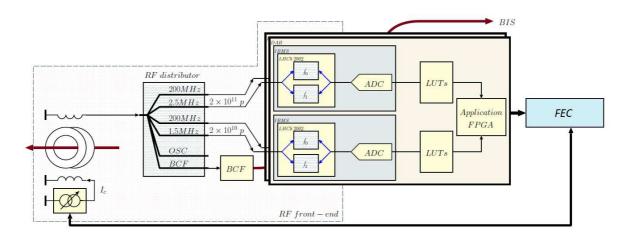

# 2.2.1 Fast Beam Current Transformer (FBCT) measurement system

The figure 2-7 depicts a simplified block schematic of the FBCT measurement system which consists of a Bergoz type transformer with a bandwidth from 400Hz to 1.2GHz (on the left). This transformer is followed by an RF front-end which consists of an analogue integrator, a Beam Circulating Flag (BCF) detector which detects the presence of the beam in

the ring and an RF distributor which is responsible to split the analog signal into two dynamic ranges, high and low gain and each dynamic range into two bandwidths, High (HBW) and Low (LBW). Finally there is a 14bit acquisition system that digitizes and process the signal. [10]

Figure 2-7: Block schematic of the FBCT measurement system [10]

The latter consists of aDigital Acquisition Boards (DABs), a VME64x standard board developed by TRIUMF (Canada) for the LHC orbit and trajectory acquisition system [11]. It is equipped with two Individual Bunch Measurement System (IBMS) mezzanine cards [12]. Each mezzanine card uses a 40MHz integrator ASIC developed for the LHC-b preshower detector by the Laboratoire de Physique Corpusculaire, UniversitéBlaise Pascal, Clermont-Ferrand [13], in order to integrate the incoming signal before pass it to the DAB that digitizes and process it to produce bunch-by-bunch intensity values. All the logic of the DAB control is implemented in a large FPGA that can be reprogrammed at any time and its firmware is being discussed at chapter 2.2.2.

These DAB cards are installed on a VME64x crate along with the Beam Synchronous Timing Receiver Interface for the Beam Observation System (BOBR) – another VME format card that provides all the timing signals required to synchronize the different beam instrumentation systems [19]. What is more, all the cards installed in the VME64x crate are controlled by the Crate Central Processing Unit (CPU) – Front-End Computer (FEC) – an Intel® Core<sup>TM</sup> 2 Duo CPU board with 1.5GHz clock frequency, 4MB cache and no hard disc [20] that runs Scientific Linux CERN SLC release 5.7 (Boron) [21] and boots via network.

The following figure 2-8 depicts the VME64x crate installation for the SPS FBCT. The FEC is visible on the left of the crate with the green lights, whereas the DAB is just on the right of it and lastly, the BOBR in the middle of the crate.

Figure 2-8: SPS FBCT's VME64x crate – on the left with green lights is the FEC, on the right of the FEC the DAB is installed and in the middle of the crate the BOBR is visible

As far as the SPS is concerned there is only a single DAB connected to the SPS type front-end amplifier. The former uses an external signal to switch between high and low gain measurements which is provided by the *sensitivity output* of each IBMS mezzanine.

In the LHC, things are different. There are two DABs per a measurement system used, one for HBW and one for LBW measurements. Each DAB provides two dynamic range measurements using its different IBMS mezzanine and more specifically high gain (top mezzanine) and low gain (bottom mezzanine) measurements.

There are three such systems in the LHC, system A, B and C of which only A and B are operational while system C is now being developed with different technologies and with a different approach in the process of the data. Further discussion about this system will follow in chapter 3.

The FBCT measurement system is calibrated by a pulse of 25µs. The amplitude of this pulse differs from SPS – 128mA – and LHC which can be programmed. For the latter case though, the currently used system doesn't use direct calibration due to the fact that the LHC toroid exhibit beam position dependency and this can affect the transfer ratio between *beam* – *measurement turn* and *calibration turn* – *measurement turn*. Instead an indirect calibration is achieved by using DC current transformers (DCCTs) installed in the LHC [17].

#### 2.2.2 Firmware

The Stratix FPGA stores the device configuration during operation at volatile SRAM cells, which must be reconfigured each time the device powers up. This is accomplished by its firmware (FIMDAB), which is stored as a raw binary file (RBF) in the EPM 3256 Complex Programmable Logic Device (CPLD). Software start-up scripts handle the FPGA start-up process and hence the FPGA is left un-programmed after power up until the software

layer is loaded. After the initial power-up process is complete, new configuration data can also be loaded at any time. [14]

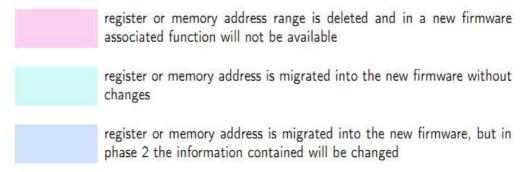

The original FBCTR firmware, used in system A and B was developed by several people using different technologies. As a result the mean time between failures (MTBF) of the entire system is worsened by several design errors. Hence, in order to properly develop FBCTR system C, it was decided that a cleanup was necessary. The new firmware was also used for the FBCTR in SPS. The firmware registers migration is summarized in table 2-3, which uses the following colors to describe the state of the registers after the completion of the migration [15].

Figure 2-9: table's 2-3 Legend

| Address Hex   Size   Type   RW |         | RW | Designation |                                                    |  |

|--------------------------------|---------|----|-------------|----------------------------------------------------|--|

| 0×000000                       | 512 KiB | LW | R           | Top mezzanine Capture Data                         |  |

| 0×200000                       | 512 KiB | LW | R           | Bottom mezzanine capture data                      |  |

| 0×400000                       | 512 KiB | LW | R           | PM Status -> Reserved memory location              |  |

| 0×600000                       | 1       | LW | R           | Firmware Compilation Date                          |  |

| 0x600005                       | 1       | В  | W           | Global command register                            |  |

| 0×600006                       | 1       | W  | R           | Global status register                             |  |

| 0x600010                       | 1       | В  | RW          | VME Interrupt Status                               |  |

| 0×600011                       | 1       | В  | RW          | VME Interrupt Enable register                      |  |

| 0×600014                       | 1       | LW | RW          | Debug register                                     |  |

| 0x600020                       | 1       | В  | RW          | Clock source selection and Status                  |  |

| 0×600021                       | 1       | В  | RW          | Phase Delay Register                               |  |

| 0x600022                       | 1       | W  | RW          | Turn Clock Delay Register                          |  |

| 0×600024                       | 1       | В  | RW          | Top/Bottom mezzanine ADC filter selection          |  |

| 0×600030                       | 1       | LW | R           | Global turn count register                         |  |

| 0×600034                       | 1       | W  | RW          | Capture turn interval                              |  |

| 0x600036                       | 1       | W  | RW          | Capture turn number                                |  |

| 0×600038                       | 1       | LW | RW          | Summing turn number                                |  |

| 0x600040                       | 1       | LW | R           | Last Capture Start TurnCount                       |  |

| 0x600044                       | 1       | LW | R           | Last Sum A Start TurnCount                         |  |

| 0x600048                       | 1       | LW | R           | Last Sum B Start TurnCount                         |  |

| 0×60004C                       | 1       | LW | R           | Last PM Start TurnCount                            |  |

| 0×600050                       | 1       | LW | R           | Last PM freeze TurnCount                           |  |

| 0x600054                       | 1       | LW | R           | Top/bottom mezzanine PM acquisition pointer        |  |

| 0×600060                       | 1       | W  | RW          | P0 Capture Start Selection Mask                    |  |

| 0×600062                       | 1       | W  | RW          | P0 Summing A Start Selection Mask                  |  |

| 0×600064                       | 1       | W  | RW          | P0 Summing B Start Selection Mask                  |  |

| 0×600066                       | 1       | W  | RW          | P0 PM Start Selection Mask                         |  |

| 0x600068                       | 1       | W  | RW          | P0 PM Freeze Selection Mask                        |  |

| 0x60006A                       | 1       | W  | RW          | P0 Global Turn Count Reset Selection Mask          |  |

| 0x60006C                       | 1       | В  | RW          | Front panel selection register                     |  |

| 0×600070                       | 1       | W  | R           | Stratix temperature register                       |  |

| 0×600070                       | 1       | W  | R           | Module power supplies status                       |  |

| 0×600100                       | 2       | LW | R           | DAB serial number                                  |  |

| 0x600100                       | 2       | LW | R           | Top mezzanine serial number                        |  |

|                                |         |    | 7,657       |                                                    |  |

| 0x600110                       | 2       | LW | R           | Bottom mezzanine serial number                     |  |

| 0x600118                       | 2       | LW | R           | DIDT mezzanine serial number                       |  |

| 0x600200                       | 1       | W  | R           | Raw Data from top mezzanine                        |  |

| 0x600202                       | 1       | W  | R           | Raw Data from bottom mezzanine                     |  |

| 0×600300                       | 1       | LW | R           | Base line calculation results for top mezzanine    |  |

| 0×600304                       | 1       | LW | R           | Base line calculation results for bottom mezzanine |  |

| 0x600310                       | 1       | W  | RW          | Top mezzanine validity level                       |  |

| 0×600312                       | 1       | W  | RW          | Bottom mezzanine validity level                    |  |

| 0x600314                       | 1       | W  | RW          | Top mezzanine FIR threshold                        |  |

| 0x600316                       | 1       | W  | RW          | Bottom mezzanine FIR threshold                     |  |

| 0x610000                       | 16 KiB  | W  | RW          | Top mezzanine LUT for INT0                         |  |

| 0x618000                       | 16 KiB  | W  | RW          | Top mezzanine LUT for INT1                         |  |

| 0x620000                       | 16 KiB  | W  | RW          | Bottom mezzanine LUT for INT0                      |  |

| 0x628000                       | 16 KiB  | W  | RW          | Bottom mezzanine LUT for INT1                      |  |

| 0x630000                       | 7128    | LW | R           | Buffer A of top mezzanine                          |  |

| 0x638000                       | 2 KiB   | LW | R           | Buffer A of top mezzanine turn sum                 |  |

Table 2-3: Original firmware register map [15]

| Address Hex | Size  | Type | RW | Designation                                   |

|-------------|-------|------|----|-----------------------------------------------|

| 0x63C000    | 4     | LW   | R  | Sum of Sum buffer A of top mezzanine          |

| 0×640000    | 7128  | LW   | R  | Buffer A of bottom mezzanine                  |

| 0×648000    | 2 KiB | LW   | R  | Buffer A of bottom mezzanine                  |

| 0x64C000    | 4     | LW   | R  | Sum of Sum buffer A of bottom mezzanine       |

| 0×650000    | 7128  | LW   | R  | Buffer B of top mezzanine                     |

| 0×658000    | 2 KiB | LW   | R  | Buffer B of top mezzanine                     |

| 0x65C000    | 4     | LW   | R  | Sum of Sum buffer B of top mezzanine          |

| 0×660000    | 7128  | LW   | R  | Buffer B of bottom mezzanine                  |

| 0×668000    | 2 KiB | LW   | R  | Buffer B of bottom mezzanine                  |

| 0x66C000    | 4     | LW   | R  | Sum of Sum buffer B of bottom mezzanine       |

| 0×670000    | 2 KiB | LW   | R  | Turn summing of top mezzanine channel data    |

| 0×672000    | 2 KiB | LW   | R  | Turn summing of bottom mezzanine channel data |

| 0×674000    | 1     | LW   | R  | Firmware revision                             |

| 0×680000    | 1     | LW   | RW | BCF threshold register                        |

| 0×680004    | 1     | LW   | R  | BCF INT0 min/max register                     |

| 0×680008    | 1     | LW   | R  | BCF INT1 min/max register                     |

| 0×68000C    | 1     | LW   | R  | Extended status register                      |

| 0x680010    | 1     | LW   | R  | BCF difference register                       |

| 0×680014    | 1     | LW   | R  | Turn Clock Watchdog                           |

**Table 2-3: Continue from previous page**

Following the table 2-3, table 2-4 summarize the minimum set of registers for the new proposed memory map. The table is organized in three categories. First group consists of the registers read directly from the DAB external static memories. Second one groups all the registers that are not specific to capture mode and third contains registers only specific to capture mode. The latter two are separated by an address space, which makes a potential insertion of new registers simple. All registers are 4-byte aligned and accessed by A32D32 transfer. Lastly, for non-single transfer registers, block transfer can be used improving the latency added when transferring huge amount of data. [15]**Error! Bookmark not defined.**

| Address Hex   Size   Type   RW |                                | Name | Designation |                 |                                       |  |  |  |  |  |

|--------------------------------|--------------------------------|------|-------------|-----------------|---------------------------------------|--|--|--|--|--|

|                                | External sampled data memories |      |             |                 |                                       |  |  |  |  |  |

| 0×000000                       | 512 KiB                        | LW   | R           | CTopData        | Top mezzanine Capture Data            |  |  |  |  |  |

| 0×200000                       | 512 KiB                        | LW   | R           | CBottomData     | Bottom mezzanine capture data         |  |  |  |  |  |

| 0×400000                       | 512 KiB                        | LW   | R           | ExtendedData    | PM Status -> Reserved memory location |  |  |  |  |  |

|                                |                                |      |             | Global register | S                                     |  |  |  |  |  |

| 0×600000                       | 1                              | LW   | R           | FWDate          | Firmware Compilation Date             |  |  |  |  |  |

| 0×600004                       | 1                              | LW   | R           | FWRevision      | Firmware revision                     |  |  |  |  |  |

| 0x600008                       | 1                              | LW   | R           | TCIkWd          | Turn Clock Watchdog                   |  |  |  |  |  |

| 0×60000c                       | 2                              | LW   | R           | SNDAB           | DAB serial number                     |  |  |  |  |  |

| 0×600014                       | 2                              | LW   | R           | SNTop           | Top mezzanine serial number           |  |  |  |  |  |

| 0x60001c                       | 2                              | LW   | R           | SNBottom        | Bottom mezzanine serial number        |  |  |  |  |  |

| 0×600024                       | 2                              | LW   | R           | SNPIM           | PIM mezzanine serial number           |  |  |  |  |  |

| 0x60002c                       | 1                              | LW   | RW          | Debug           | Debug register                        |  |  |  |  |  |

| 0×600030                       | 1                              | LW   | RW          | FPMux           | Front panel selection register        |  |  |  |  |  |

Table 2-4: New firmware register map [15]

| Address Hex | Size       | Type | RW | Name                | Designation                              |

|-------------|------------|------|----|---------------------|------------------------------------------|

| 0×600034    | 1          | LW   | RW | Command             | Extended/Global command/status register  |

| 0x600038    | 1          | LW   | RW | IRQ                 | VME Interrupt enable/status register     |

| 0×60003c    | 1          | LW   | R  | GlobalTurnCount     | Global turn count register               |

| 0×600040    | 1          | LW   | RW | TClkDelay           | Turn Clock Delay Register                |

| 0×600044    | 4          | LW   | R  | FWCodename          | Firmware codename ASCII string           |

| 0x600054    | 1          | LW   | R  | PSStatus            | Power supplies status                    |

| 0×600100    | 128        | LW   | R  | DebugMem            | General purpose debugging memory         |

|             | \ <u>\</u> |      | C  | apture related regi | sters                                    |

| 0×610000    | 1          | LW   | RW | ClkPhase            | Phase Delay Register                     |

| 0×610004    | 1          | LW   | RW | CTurnInterval       | Capture turn interval                    |

| 0×610008    | 1          | LW   | RW | CTurnNumber         | Capture turn number                      |

| 0×61000c    | 1          | LW   | R  | CStartingTurn       | Last Capture Start TurnCount             |

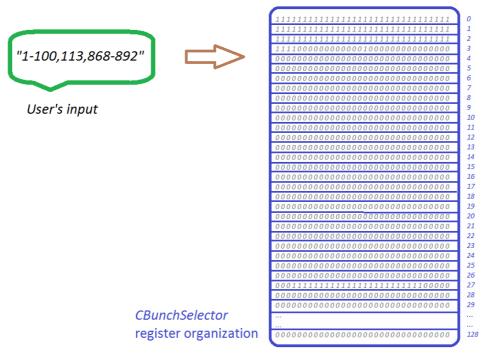

| 0×610200    | 128        | LW   | RW | CBunchSelector      | Bunch selection memory                   |

| 0×610400    | 1          | LW   | R  | CRollPointer        | Rolling pointer                          |

| 0×610404    | 1          | LW   | R  | CCurrentBSlots      | Number of currently selected bunch slots |

Table 2-4: Continue from previous page

From the latter table, 6 major changes at the registers can be pointed out.

Firstly is the capture data organization. Using 32-bit storage, two 14-bit ADC samples can be stored per entry. Unfortunately this is not enough since additional information is needed to be stored with the stream, information about what integrator was used for acquiring the sample – the most significant bit of the sample (31 and 15) reveals the appropriate integrator (0 or 1) –, about whether the sample was saturated – bits 30 and 14 – and finally, about where the turn clock starts. Since there is no space left to store the latter information with the stream, a convention had to be declared: the turn always starts at the memory start address – 0x000000 for top mezzanine and 0x200000 for bottom. Hence, next turn can be easily calculated as following: <start\_address> + (<number\_of\_bunches> / 2).

Such memory organization decreases the amount of external memories read from three to two, since the information stored in mezzanine three are now coded with the samples. It also increases the number of samples per mezzanine by factor of two, enabling at the same time the use of fast block transfer of the data, from the external memories to the CPU.

Furthermore, changes in register bit positions should also borne in mind. The original information of the Turn Clock Delay register is migrated from address 0x600022 to 0x600040, bits 12...0, whereas the information of the Phase Delay register from address 0x600021 to 0x610000, bits 7...0. As for the Front Panel Selection register, information about MUXA originally located at bits 7...4 is extended into bits 31...16, whereas information about MUXB, originally at bits location 3...0 is extended into bits 15...0. As far as the IRQ register is concerned, it behaves as Interrupt Enable register when written and returns the Interrupt Status register when read.

Last but not least is the *Command* register which combines the original locations at 0x600005, 0x600006 and 0x68000c and acts as *Command* register when written, keeping all the original properties and as *Status* register when read. The meaning of all bits read is

changed though, due to the differences between the two versions of the firmware and for a full description of this meaning refer to full technical documentation [14]**Error! Bookmark not defined.**

#### 2.2.3 Driver Background

There are more than one ways to access the device's register and hence, we had to find which one is more suitable for us. The most common way is to use the *ioctl* module-specific library that comes with the driver and is automatically generated from the description of the module in the CO Data Base. This is a simple library that uses only one method to access the hardware, IOCTL. This library is good for individual values or short amount of data, since it is already high leveled and not that slow.

If the performance is one of the main characteristics of the project, one should consider another library that comes with the same auto generated driver and that is *dal* (Driver Access Library). The *dal* library has three ways of accessing the hardware and these are IOCTL, same as before, IOMMAP and IODMA. Now as for the last two, the IOMMAP method uses the CPU to access the hardware while the IODMA does this directly.

We have been experimenting with these three ways, only to find out that there is a significant difference between IODMA and the other two. Generally we could summarize our conclusions as this: faster: IODMA < IOMMAP < IOCTL. As we saw in chapter 2.2.2, only three of our registers are a considerable amount of data (512.00 KiB) and from those, only two are being currently used. All the others are either single valued or short amount of arrays. Thus we've decided to use the *ioctl* library for all the registers but the two mezzanines for which we've used the *dal* library with the IODMA method.

#### 2.3 The FBCTs in the SPS

As described in the previous sections there is only one FBCT system installed in the SPS and this consists of only one DAB card on the VME crate, which used to operate with the original version of the device's firmware (FIMDAB).

In the following sections, we will describe how the server used to be organized and which were its basic functionalities that made it operational.

#### 2.3.1 Software Architecture

The server was designed 1 to operate a full acquisition (1-924 bunches) for every different active cycle – approximate cycle's length is 20sec. Different sequence of real-time actions used to accomplish that by preparing the device, starting the acquisition, reading back the acquired data, processing them, storing them temporarily, starting the acquisition again and repeating this sequence until the cycle was over.

All these functionalities were implemented in different real-time actions, rtPrepare, rtStart, endCapture and rtStop whose technical specifications will be discussed in the following chapter 2.3.2. The scheduling of these actions was the key for the proper operation of the server.

\_

<sup>&</sup>lt;sup>1</sup> The server was created by Lars Jensen

A warning of the beam's injection was used as an event that comes 20 msec before every different cycle's injection. This event was being used by the rtPrepare to set the appropriate settings to the device as well as calibrate it, before the acquisition could start.

Another event, specifying the beam's injection – cycle's beginning, was being used by the rtStart to initially start the acquisition. After that, an event coming every 40msec, was being used by the endCapture to read back the acquired data, process and store them in temporary buffers and finally start the acquisition again. This procedure was being repeated as many times as it could fit in every cycle's lifetime.

Lastly, an event specifying the cycle's end was being used by the rtStop to gather all data from the temporary buffers and store them in the shared memory of the server so that it could be fetched to the users.

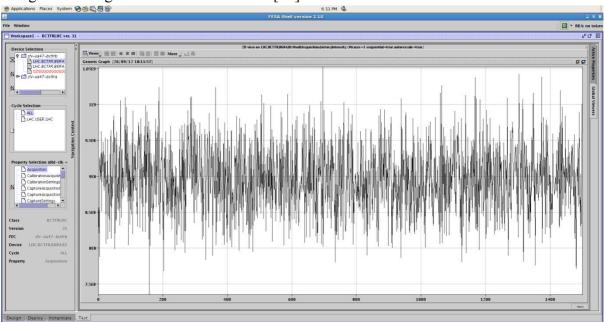

Figure 2-10: FESA Framework Interface

The FESA properties that used to interface the server were Setting – where the user could enter the settings relative to the acquisition, Expert Setting – where the user could specify the settings relative to the calibration of the device, Acquisition – where the user could see the desired data after all steps of their process, User Data – where the user could see the intermediate steps of the processed data and Calib Data – where the user could see and set the calibration factors of the data, either on his own or with respect to the calculated ones by rtPrepare. No external application interface (such as Expert GUI) was used for visualizing the above properties, and thus the FESA interface was used for that purpose as it can be seen in figure 2-10.

#### 2.3.2 Previous Implementation

The previous implementation of the server used to access the device directly from its classes using the IOCTL library.

More specifically the rtPrepare action used to set the full bunch range (bunches 1-924) to the device as well as the number of turns for the acquisition which was always 1. After

that, it would start an acquisition along with a calibration pulse in order to calibrate the device. This is achievable due to the fact that the rtPrepare operates when there is no beam. In this way and by firing a calibration pulse, whose current is known in advance, the appropriate calibration factors could be specified to take away all the additional noise that is being added to the data by the electronic equipment. Following the calibration, the rtPrepare would reset all the intermediate temporary buffers that were going to be used by the endCapture.

For the rtStart action, things used to be much simpler, since its only responsibility was to start a normal acquisition which means without the calibration pulse.

Furthermore, the endCapture action was the most critical one as far as the time constrains is concerned. In this action, the data would be fetched from the device and be processed before been stored to the temporary buffers. By processing the data, we mean to restore their base line as well as apply the calibration factors that were calculated before by the rtPrepare. The base line restoration is by far the most difficult stage of their process since its main goal is to take away the beam's position dependency with the measuring device, restoring the level of the acquired noise to 0 in the y (intensity) axe, and this procedure is non-trivial at all.

The existing implementation was using the Magic Imperial algorithm to restore the data's base line. This algorithm was based on the statistics from previous operational experience and its basic idea was the following:

- Iterate the acquired data and find minimum and maximum value.

- Using this information, determine the noise region as the (minimum value + (0.05 \* maximum value)).

- Iterate again the acquired data and find a mean value for any sample that is below the just specified threshold.

- Finally iterate all the acquired data and take away this just calculated mean value.

In this way, all the noise samples would reach the 0 area in the y axis, while the original shape of the data would stay unchanged.

Last but not least, the rtStop action stored the intermediate buffers to the shared memory (device fields). This was accomplished by declaring the above buffers with the C++ key word *extern* and hence they were visible by more than one C++ class in the server.

The server actions that served the Setting and Expert Setting interfaces were implemented as simple actions. What is more and only for the Setting property, partial setting was allowed. As for the Calib Data property complex GET/SET actions were implemented with the partial setting enabled. Lastly, for the Acquisition and User Data, complex GET actions copied the contexts of the shared memory (fields) to the interface memory in order to be properly presented.

At this point, it's worth mentioning few words about the buffers holding the data, intermediate and final. The acquisition data were stored in two dimensional arrays; first dimension for the different measurements made by the endCapture and second dimension for the acquisition itself –intensity values for bunch slots 1-924. Unfortunately, there was no useful way to present these values with FESA interface and thus filters were being used.

Hence, under User Data property, the user had to specify in the filter which measurement desired to observe. Using this filter in the server action, only one raw of the 2D arrays was returned (924 values in total). In this way, data were quite uncomfortable to be studied, since the filters apply in the acquired data only once and thus one should wait for the next acquisition to see another measurement. One such example can be seen at Figure 2-10.

#### 2.4 The FBCTs in the LHC

In the LHC ring there are three FBCT systems, each consisting of 4 DABs as described in chapter 2.2.1. System A and B use the original version of the FBCT's firmware which used to have 4 measurement modes [16]:

- Capture the intensity measurement in each bunch slot for a specified number of turns

- **Turn Sum** a total intensity measured from a full bunch acquisition (3564 bunches) over a single turn

- **Slot Sum** a total intensity measured for a specified bunch slot over specified number of turns

- **Sum Sum** the combination of *Turn Sum* and *Slot Sum*. By this we mean to make a *Turn Sum* for each acquired turn and then, sum all these sums as they were a single bunch slot measurement

## 2.4.1 Software Architecture

The FESA class that serves LHC's A and B FBCT measurement systems is BCTFRLHC v31<sup>2</sup>. The server of both systems is identical and has two instances, serving the FBCT installation for each circulating beam.

The version 31 of the BCTFRLHC FESA class is designed to provide LBW total intensities averaged over 225 consecutive turns at 1Hz. In addition, it provides HBW total intensities per turn with time resolution up to one turn (89µs) as well as HBW individual bunch intensities averaged over 900 turns as input for the post-mortem system for analyzing the causes of machine protection beam dumps. [18]

# 2.4.2 Existing Implementation

The server uses the LBW channel to make full bunch acquisitions over 225 consecutive turns – to suppress the noise at  $50~\mathrm{Hz}$  – using firmware's Sum~Sum measurement method and it continuously updates them every second for operational displays. Additionally, it keeps the values from the last 30 seconds in a rolling data buffer, which also updates every second.

As for the HBW channel, the server uses the firmware's *Turn Sum* measurement mode to produce and publish the turn intensities – the total intensities per turn – and the *Slot Sum* measurement for the average individual bunch intensities. Both measurements are updated every second.

<sup>&</sup>lt;sup>2</sup> Created by Michael Ludwig

In order to suppress errors in the calculation of the noise mean value at the baseline restoration (BLR) procedure, the summing of empty buckets must be avoided. This is achieved by applying a minimum beam threshold set by the user. The BLR is based on the presence of empty buckets in each turn at least at the  $3\mu$ s abort gap and hence, the calculation of the minimum integrated value of one turn can be used as offset correction for the next one. Subsequently, the lowest measurable turn-sum and bunch-average intensity is given by the noise suppression peak threshold –  $10^8$  number of charges for high gain and  $5*10^8$  number of charges for low gain for both bandwidths. [18]

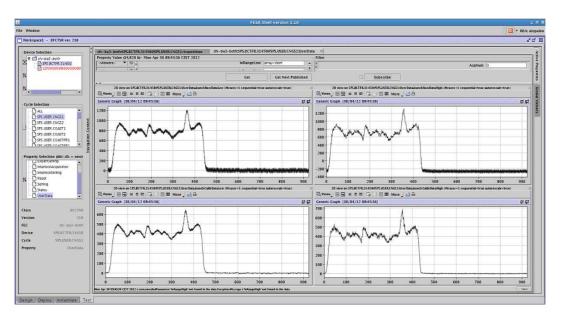

Figure 2-11: Total Intensity History from beam1 of the LHC, System B

The above figure 2-11 depicts the rolling data buffer of the total intensity of beam 1 as it was measured by the FBCT in the system B. This buffer holds the calculated total intensities of the last 30 seconds – 1 acquisition over 225 turns takes 20ms hence 50 values per second and 1500 per 30 seconds. As there is no expert GUI developed, the client application that is being used to control the servers is the FESA interface.

# 3 Our Implementation

In the previous section we described all the theoretical and technical background needed to better understand the previous software implementation for the FBCTs in the SPS and the existing one for the LHC. In this section we analyze our proposal for both systems separating the design from the technical part.

# 3.1 High level

As the developing of the two systems was ongoing, we came across several decisions that needed in order to proceed. This chapter is dedicated to such decisions that helped us to structure better our work and provide us useful tools for our implementations.

#### 3.1.1 Wrapper - Design

Since the firmware changed, a new way of accessing the device was needed. As the new firmware was to be deployed in both SPS and LHC FBCTs, we decided to create a common wrapper class, DABBFCTSRWrapper, which abstracts the device communication with the server. Additionally, such class is ideal for implementing functionalities irrelevant with the accelerator that hosts the FBCTs.

The DABBFCTSRWrapper is designed to have public methods for accessing all the device's registers using the IOCTL library, as well as processing some of the data that need to be read from or written to it, while there are also some other private methods for that scope as well.

Finally the header file of the wrapper seemed the perfect place for implementing the hash table with the different commands that the device can handle since it is imported every time we want to use it in the project for accessing the hardware and hence to instruct it to do something. In this way we've implemented it once being sure that is always visible in our general implementation.

#### 3.1.2 Tester - Design

Another decision that was taken in the early days of our implementation was to create an additional tester class for testing the proper communication with the device. This class used to do nothing else but trying and write all the writable registers of the device and then read them back. In this way, several errors in the firmware were revealed when it was easy to be spotted and fixed.

While progressing with our implementation, the tester was changed to fit our testing needs. Hence, the tester ended up asking the user to select the bunches and the number of turns for acquisition, then firing the acquisition, reading back the data and printing them in the console as raw ADC values, just as they were read from the device. This procedure was found incredibly useful for studying, testing and assuring the decoding process of the data (look at chapter 2.2.2 – last paragraph / change of the data capture organization).

Furthermore, additional timing routines were added in order to study the different driver solutions for fetching the data from the device to the CPU, as well as some

performance issues, especially as the server in LHC is concerned. These issues are being discussed in greater detail in chapter 3.2.5.

#### 3.1.3 DabInfo - Design

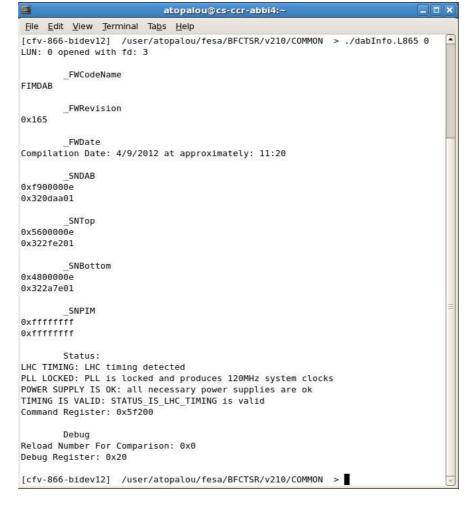

As described in chapter 2.2.2 and table 2-4, there are some registers in firmware related to the DAB's information such as serial numbers and so on. Hence, it was found useful to have a console application that would retrieve and present this information. In this way, we were able to check the identification of the firmware, the mezzanines as well as the DABs themselves installed in the SPS, the LHC or the lab.

#### 3.1.4 SPS

Our implementation is based on the existing one. We used this version and updated it so that it can access the new hardware and have one different acquisition mode the TURN\_BY\_TURN as we called it, as well as improving some troublesome behavior relative to base line restoration. Our main goal, beside the proper functionality of the server of course, was to keep as much backwards compatibility as we could by changing the design as less as possible.

Hence, a new real time action was introduced; the rtTurnAcq which implements the new acquisition mode, while the rtPrepare remained the same, at least as far as the design is concerned.

The main difference to the existing classes was at the rtStart and endCapture class which were not needed if the acquisition mode was TURN\_BY\_TURN, and thus should exit immediately. The same idea was introduced to the new rtTurnAcq class but the other way round, it would exit if the acquisition mode was REPETITVE. The event that wakes the rtTurnAcq is a warning of the beam's injection which come 20msec in advance. The new class is responsible to start the acquisition with 18msec delay, read the data, process them, transform them from ADC bins to number of charges, restore their baseline and finally save them to the appropriate buffers.

We kept the rtStop class the same which only copies the data from the buffers to the shared memory when the cycle is over. This is common for both acquisition modes and so, it made sense to try and keep it the same. In order to do that though, we had to change the buffers visibility through the server classes. In that sense, the variables that should be common to both acquisition modes and thus the appropriate classes, are now being created and initialized in the rtPrepare class and are visible by the endCapture, rtTurnAcq and rtStop by using again the keyword *extern*.

#### 3.1.4.1 Baseline Restoration

The existing algorithm that used to correct the baseline was working quite well but unfortunately not always. It was observed that whenever there was a negative spike quite bigger than expected the algorithm didn't work. Since the algorithm was taking into account the ratio between the minimum and maximum value within an acquisition to determine the noise region, in case of this so called "undershoot" this region would include only one point, the minimum. As a result the minimum would be considered as noise and thus, after the BLR

it would end up to be 0 and everything, including the actual noise, to be in the positive side of the graph. This can be easily seen at the following graphs:

Figure 3-1: ROSALI plot with error in BLR

Figure 3-2: ROSALI plot with correct BLR

These "undershoots" won't come often and for every cycle, but when they come the BLR doesn't work as it should be. That is why we considered changing the existing algorithm for restoring the BLR to another one much simpler and more stable.

We've decided not to take into account the min – max difference to specify the noise region, since this can change from cycle to cycle and from time to time. The hard coding percentage of that difference wasn't flexible enough when those differences appeared. Hence,

we search only for the minimum value of an acquisition and noise area is determined by a user setting. In this way, the BLR is much more flexible and dynamic.

Of course this does not erase the "undershoot" problem, since they don't come in a deterministic way and thus one cannot specify a well-defined noise area and trust that would work for a longer period of time. In addition, an "undershoot" identifier had to be designed in order to help us ignore this kind of extreme values. To do that though, the user should provide another setting specifying the distance between two consecutive points that would identify the most negative as an "undershoot".

## 3.1.4.2 TURN\_BY\_TURN acquisition mode

The most important change to the server was to add the new acquisition mode. As it was mentioned before, a full bunch acquisition (bunches: 1-924) over one turn, is repeated every 40msec until the end of every cycle. This mode of acquisition, REPETETIVE, covers the whole cycle and it was being used until now.

The new acquisition mode, TURN\_BY\_TURN, is again a full bunch acquisition but for as many consecutive turns as the data storage permits. This limitation comes from our effort to keep the backwards compatibility and hence by the fact that we use the same intermediate buffers in software as the REPETETIVE mode. For more details about the implementation of these buffers and their limitations please refer to chapter 3.2.4.

#### 3.1.4.3 Client – Interface

The BFCTSR\_ExpertGUI was developed in Java and is organized in 5 packets for clearer separation of its classes. The *Constants* packet hosts all the classes that consist of constant data such as enumerations, names and converters. In the *expertGUI* packet, all the classes that implement the application interface are stored. Furthermore, there are the *factories* and *listeners* packets which host the homonyms classes. Last but not least is the *Data* packet where all the classes that are data specific are stored.

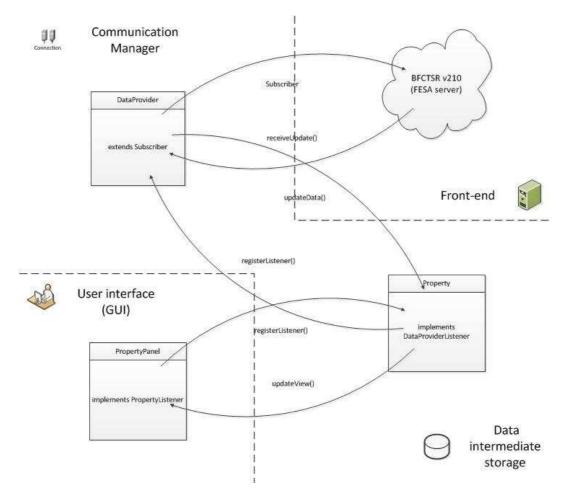

For the communication with the server, we used the *communication* library that was developed from our group and establishes a communication flow per device. We kept the communication and subscription mechanism over the network separated to one class called *DataProvider* and the data storage per FESA property to another called *Property*. Both classes are abstract since only few methods are domain specific and had to be separated.

The general idea of the design is the following: the *DataProvider* communicates via subscription to the server that runs on the front-end. Each time new data are produced, the *DataProvider* informs the *Properties* which process them if needed and store them to buffers. Then, they inform their interfaces to update their view with the new data. This data flow is depicted in the following figure:

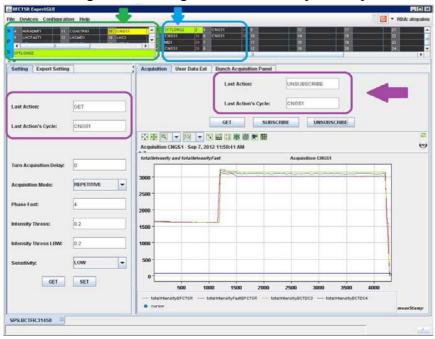

Figure 3-3: Data flow between front-end server and GUI client

We decided to split the frame into three areas. The top one hosts the TimingPanel component which shows which cycle is active per accelerator so that the users can choose an appropriate one. The left one hosts the setting and expert setting panels as tabs while the right one hosts the acquisition, UserData and BunchAcquisition panels as tabs. The representation of the data is on the right area of the frame and more specifically the acquisition tab is a graph of the total intensities as acquired and calculated from BFCTSR as well as two more devices for cross-checking, BCTDC3 and BCTDC4. The UserData tab hosts a graph of the individual bunch intensity measurements — one measurement at a time, while the BunchAcquisition tab hosts a 3D graph of the individual bunch intensity measurements — all together.

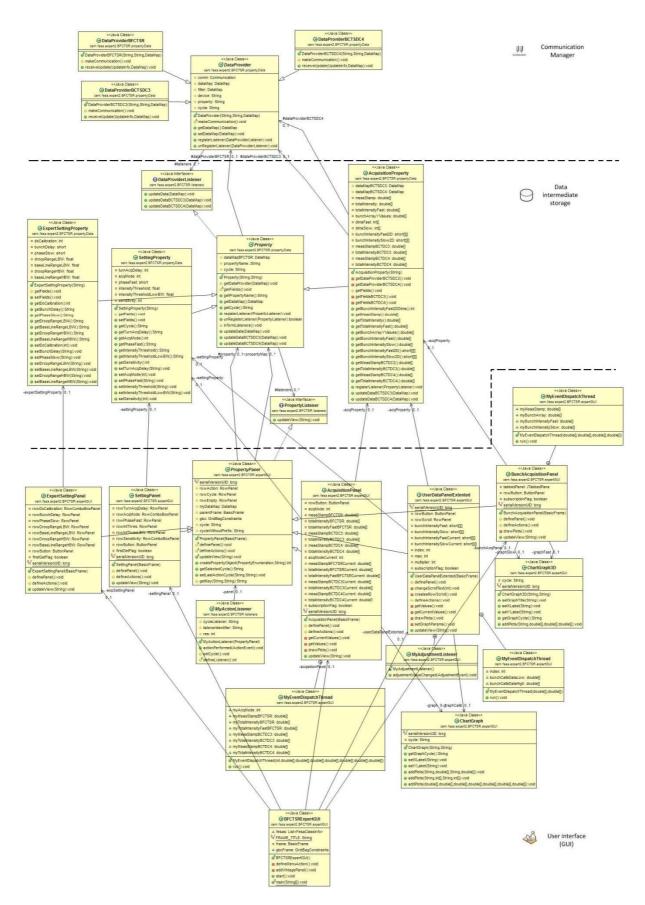

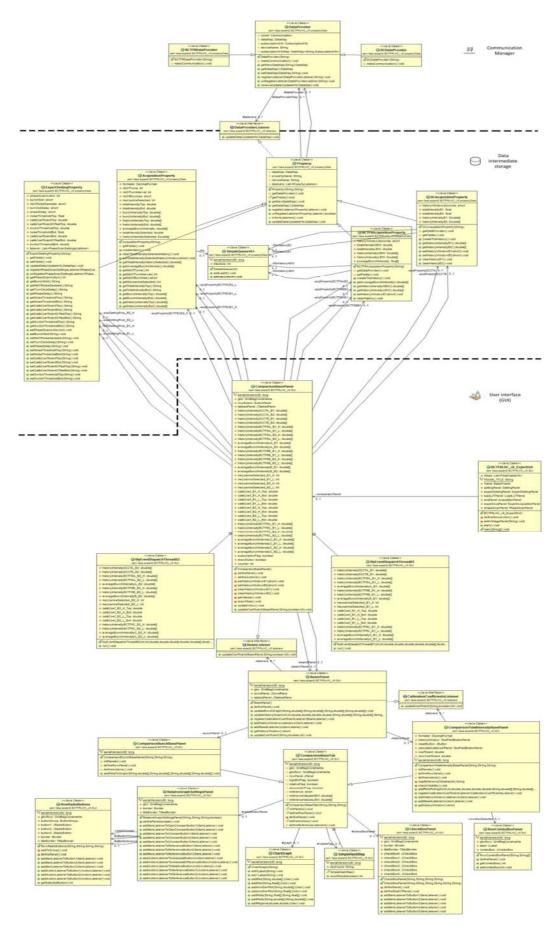

In figure 3-4 the Unified Modeling Language (UML) class diagram of our expert GUI is depicted according to entity separation of figure 3-3. The communication between two classes from a different group (Communication Manager, Intermediate Data Storage and GUI) is achieved with separated interfaces.

Figure 3-4: BFCTSR\_ExpertGUI UML Class Diagram

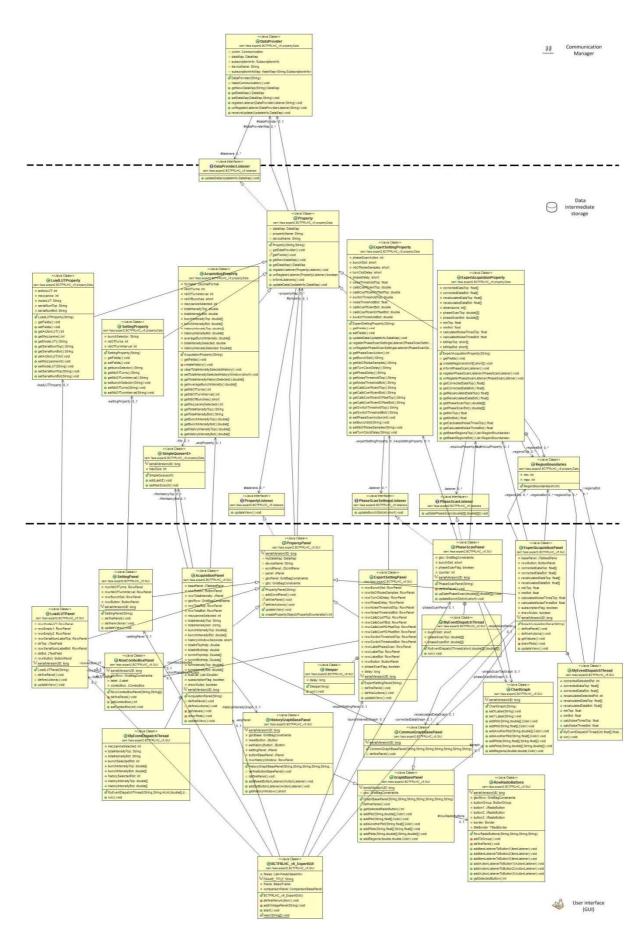

#### 3.1.5 LHC