## Hardware Design Implementation of HEVC IDCT Algorithm with High-Level Synthesis

Author

Magoulianitis Vasileios

A thesis submitted for the Faculty of the Department of Electrical and Computer Enginnering in Partial Fulfillment of the Requirements for the Diploma of Science

Supervisors:

Dr. Christos Sotiriou Dr. Gerasimos Potamianos

Department of Electrical and Computer Engineering UNIVERSITY OF THESSALY

October 13, 2015

#### UNIVERSITY OF THESSALY

Department of Electrical and Computer Engineering

# Hardware Design Implementation of HEVC IDCT Algorithm with High-Level Synthesis

by

Magoulianitis Vasileios

Graduate Thesis for the degree of Diploma of Science in Computer and Communication Engineering

Approved by the two member inquiry committee at 13th of October 2015

Dr. CHRISTOS SOTIRIOU

Dr. GERASIMOS POTAMIANOS

### **Declaration of Authorship**

I, Vasileios Magoulianitis, declare that this thesis titled, 'Hardware Implementation of HEVC Inverse Integer Transform with High-Level Synthesis Tool' and the work presented in it are my own. I confirm that:

- This work was done wholly or mainly while in candidature for a bachelors degree at this University.

- Where any part of this thesis has previously been submitted for a degree or any other qualification at this University or any other institution, this has been clearly stated.

- Where I have consulted the published work of others, this is always clearly attributed.

- Where I have quoted from the work of others, the source is always given. With the exception of such quotations, this thesis is entirely my own work.

- I have acknowledged all main sources of help.

- Where the thesis is based on work done by myself jointly with others, I have made clear exactly what was done by others and what I have contributed myself.

Signed:

Date:

"The roots of education are bitter, but the fruit is sweet."

Aristotle

### Abstract

Video applications are used widely nowadays, supporting different aspects of our life, such as entertainment, security, medicine e.t.c.. However, the increasing number of video contents yields issues in its storage and transmission, since it conveys high volume of data. High Efficiency Video Coding (HEVC) is the new video compression standard, reducing bitrates nearly at half compared to its predecessor the H.264, supporting high demanding video contents. This reduction in bitrate is achieved by a series of computationally expensive algorithms, thus making imperative to implement some complex parts of HEVC into hardware, so as to meet the real-time constraint of video coding applications. Unfortunately, hardware design maintains large cycle for design and verification processes and therefore many man-months have to be spend for a hardware video codec implementation.

High-Level Synthesis (HLS) draws much attention from industry lately, because of the short time-to-market value that it offers. Describing an algorithm with C/C++, is much easier than writing Hardware Description Languages (HDLs), while lets to explore different architectures for the same algorithm. Also, HLS is used widely for Digital Signal Processing (DSP) applications, one of them being video coding. Therefore, the subject of this thesis is the design space exploration of the HEVC Inverse Integer Transform (IIT) using the Vivado HLS tool, for synthesis on FGPAs. Different code versions and directives, yields different RTLs in terms of latency and device utilization. All these RTLs, are extensively analyzed according to their throughput performance, identifying the different video contents that each of them can support. Finally, a throughput comparison is conducted among other levels of implementation, in order to find how efficient are the RTLs from a HLS tool. Results, show that HLS tools provide great flexibility for design space exploration of RTL, but their efficiency (*performance/area*) is still far, when compared with RTLs written by human's hand.

# Περιληψη

Οι διαφορες χρησεις του βιντεο στις ημερες μας, πληθαινουν ολοενα και περισσοτερο κυριως σε τομεις οπως η ψυχαγωγια, η ασφαλεια, η ιατρικη κ.τ.λ. Ο αυξανομενος αριθμος των εφαρμογων που χρησιμοποιουν βιντεο, δημιουργει προβληματα τοσο στην αποθηχευση του, οσο και στην μεταδοση του διαμεσω καναλιων επικοινωνιας, καθιστωντας την συμπιεση των δεδομενων βιντεο ιδιατερα σημαντικη. Το τελευταο βιντεο στανταρντ Η.265 προσφερει σημαντική συμπιεσή στα δεδομενα, σχεδον διπλασια από το προηγουμενό Η.264 στανταρντ. Ωστοσο, το διπλασιο χερδος σε συμπιεση, επιτυγχανεται χρησιμοποιωντας μια σειρα πολυπλοχων αλγοριθμων, αυξανοντας την συνολιχη πολυπλοχοτητα στον αποχωδιχοποιητη περιπου στο διπλασιο, ο οποιος σημειωτεον, πρεπει οπωσδηποτε να τρεξει σε πραγματικό χρονό και να επεξεργάζεται δεδομένα με συγκεκριμένο ρυθμό. Ως εκ τουτού, γινεται σαφες οτι χαποιοι περιπλοχοι αλγοριθμοι, θα πρεπει να υλοποιηθουν σε υλιχο ετσι ωστε να επιταγχυνουμε την αποκωδικοποιηση. Οσων αφορα τωρα την αναπτυξη υλικου, τελευταια απο τη βιομηχανια εχουν αρχισει να εξερευνωνται εργαλεια συνθεσης απο υψηλο επιπεδο, λογω του μικρου κυκλου εργασιας που απαιτουν για την σχεδιαση και επαληθευση κυκλωματων. Ειδικοτερα, τετοια εργαλεια χρησιμοποιουνται ευρεως για αλγοριθμους ψηφιακης επεξεργασιας σηματων -οπως ειναι η συμπιεση του βιντεο- επιτρεποντας διαφορετικες αρχιτεκτονικές λυσείς για έναν αλγοριθμο σε μικρό χρονικό διαστήμα. Ετσι, το αντικείμενο αυτης της εργασιας ειναι η εξερευνηση του χωρου λυσεων διαφορων χυχλωματων για τον αντιστροφο μετασχηματισμο του αποκωδικοποιητη Η.265 με χρηση καταλληλων εργαλειων για συνθεση απο υψηλο επιπεδο. Οι διαφορετιχοι χωδιχες χαι οι διαφορετιχες οδηγιες που δοθηκαν στο εργαλειο, μας εδωσαν διαφορετικα κυκλωματα, με βαση τον χωρο που καταλαμβανουν σε μια επαναπρογραμματιζομενη συσχευη με βαση τον ρυθμο των δεδομενων που επεξεργαζονται καθε δευτερολεπτο. Ολα ται διαφορετικα κυκλωματα που μας εδωσε το εργαλειο, διευρενωνται ως προς την αποδοση τους, ωστε να διαπιστωσουμε ποσο αποδοτικες ειναι οι λυσεις που βγαζουν αυτα τα εργαλεια, σε συγχριση με αλλα επιπεδα υλοποιησης. Τελιχα, στοχος μας είναι να δουμε ποια είναι τα ορία αυτών των εργαλειών και ποιο είναι το μεγαλυτερο αναλυσης βιντεο που μπορει να υποστηριχθει απο τετοια χυχλωματα. Τα αποτελεσματα δειχνουν, οτι τα εργαλεια συνθεσης απο υψηλο επιπεδο, προσφερουν μεγαλη ευελιξια, τοσο στην συνθεση οσο και στην επαληθευση των κυκλωματων, αλλα ειναι μακρια σε αποδοση, σε σχεση με χυχλωματα, στα οποια η αρχιτεχτονιχη περιγραφεται απευθειας απο τον ανθρωπο.

### Acknowledgements

At this point, I feel glad to express my sincere gratitude to my supervisor, Professor Christos Sotiriou, who trusted and supported me throughout this work. His technical background and in depth knowledge of the subject, provided valuable feedback to this thesis. Also, i would like to thank him for his precious advices from our office discussions.

Furthermore, i would like to thank my co-advisor, Professor Gerasimos Potamianos, for his feedback at the final stages of this thesis.

Once the accomplishment of this work required mixed knowledge from different divisions of computer engineering, i would like to express my acknowledgments to all the professors that i collaborated through my undergraduate studies.

I am also grateful to my closest friends and colleagues for helping and supporting me all those years.

Last but not least, I would like to thank the members of my family, for everything they offered me in all aspects of my life and their support during my academic experience.

## Contents

| Declaration of Authorship | ii   |

|---------------------------|------|

| Abstract                  | i    |

| Περιληψις                 | i    |

| Acknowledgements          | i    |

| List of Figures           | iv   |

| List of Tables            | vi   |

| Abbreviations             | viii |

| 1 | Intr | roduction                        | 1  |

|---|------|----------------------------------|----|

|   | 1.1  | Motivation                       | 3  |

|   | 1.2  | Objective                        | 4  |

|   | 1.3  | Other Works                      | 5  |

|   | 1.4  | Thesis Structure                 | 6  |

| 2 | Vid  | eo Coding Background             | 8  |

|   | 2.1  | Video in Signal Processing       | 8  |

|   | 2.2  | Typical Compression Diagram      | 9  |

|   |      | 2.2.1 Spatial Correlation        | 2  |

|   |      | 2.2.2 Temporal Correlation       | 4  |

|   | 2.3  | Video Standards                  | 6  |

|   |      | 2.3.1 MPEG-1/2                   | 6  |

|   |      | 2.3.2 MPEG-4                     | 7  |

|   |      | 2.3.3 H.264/AVC                  | 7  |

|   |      | 2.3.4 H.265/HEVC                 | 8  |

| 3 | HE   | VC Inverse Integer Transform 2   | 0  |

|   | 3.1  | Discrete Fourier Transform (DFT) | 21 |

|   | 3.2  | Discrete Cosine Transform (DCT)  | 23 |

|   | 3.3 | Fast T | ransform Implementation                         | 25 |

|---|-----|--------|-------------------------------------------------|----|

| 4 | Hig | h Leve | l Synthesis on FPGA                             | 28 |

|   | 4.1 | Introd | uction                                          | 29 |

|   |     | 4.1.1  | HLS flow                                        | 31 |

|   | 4.2 | Vivado | HLS – Tutorial                                  | 33 |

|   |     | 4.2.1  | Directives                                      | 35 |

|   |     | 4.2.2  | Latency-Based Control                           | 38 |

| 5 | Exp | erime  | ntal Methodology                                | 41 |

|   | 5.1 | Genera | al Flow                                         | 42 |

|   |     | 5.1.1  | Reference Source                                | 43 |

|   |     | 5.1.2  | Inline Shift–Add Source                         | 44 |

|   |     | 5.1.3  | Function Shift–Add Source                       | 44 |

| 6 | Res | ults   |                                                 | 46 |

|   | 6.1 | Vivado | HLS Results                                     | 47 |

|   |     | 6.1.1  | Reference Code                                  | 48 |

|   |     | 6.1.2  | Inline Shift–Add Code                           | 51 |

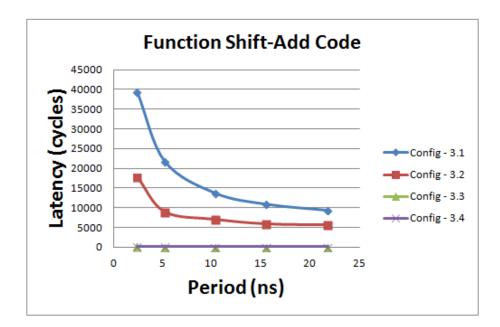

|   |     | 6.1.3  | Function Shift–Add Code                         | 53 |

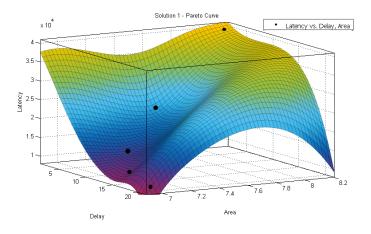

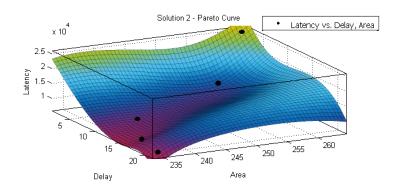

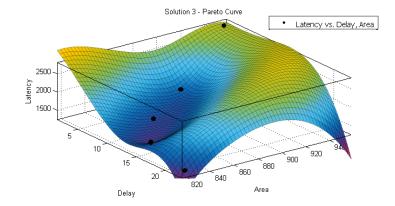

|   | 6.2 | Area - | - Delay – Latency                               | 55 |

|   |     | 6.2.1  | 2-D Diagrams                                    | 56 |

|   |     | 6.2.2  | 3-D Diagrams                                    | 60 |

|   | 6.3 | Throu  | ghput Exploration                               | 62 |

|   |     | 6.3.1  | Min–Max Throughput                              | 63 |

|   |     | 6.3.2  | Weighted Throughput                             | 68 |

|   |     | 6.3.3  | Comparing Other implementations                 | 71 |

|   |     |        | 6.3.3.1 Reference Software Implementation (x86) | 71 |

|   |     |        | 6.3.3.2 SIMD–Reference Software                 | 73 |

|   |     |        | 6.3.3.3 Custom Hardware RTL                     | 74 |

|   |     | 6.3.4  | Supporting Different Videos                     | 76 |

| 7 | Con | clusio | n and Future Work                               | 80 |

|   | 7.1 | Conclu | nsion                                           | 80 |

|   | 7.2 | Future | Work                                            | 81 |

# List of Figures

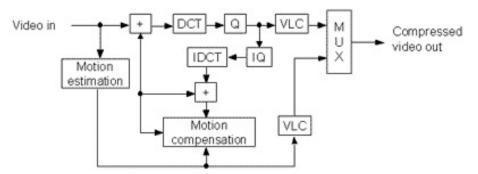

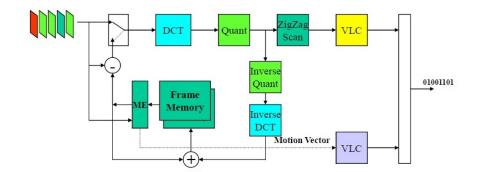

| 2.1  | Architectural diagram of a typical video codec [44]                                                 | 10 |

|------|-----------------------------------------------------------------------------------------------------|----|

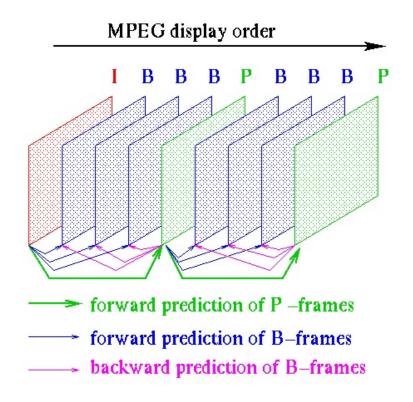

| 2.2  | A group of pictures with I, P, B frames [39]                                                        | 10 |

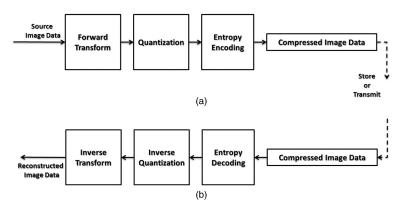

| 2.3  | Basic stages of JPEG codec for still image compression [40]                                         | 11 |

| 2.4  | Deblocking Filter [41]                                                                              | 12 |

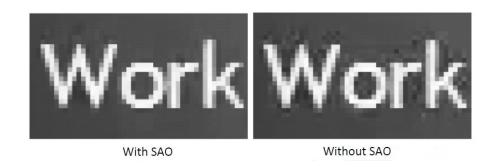

| 2.5  | Sample Adaptive Offset (SAO) filter [20]                                                            | 12 |

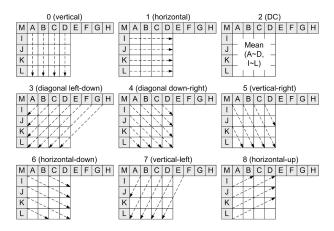

| 2.6  | Possible directions for intra prediction in H.264/AVC standard [2]                                  | 13 |

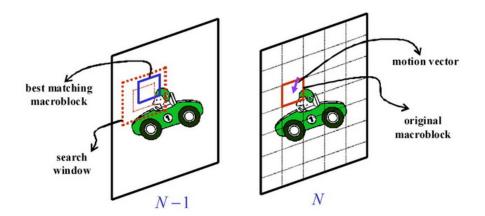

| 2.7  | Motion estimation algorithm. Finds best match block in different temporal                           |    |

|      | frames. Motion vector indicates how far from current position best block is                         |    |

|      | located [42]                                                                                        | 15 |

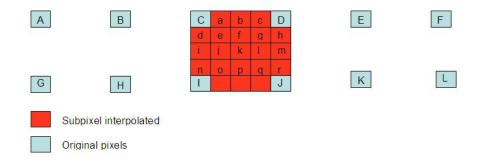

| 2.8  | All possible sub-pixel values that can be found in quarter distance. Different                      |    |

|      | filters are used to obtain values in each position [43] $\ldots \ldots \ldots \ldots \ldots \ldots$ | 15 |

| 2.9  | Typical diagram of an MPEG-1/2 encoder [44]                                                         | 17 |

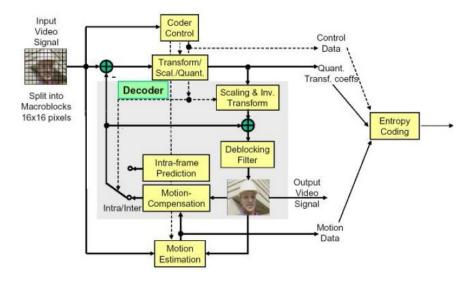

| 2.10 | Typical diagram of an H.264/AVC codec [2]                                                           | 18 |

| 2.11 | Typical diagram of an H.265/HEVC codec [1]                                                          | 19 |

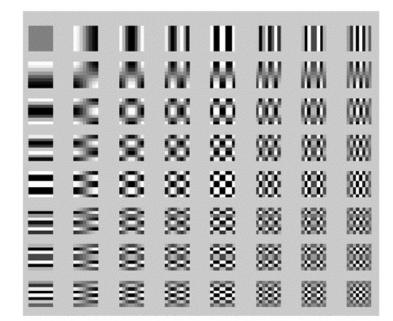

| 3.1  | $8 \times 8$ DFT basis functions [28]                                                               | 22 |

| 3.2  | DFT vs DCT in terms of signal reconstruction [29]                                                   | 23 |

| 3.3  | $8 \times 8$ DCT basis functions [28]                                                               | 24 |

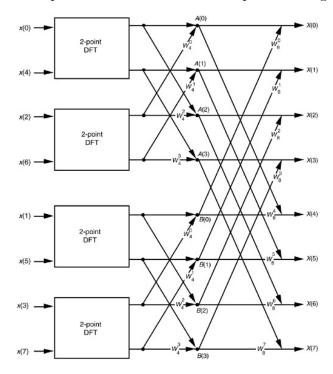

| 3.4  | Cooley-Tukey algorithm with radix-4 [26]                                                            | 26 |

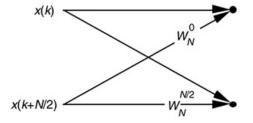

| 3.5  | Radix-2 bytterfly [26]                                                                              | 26 |

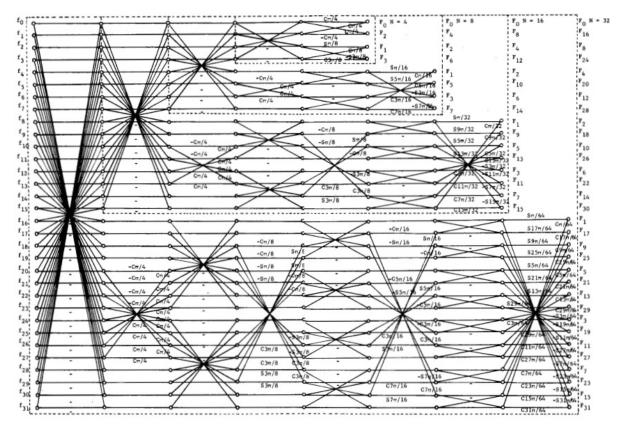

| 3.6  | Signal flow graph of Chens fast factorization for 4x4, 8x8, 16x16 and 32x32                         |    |

|      | transforms [38]                                                                                     | 27 |

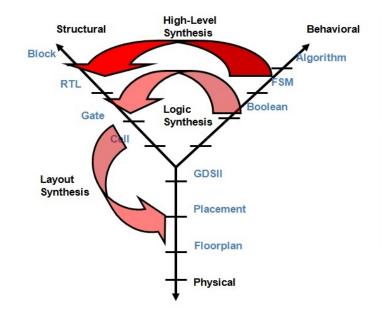

| 4.1  | Abstraction layers on digital circuit design [33]                                                   | 30 |

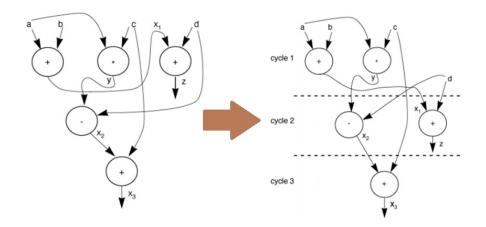

| 4.2  | Different operations are scheduled in clock cycles [34]                                             | 31 |

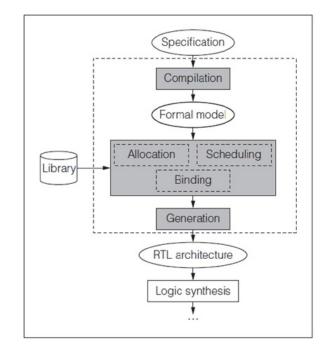

| 4.3  | High Level Synthesis general flow diagram [35]                                                      | 32 |

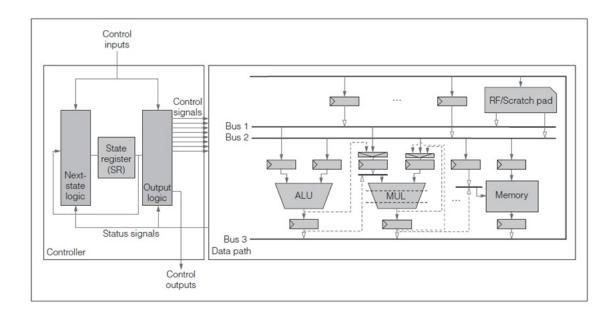

| 4.4  | Typical structure of RTL, produced from a High Level Synthesis tool [35]                            | 33 |

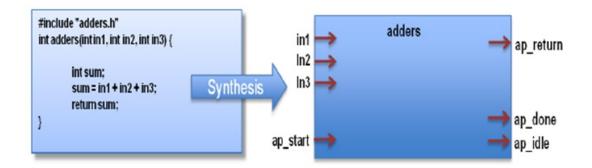

| 4.5  | A small example of C code and what interface signals are produced at top module                     |    |

|      | level after high level synthesis process [32]                                                       | 35 |

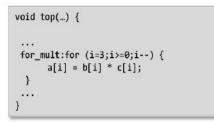

| 4.6  | Partial and full loop unrolling example in a small loop. Latency is improved as                     |    |

|      | level of unrolling increases [32]                                                                   | 37 |

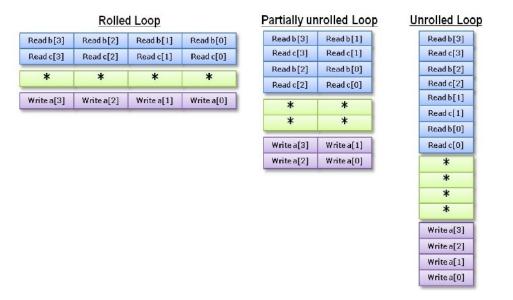

| 4.7  | Pipelining betweern different operarations and loops examples. Interval and                         |    |

|      | throughput are directly affected [32]                                                               | 38 |

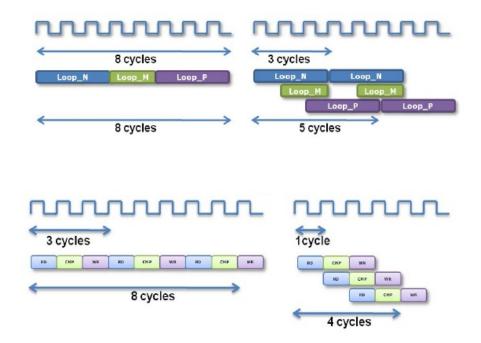

| 4.8  | In unpipelined designs, different latency information is stored for different data                  |    |

|      | paths. According to the input signals, FSM chooses each of them for output in                       |    |

|      | specific latency cycles                                                                             | 40 |

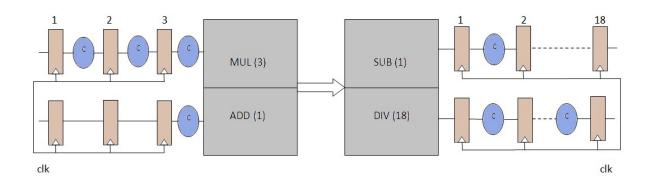

| 4.9  | Two modules with different latencies are aligned in worst latency by adding FFs,                    |    |

|      | when RTL is pipelined                                                                               | 40 |

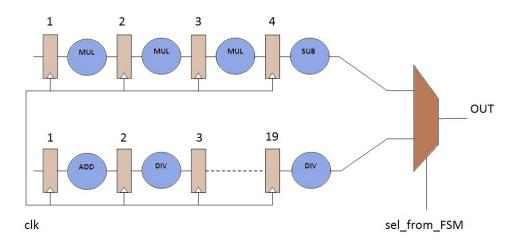

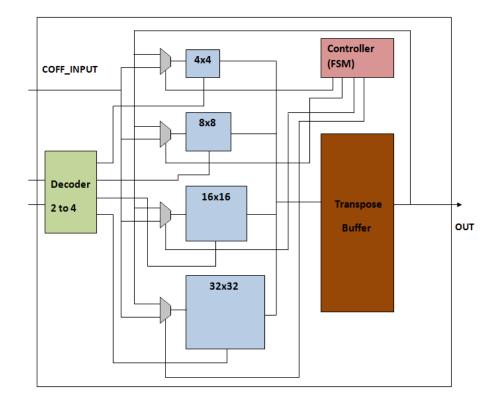

| 6.1  | Block diagram at the top module hierarchy level that Vivado HLS tool yielded              |    |  |

|------|-------------------------------------------------------------------------------------------|----|--|

|      | for all the different RTLs.                                                               | 47 |  |

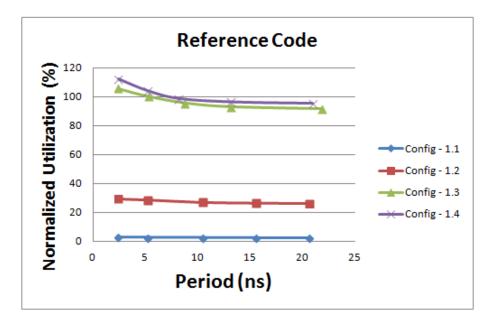

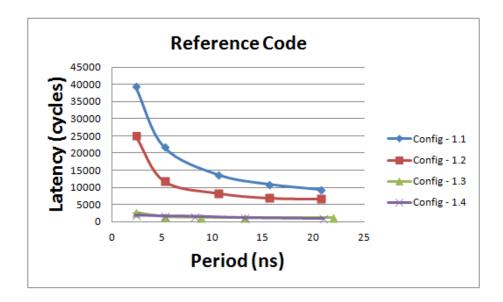

| 6.2  | Normalized Utilization – Delay diagram for reference code experiment                      | 58 |  |

| 6.3  | Latency – Delay diagram for reference code experiment                                     | 58 |  |

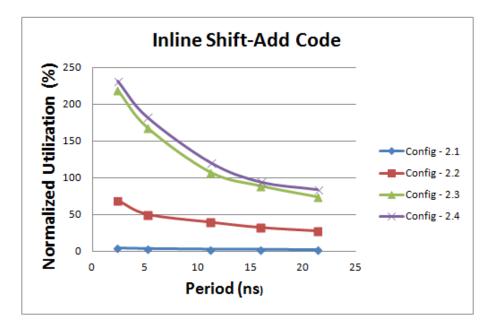

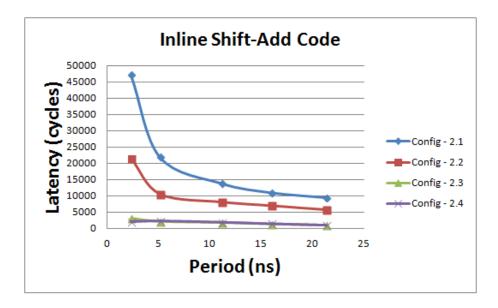

| 6.4  | Normalized Utilization – Delay diagram for inline shift-add code experiment               | 59 |  |

| 6.5  | Latency – Delay diagram for inline shift-add code experiment                              | 59 |  |

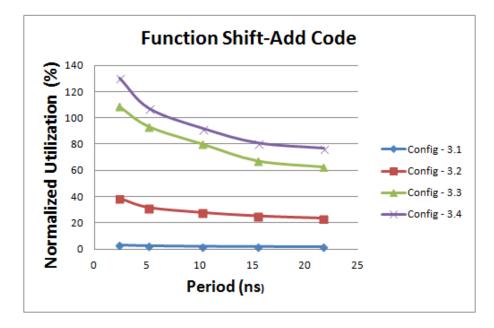

| 6.6  | Normalized Utilization – Delay diagram for function based shift-add code exper-           |    |  |

|      | iment                                                                                     | 60 |  |

| 6.7  | Latency – Delay diagram for function based shift-add code experiment                      | 60 |  |

| 6.8  | Configuration 1.1 – Trafe off Surface from Vivado HLS – Latency, Area, Delay $\therefore$ | 61 |  |

| 6.9  | Configuration 1.2 – Trafe off Surface from Vivado HLS – Latency, Area, Delay $\therefore$ | 62 |  |

| 6.10 | Configuration 1.3 – Surface from Vivado HLS – Latency, Area, Delay 6                      | 62 |  |

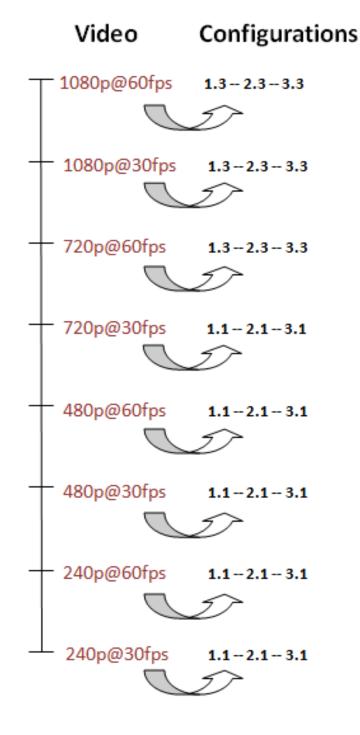

| 6.11 | Usual video contens and which congigurations can support them with minimum                |    |  |

|      | device utilization. Solutions from three codes are presented, because each of             |    |  |

|      | them may support a video, reserving different percentages for FPGA resources $\ $         | 79 |  |

## List of Tables

| 2.1  | Popular video standards that have been used in video applications                             | 16       |

|------|-----------------------------------------------------------------------------------------------|----------|

| 4.1  | Directives for function level optimizations                                                   | 36       |

| 4.2  | Directives for loop level optimizations                                                       | 36       |

| 4.3  | Directives for array-storage level optimizations                                              | 37       |

| 6.1  | All different configurations that experiments were conducted                                  | 48       |

| 6.2  | Configuration 1.1 – HLS Report for different delay constraints on the same con-<br>figuration | 49       |

| 6.3  | Configuration 1.2 – HLS Report                                                                | 50       |

| 6.4  | Configuration 1.3 – HLS Report                                                                | 50       |

| 6.5  | Configuration 1.4 – HLS Report                                                                | 50       |

| 6.6  | Configuration 2.1 – HLS Report                                                                | 52       |

| 6.7  | Configuration 2.2 – HLS Report                                                                | 52       |

| 6.8  | Configuration 2.3 – HLS Report                                                                | 52       |

| 6.9  | Configuration 2.4 – HLS Report                                                                | 53       |

| 6.10 | Configuration 3.1 – HLS Report                                                                | 54       |

| 6.11 | Configuration 3.2 – HLS Report                                                                | 54       |

| 6.12 |                                                                                               | 54       |

| 6.13 | Configuration 3.4 – HLS Report                                                                | 55       |

|      | Top Module Throughput in <i>Msamples/sec</i> Min–Max results from reference code              |          |

|      | implementation                                                                                | 66       |

| 6.15 | Sub-Modules Throughput in $Samples/cycle$ Min–Max results from reference                      |          |

|      | code implementation                                                                           | 66       |

| 6.16 | Top Module Throughput in $M samples/sec$ Min–Max results from inline shift-                   |          |

|      | add code implementation                                                                       | 66       |

| 6.17 | Sub-Modules Throughput in Samples/cycle Min–Max results from inline shift-                    |          |

|      | add code implementation                                                                       | 66       |

| 6.18 |                                                                                               |          |

|      | shift-add code implementation                                                                 | 67       |

| 6.19 | Sub-Modules Throughput in <i>Samples/cycle</i> Min–Max results from function based            | ~ -      |

|      | shift-add code implementation                                                                 | 67       |

| 6.20 | Results from several reference video bitstreams, regarding TU utilization for                 | 70       |

| C 91 | different resolutions and QPs                                                                 | 70       |

|      | Reference code weighted throughput for different video resolutions                            | 70<br>70 |

|      | Inline Shift-add code weighted throughput for different video resolutions                     | 70<br>70 |

|      | Function Shift-add code, weighted throughput for different video resolutions                  | 70<br>72 |

|      | Reference code sub-module's throughput                                                        | 72<br>72 |

| 0.25 | Inline shift-add code sub-module's throughput                                                 | 72       |

| 6.26 | Function shift-add code sub-module's throughput                                 | 7 | 3 |

|------|---------------------------------------------------------------------------------|---|---|

| 6.27 | Throughput results from reference code running on an AMD processor              | 7 | 3 |

| 6.28 | Throughput results from reference code after SIMD optimization, on general      |   |   |

|      | purpose microprocessor                                                          | 7 | 4 |

| 6.29 | Latency and Throughput results for 4, 8 and 16 core transform for FPGA $@~251$  |   |   |

|      | MHz                                                                             | 7 | 5 |

| 6.30 | Throughput requirement in (Msamples/sec) for different resolutions of video and |   |   |

|      | frame rate for YUV 4:2:0                                                        | 7 | 7 |

## Abbreviations

| HEVC           | $\mathbf{H} \mathrm{igh} \ \mathbf{E} \mathrm{ffeciency} \ \mathbf{V} \mathrm{ideo} \ \mathbf{C} \mathrm{oding}$ |  |  |

|----------------|------------------------------------------------------------------------------------------------------------------|--|--|

| AVC            | $\mathbf{A}$ dvanced $\mathbf{V}$ ideo $\mathbf{C}$ oding                                                        |  |  |

| IIT            | Inverse Integer Transform                                                                                        |  |  |

| $\mathbf{CTU}$ | Coding Tree Unit                                                                                                 |  |  |

| CB             | Coding Block                                                                                                     |  |  |

| $\mathbf{PU}$  | Prediction Unit                                                                                                  |  |  |

| $\mathbf{TU}$  | Transform Unit                                                                                                   |  |  |

| $\mathbf{QP}$  | $\mathbf{Q}$ uantization $\mathbf{P}$ arameter                                                                   |  |  |

| FPGA           | ${\bf F}{\rm ield}~{\bf P}{\rm rogrammable}~{\bf G}{\rm ate}~{\bf A}{\rm rray}$                                  |  |  |

| $\mathbf{RTL}$ | $\mathbf{R} egister \ \mathbf{T} ransfer \ \mathbf{L} ayer$                                                      |  |  |

| HLS            | $\mathbf{H} igh \ \mathbf{L} evel \ \mathbf{S} ynthesis$                                                         |  |  |

| MPEG           | Motion Picture Experts Group                                                                                     |  |  |

| JPEG           | $\mathbf{J} \text{oint } \mathbf{P} \text{hotographic } \mathbf{E} \text{xperts } \mathbf{G} \text{roup}$        |  |  |

| SIMD           | Single Instruction Multiply Data                                                                                 |  |  |

| HD             | $\mathbf{H} igh \ \mathbf{D} e finition$                                                                         |  |  |

To my family...

### Chapter 1

### Introduction

In 21<sup>st</sup> century, digital video applications are used widely in a huge variety of daily consumer products. Desktop PCs, laptops, cell phones, tablets, TVs and watches, are only a some small part of the high volume of applications that use video technology. However, video is not only used for entertainment purposes, but its objective span in many other fields. Video surveillance, video tracking and medicine are some of the aspects that video enhances our life, out of entertainment reasons. In previous decade, some of the previous applications were using analog video signal to perform their various processing tasks. In this thesis work, we are occupying only with digital video, since analog seems to be the predecessor of it, because most –if not all– of today video applications, are using digital technology.

Unfortunately, digital video has a huge volume of data that must be stored, processed and submitted, thus making imperative the compression of those big data. To realize the magnitude of video data, we quote that according to CISCO, "2/3 of the internet traffic, will belong in video by 2018" [3]. Video standards that are used in order to compress video data, remain an open field the last three decades, for both research and industry development and therefore they attract quite deliberation from research community. Progress in video compression technology, results in higher compression ratio, while retaining same perceptive quality –in terms of dB– from human eye. Every video compression standard is characterized as lossy compressor, because it cannot retrieves all primary information, although, this loss is not perceivable many times from human eye. Hence, each video standard incorporates itself many years of research, to attain better compression ratio while keeping video reconstruction quality in as much as possible standard levels. Although each new coming video standard has better performance in video coding, the complexity that is introduced in each of them constantly increases, because more and more complex algorithms are used to achieve improved results in compression. High Efficiency Video Coding (HEVC) or H.265-ITU is the new video coding standard, was introduced in 2013 that reduces bitrates at half in video streaming, in comparison with its predecessor the H.264/AVC (Advanced Video Coding) standard. The module which we are implementing in this work, is a part of HEVC decoder.

Video coding, except for the large data that has to manage, has also another characteristic that video implementations have to take into account before their design. Video coding/decoding can be considered as critical tasks, because of the high complexity of their algorithms and also the requirement that they need to be performed in a real-time constraint. Let us assume for instance that a video decoding application has to decode 30 fps –which is a typical frame rate– in a dedicated resolution, but it has performance only for 20 fps. One can be easily deduced from this assumption, video playback shall stalls, something that it is an undesirable effect. Consequently, video coding and decoding applications have to be implemented under certain specifications, regarding video resolution and frame rate, so as to achieve a minimum performance requirement.

Several video coding applications that have been developed so far, are implemented entirely either in software or in hardware. Software solutions, running on several types of processors, provide very flexible solutions for video coding in terms of design cost and portability, but they have poor performance for high content videos. Optimization can be performed in software solutions, exploiting hardware resources that are called "hardware accelerators", accelerating critical algorithms from video codecs. On the other side, exclusively hardware implementations, are very efficient in performing video coding tasks, achieving high throughput performance, while running in relatively low operating frequencies. Having although high design life cycle (design, simulation, debugging, verification, fabrication and testing), the disadvantages comes from design cost considerations, as concerning time-to-market value.

High Level Synthesis (HLS) concept, last yeas have been introduced more aggressively in industry, in order to overcome the high cost disadvantage of custom-hardware implementations. Describing an algorithm with a software level language, such as C/C++ is much easier than writing Hardware Description Languages (HDLs) and leads to quicker exploration of design space. Moreover, the simulation of C/C++ code is faster, because writing a C/C++ testbench to verify module's functionality, is much quicker than writing it into Verilog or VHDL. As a consequence and as already implied, HLS takes as input an algorithm in C/C++ and exports RTL (Verilog or VHDL). The RTL that is exported can be easily verified, only if we assure that C algorithm has proper functionality. Hence, an HLS tool guarantees that if C/C++ code works properly, then the exported RTL shall have the same behavioral functionality. Therefore, one needs to verify our design in RTL level, only write a piece of code in software that will verify the algorithm in software level. After that, a reference output has to be used for comparison and eventually if output results match, we do know that RTL will have the same behavioral functionality. Now, as concerning the performance of HLS implementations, it does not reach those of custom hardware RTLs, because RTL is outputted from a tool which follows standard templates and techniques. Nevertheless, the shorter time-to-market value that they provide, has special worth in industry, thus drawing inevitably as much attention from research community. Further details on HLS concept and Vivado HLS tool, are explained in Chapter 3 and in Chapter 6 we will ascertain where HLS performance stands among others.

Video codecs have several different modules that perform compression algorithms. In almost every video and image codec, there is a module that converts a block of pixels from its spatial representation to frequency domain, in order to evaluate a block of pixels according to its frequency components, so to reject those components that are not perceivable to human eye. The algorithm that is shouldered in performing this task, is called Integer Transform and is essentially the same with Discrete Cosine Transform (DCT) algorithm. One difference that exists, integer only numbers are now used replacing floating point arithmetic of DCT. DCT is based on Fourier's family transforms and its usage is not limited to video coding. Other applications such as video processing, computer vision, audio coding, speech recognition and communication, also use some kind of DCT algorithm. This thesis, conducts a HLS implementation, regarding the HEVC Inverse Integer Transform in particular, which is used in video decoding applications and converts frequency coefficients back to spatial domain. Further details are extensively discussed on this interesting algorithm in Chapter 3.

#### 1.1 Motivation

The number of video applications increases day by day for a variety of reasons, in many different aspects of our life. Also, the big amount of video data that are transmitted worldwide has to be reduced, for bandwidth saving reasons and so as to store video using less storage space. This problem of huge data gets worse, as the video content increases. Today video applications have the trend to use more and more higher resolutions and frame rates, in order to provide better visual quality to users, requiring as much less inherited distortion from compression process. HEVC, achieves best results among prior standards, regarding compression ratio for a standard video quality and definitely will be used in future video applications.

Adopting future applications HEVC standard, have to deal with a variety of issues that will be presented. The high complexity that have been introduced in this more sophisticated codec, is the major concern about HEVC adoption. According to a survey [4], HEVC decoder is roughly twice more complex than AVC decoder and HEVC encoder is expected to be several times more complex than H.264/AVC encoder. For this reason, future researches should propose optimized implementations in different platforms, thus supporting different target video contents according to the specifications of the target device. Software implementations, have low granularity levels for optimization, in comparison with the hardware ones. Some complex modules of HEVC have to be implemented using hardware accelerators, in order to enhance software implementations and to achieve demanding performance, for supporting high video contents.

Another incentive of this work, HLS, as already mentioned, has attracted a lot of attention in recent years from industry, because it provides shorter design cycle and eventually smaller time-to-market when compared to traditional hardware implementations, though it doesn't achieves the performance of custom RTLs. In other words, it provides great flexibility to explore hardware design space of a specific algorithm, in comparison with custom RTLs. Hardware accelerators that can be created with HLS tools, may be used from embedded systems, in order to enhance some critical parts of HEVC decoder and encoder. If a HLS implementation meets a certain performance requirement and the specifications of the circuit (area, power, delay) are also met, HLS could be a quick and efficient solution, for creating a hardware accelerator. Afterwards, this accelerator can be placed onto FPGAs or in embedded systems, or to create an ASIC hardware accelerator, which is going to enhance parts from software codecs. Hence, future video implementations may use HLS, so to explore more efficiently and rapidly the design space of the HEVC video codec implementation, which requires as much speedup as only hardware can provides.

Finally, the HEVC Inverse Integer Transform module that we got hands-on, is among the most complex modules of a video decoder and in HEVC decoder its complexity has further increased at 9% according to [4], due to the higher number of transform sizes. So, the acceleration of inverse transform is valuable, in order to accelerate the HEVC video decoder.

#### 1.2 Objective

◊ Design space exploration of the HEVC Inverse Integer Transform (IIT) algorithm using Vivado HLS tool, so to realize the pros and cons from different RTLs that tool derives and how HLS tool reacts on different directives and sources, describing the same algorithm.

- ◊ Deciphering the Vivado HLS tool, on how it manipulates latency on different architectures and data paths and how RTL architecture changes, forcing design to meet as much lower delay constraints.

- ◇ Throughput exploration analysis, so as to identify the different architectural plans for the algorithm, what throughput performance will they have. The outer purpose of this exploration, how a HLS tool is compared with other implementations in terms of throughput performance, such as software (x86), SIMD-accelerated software and custom-hardware RTL implementations.

- Realize when each different RTL solution becomes a critical component in a video decoder at the IIT module, thus finding the limits of HLS for decoding demanding video contents.

#### 1.3 Other Works

In this section we briefly discuss, what other works exist on video codec implementations, just to have an intuition about the different platforms and levels of implementation and also the results that other works provide.

Video coding is an open topic in research community and for this reason several papers have been published all those twenty five years that digital video had a great evolution. Research works can be distinguished into two major classes. The first category deals with proposals that induces on video coding field in terms of signal processing, thus determining algorithms and methods for improving compression. The second category deals with ways, to implement different video codecs, in different platforms and making different trade offs and optimizations. This thesis, is entirely related to the latter category, so we are going to focus on this, in literature review.

Several implementations have been proposed so far for every new standard. starting from pure software. up to custom hardware RTL. Software solutions mainly focus, either on supporting as much higher frame rates and resolutions, exploiting SIMD architectures on processors [5] and [6] or on performing complexity analysis [4], in order to give useful information in other researches that will use them. Other implementations are based on software, but gain a lot of performance from hardware features. Configurable microprocessors are such a solution because the Instruction Set Architecture (ISA) of those low-power microprocessors, can be extended with new custom instructions that will reduce total cycle effort and eventually shall increase performance or reduce power consumption. Various works have been proposed on this level for different video codecs such as [18] for H.264/AVC and [19] for HEVC.

The lower level of implementation is hardware RTL that is going to be used, either as a hardware accelerator onto an embedded system or as a module in a hardware video codec on FPGA or ASIC. Hardware implementations, due to the high design's complexity often are focusing in a specific module of a video codec and they provide different optimization results about performance, area and power. In general, hardware RTLs before turn in logic synthesis flow, can be distinguished as "custom-made", where architecture is designed from engineers or it can be exported from a HLS tool. Some good hardware references regarding some complex modules of HEVC are: [12] and [13] that they implement motion compensation module, [8], [9], [10] and [11] for integer transform module and [14], [15] and [16] that they are touching the difficult CABAC– entropy coding module of HEVC.

Hardware implementation proposals are countless, because video codecs are so complex applications and therefore they have a strong requirement in hardware, that their examination cannot be limited in this small section. We have to say that most of them, deal with a specific type of optimization and finally provide results to prove what they achieved. For instance, most hardware implementations that deal with throughput performance, aiming to reach the limits of highly demanding videos with upper limit the 8K @ 120 fps, keeping area and power as much low as possible.

Finally, except for custom-made RTLs, also have been proposed papers for implementing video codecs with HLS and now except to performance, area and power, man-month work is also used, in order to show how HLS tools can short time-to-market, thus showing its comparative advantage against custom RTLs. One HLS implementation for ASIC have been proposed regarding H.264/AVC codec [17] and to our knowledge this is the first effort that implements a module of HEVC with a HLS tool for FPGA.

#### 1.4 Thesis Structure

This thesis is organized in several different chapters, each of them analyzes a small division or a theoretic background of our work. The outline of the thesis is organized as follows:

- Chapter 2 provides some background theory about video coding and finally it briefly presents the more important video codecs that have been used so far, in video applications. The objective of this chapter, only show the general concept that video codecs inherent through years without give a lot of details about each video standard. The reader may understand some fundamentals about video coding theory, having read this chapter, so to be able to follow up some basic notions in rest parts from this work.

- Chapter 3 presents forward and inverse integer transform algorithms and all the mathematical background behind them, aiming primarily on how they work. Also, discusses how we get faster computational versions of the same algorithm and how they help in video coding process, which is a critical task.

- Chapter 4 initially clarifies the idea of High Level Synthesis for digital circuits and why it is so valuable in industry. Additionally, Vivado HLS tool is presented extensively on how it works and what options can be selected in order to explore hardware design space of an algorithm, meeting different latencies.

- Chapter 5 shows the way we set up the experiment and how we are using Vivado HLS tool to obtain results and to see as much aspects of total design space of algorithm.

- Chapter 6 contains all results and is structured with several different results in tables and diagrams, thus helping to understand better how tool reacts on different inputs. Finally, throughput performance is extensively explored for all the different configurations and is compared with other implementations.

- Finally, Conclusion further discusses on results, paying attention on the big picture of the problem and makes a total inference on this thesis. Alongside, future work discusses what other surveys may follow up this work.

### Chapter 2

### Video Coding Background

As briefly discussed in introduction, video data has a quite big volume that leads in two important problems. At first, a large storage space has to be reserved in order to store a video file and secondly when we want to transmit a video sequence, we require huge bandwidth to do so. To better understand this problem, we present a simple example. A typical video movie has length roughly 90 minutes. If assumed HD resolution and frame rate at 30 fps, then we have 1920x1080x30x3x90x60 bytes to store information for 3 color channels (e.g. RGB or YUV) with 8-bit color depth. Thus, we need about 900 GB (1 TB is a typical hard disk size) to store a typical Blu-Ray movie, without include audio data. Now, one needs to transmit this content in a live streaming application, send 1920\*1080\*3\*30\*8 bits per second, in order to see video without stall effects. This volume is translated into 1.5 Gb/sec, which requires huge bandwidth that is difficult to be found in daily consumer products. Finally, according to Cisco surveys, 2 of 3 data packets that are send every time over internet network, belong to video content. Consequently, we realize that video compression is a big deal in our digital epoch and how it directly affects our lives, because video is everywhere among us.

#### 2.1 Video in Signal Processing

Initially, compression algorithms can be distinguished in two categories according the type of elaboration that they perform on camera data. The two categories are called lossy and lossless compressors. Lossless compressors are those that reconstructed data on decoders side, are exactly equal with those that inserted as input in encoder side. Lossy compressors are those that reconstructed data, are slightly different from input, in that way that human eye cannot perceive it. Lossy compressors attain high compression rates and provide different levels of trade offs, between compression and reconstruction

quality. Every almost video standard that is used in products, utilizes a lossy codec, thus attaining great compaction results. In next sections, we are showing the basic stages that modern video codecs utilize, in order to compress video content.

A still image, is represented as a 2-D signal –in terms of signal processing– with one dimension denoting color change in horizontal direction and the other dimension, color change in vertical. In this approach, video is a 3-D signal, with 3<sup>rd</sup> dimension being the temporal factor, to wit the color change between different frames in time, because video is actually a sequence of frames or still images. Video and image compression standards, exploit spatial and temporal correlation from frames, in order to compress data. If we carefully pay attention in ordinary images, we will realize that some parts of the image, have about same intensities with others and therefore image signal has a spatial correlation between different regions in image. In video, except for the spatial correlation in one frame of it, different neighboring frames are very similar between them and so video has a temporal correlation as well. Realizing this correlation, prediction algorithms can be performed in video codecs, so to predict some parts of video signal, thus do not requiring to send all information in decoder's side. Even more, video and image codecs exploit one more attribute that is based on a property of human's eye. Human eye cannot perceive high frequency changes in color, similar to ear which has a restricted bandwidth in acoustic frequencies. So, rejecting some of the high frequency components, we reduce information, without eye realize this degradation. In next Section 3, all these notions about frequency components, will be clarified further, to see how they are translated into signal processing.

#### 2.2 Typical Compression Diagram

All renowned video compression standards that have been introduced so far, are based on a certain structure with same stages as shown in Fig. 2.1. The general scenario is the following. At first, a frame is declared as an intra or inter frame. In the former case, only spatial correlation is utilized to remove content redundancy, while in latter case, both spatio-temporal may be used. In either cases, an arrived frame get stored in frame buffer and is divided into small blocks of pixels. Each of the following stages from now on, refers to block operations. The first frame of video, must be declared as an intra (I-frame), because there aren't previous frames to make predictions, so it is encoded without having references from other frames. In Subsection 2.2.1 we provide further details on intra prediction. Other frames except intra, can be declared as P or B frames. P frames, use temporal prediction from previous frames, in order to reduce temporal redundancy, while Bi-directional frames are capable of using both previous and future frames as reference, thus exploiting correlation from both future and past frames. Of course, future reference frames –from which B-frames take prediction– have to be decoded beforehand, so current B-frame have in memory the reference block of pixels, so to perform prediction – Fig. 2.2. Refer to Subsection 2.2.2 for further details on inter prediction.

FIGURE 2.1: Architectural diagram of a typical video codec [44]

FIGURE 2.2: A group of pictures with I, P, B frames [39]

After removing redundancy for both intra and inter cases, we have the error that is

called residual of pixels or distance from prediction. The predictors from inter prediction are called motion vectors. Prediction error, will be send for transformation and quantization, in order to retain only low frequency components of error, thus requiring to send fewer information. Quantization process, introduces the lossy notion, because for those coefficients that have low energy in frequency domain, they will become zero. In this step, we have lost information, because decoder cannot retrieve zero coefficients in their primary value, before quantization step. First video standards, such as MPEG-1 and 2, that haven't exploited intra prediction, utilize transformation in a block of pixels -not in residual error- for I-frames. This concept that transforms a block of pixels without prediction and discard high frequency components, is used in image compression from JPEG standard (see Fig. 2.3). We have to say here that there are video codecs such as Motion-JPEG that do not exploit neither spatial nor temporal correlation. All frames are encoded as still images (JPEG coding is performed in each one) and only by rejecting high frequency components in block of pixels, we achieve some compression ratio. After all this procedure, the final stage of a video encoder in called entropy coding (Huffman, CAVLC, CABAC). The entropy module, undertakes the task to compress information according with the likelihood of each syntax element, which can be one of the following: motion vector, quantized coefficient, intra predictor, various indices and flags. Entropy encoder operates in bit level, using small length codewords for symbols

with high likelihood and large codewords for more infrequent symbols.

FIGURE 2.3: Basic stages of JPEG codec for still image compression [40]

Decoder, have to follow same steps in reverse order, starting with entropy decoding and so on. Encoder, have to decide about several parameters in order to encode a video, but decoder needs only to follow what encoder have decided on. This scenario and the "communication" between encoder and decoder, is indicated via encoded bitstream. Hence, video encoders are considerably more complex than decoders, due to many decisions that they have to try. Also, some high complex algorithms, such as motion estimation, performed in encoder's side, so they increase further the computational complexity of encoder. A very strong feature that is met in later video standards, is some filters from image and video processing fields, that their task is to remove blocking artifacts that video codecs introduce, due to the block-based structure that they have. The in-loop filter or else de-blocking filter, applies a filtering in all vertical and horizontal edges, thus removing blocking artifacts. Other such filters that have been introduced in HEVC standard like Sample Adaptive Offset (SAO) filter [20], gives an offset in pixel values, after reconstruction process in decoder side. Visual results in order to compare differences are illustrated in Figures 2.4 and 2.5.

FIGURE 2.4: Deblocking Filter [41]

FIGURE 2.5: Sample Adaptive Offset (SAO) filter [20]

#### 2.2.1 Spatial Correlation

Spatial correlation, exploited at first in H.264/AVC standard. Until then, only temporal was exploited by video codecs and so I-frames (intra frames or frames without temporal prediction) were using only transformation and quantization in block of pixels, in order to reduce input information. The basic idea is that in many frames, there are some regions that can be predicted from other already decoded. Therefore, some blocks can be predicted from other co-located blocks, according to a certain direction. Direction,

indicates the algorithm that we take pixels from up and left blocks and how we use them in order to best predict pixels in our current block. Let us assume that a quite spread area into one frame has about the same color information. Then, it is easy to predict some blocks from other neighboring already decoded blocks, just by coping pixel information either in horizontal or in vertical direction. Of course, there will be an error from prediction that is going to be transformed and quantized. Fig. 2.6, shows the nine different possible directions for intra prediction that is maintained in AVC codec. We can see vertical prediction (just copying information from upper adjacent block), horizontal (from left block), diagonal predictions with different angles and finally DC prediction that finds the mean, between the two rows of pixels. In real life, most of real objects have vertical correlation, so we can notice that respective mode has number zero, because this is the number that has the smallest entropy information in a video codec. Hence, modes with high likelihood are represented by numbers with small entropy in a video codec, as long as it is a rational practice, in order to achieve high compression.

FIGURE 2.6: Possible directions for intra prediction in H.264/AVC standard [2]

As long as a frame is declared as an I-frame in the GOB, then its blocks proceed for finding best intra prediction mode. First intra block (upper-left in frame) that has no predictors is the only that in encoded just by transformation and quantization on pixel intensities, like to JPEG. A greedy approach, it could be this: try all possible directions and find what is this with the smallest prediction error. Although, some early termination algorithms can be utilized, so under a threshold condition according to Mean Square Error (MSE) value, prediction is over. Finally, intra prediction can be used also from inter frames, because if one block cannot be predicted well from other frames, then an intra block may be used to give better prediction. If so, this block in the inter frame, has to be declared as intra via some flag, so decoder knowing the predictors, in the reconstruction process of the block.

#### 2.2.2 Temporal Correlation

Temporal correlation is a common attribute in video sequences and thus it is exploited largely from video codecs, for reducing the coding information. The third dimension of a video signal is the temporal factor and as already mentioned, different frames in time have a strong correlation between them. Temporal correlation is occurred in video signals, due to the short time that frames are captured from the camera. Capturing a video at 30 fps for instance, means that a new frame is captured every 33 millisecond. It is rather straightforward to see that those frames, shall have a strong relationship between them and temporal prediction can be used to predict each other.

A simple approach of such a procedure is this: a current block that is going to be predicted is searched in different frames in a certain search range and the frame with the smallest error, is declared as best. The motion vector that refers to the best block, is transmitted to decoder's side. Motion vector, is a vector in (X, Y) format that declares how far from current block we have to go, in order to find the best predicted block. Additionally, an index is encoded in bitstream, which declares from which frame we have used the block for prediction. In Bi-directional frames, there is also option to find two prediction blocks, from different temporal frames and find their average or weighted average with some pre-defined weights, thus constructing the prediction block that will be used to calculate the prediction error.

The module that elaborates the previous demanding task, is the popular motion estimation algorithm, which is the most complex algorithm in a video encoder, since it takes many cycles to find the best motion vector. The greedy algorithm or else the full search, takes all possible blocks in a specific search range and finds the best error between them in terms of MSE. As we can realize, operations are performed pixel by pixel for the entire block, thus making motion estimation a computational demanding algorithm. Some researchers such as [22], have proposed different schemes for early termination, making trade-offs, between time for prediction accuracy. After motion estimation is accomplished, a motion vector, an index and a residual block (prediction error), are yielded from this module. Fig. 2.7 illustrates motion estimation between two frames.

FIGURE 2.7: Motion estimation algorithm. Finds best match block in different temporal frames. Motion vector indicates how far from current position best block is located [42]

In typical videos, the very smooth motion that exists frame by frame, induces another attribute that video codecs take into account. In actual video sequences, there is a big probability that motion doesn't matches so well on integer pixel distance. What we are trying to say, many times block's motion, doesn't match with integer pixels, because motion goes in sub-pixel distances and therefore integer block options, don't give as much accurate prediction as it could, if sub-pixel values were exploited.

FIGURE 2.8: All possible sub-pixel values that can be found in quarter distance. Different filters are used to obtain values in each position [43]

Motion in sub-pixel values can be captured only by moving in distance lower than pixel. Of course, a prediction block in half pixel distance is not in memory, because only integer pixel values from already decoded frames are in there. So, in order to find new pixels in sub-pixel distance, interpolation process has to be performed, with input the integer pixel values from integer part of motion vector. Most of video codecs are using quarter pixel interpolation values, thus enabling accuracy at quarter pixel distance. Fig. 2.8, shows all quarter pixel positions that can be found from already decoded integer values. Each new video codec, adopts new techniques on interpolation method. As the accuracy of interpolation goes higher, it leads to better coding efficiency because energy of motion's prediction error gets decreased.

| Year | Standard   | Applications   | Bitrate (Mbps) (720x480) |

|------|------------|----------------|--------------------------|

| 1993 | MPEG-1     | VCD            | 7                        |

| 1995 | MPEG-2     | DVD            | 6                        |

| 1999 | MPEG-4     | DivX, XVid     | 5                        |

| 2003 | H.264/AVC  | BluRay, DVB-TS | 4                        |

| 2013 | H.265/HEVC | next of H.264  | 2                        |

TABLE 2.1: Popular video standards that have been used in video applications

#### 2.3 Video Standards

Video standards through years, aim on better coding efficiency, so to delivering video at lower bitrate, trying to retain a good quality in video content in terms of PSNR. Peak Signal to Noise Ratio (PSNR) is a metric that evaluates how much faithful is the reconstructed video sequence after the video decoding process. PSNR, in terms of signal processing, is the amplitude of true video signal in respect to noise. Noise in video is declared as the MSE, between pre-encoded and post-decoded frames. So, each new video coding standard, aims on achieving better PSNR for same bitrate or reduced bitrate for same PSNR. In next subsections 2.3.1, 2.3.2, 2.3.3 and 2.3.4, we shortly present some of the most popular video standards that have been used in daily consumer products so far 2.1, via architectural diagrams and their key innovations.

#### 2.3.1 MPEG-1/2

MPEG-1 is the first video codec that exploited temporal correlation using motion estimation techniques. I-frames, don't have spatial prediction and are coded like JPEG, only using transformation and quantization to reduce information before entropy coding. P and B frames, use motion estimation in order to find best prediction block and in these frames, only error of prediction is sending to decoder, along with motion vectors. MPEG-1, utilizes Huffman algorithm [21] for the entropy coding stage. MPEG-2, has small differences when compared to MPEG-1. Different scanning order of quantized coefficients, standard half-pel motion estimation and support for other color formats, are some of the small difference between the two standards. A typical diagram of an MPEG-1/2 video codec, is depicted on Fig. 2.9.

FIGURE 2.9: Typical diagram of an MPEG-1/2 encoder [44]

#### 2.3.2 MPEG-4

MPEG-4 is the most interesting video standard from academic and research aspect. The video coding process, differs a lot in comparison with other standards, because everything is consisted from multimedia objects and background. True objects, faces and mesh can be considered as multimedia objects and also transparency of each object, can be used in coding process. Scalability of video content is used as well, either spatial or temporal, thus enabling video delivery in different bandwidths and qualities. MPEG-4 supports now color bit-depths from 4 up to 12 bits, in comparison with MPEG-1/2, where only 8-bit was permitted. Quarter pixel accuracy in interpolation, is now an option that leads to better coding efficiency. Besides, there are schemes for prediction on DC and AC coefficients, among adjacent transform blocks. Finally, a great advantage of MPEG-4, is the error resilience tools and techniques that utilizes, in order to be more robust in errors that are introduced in video streaming over networks.

#### 2.3.3 H.264/AVC

H.264 or Advanced Video Coding (AVC) is also known as MPEG-4 part 10, because it was developed as an amendement of MPEG-4 standard. Here, coding methods return back into block-based structures, without having any more notions, such as multimedia object, background and transparency.

Spatial correlation is exploited for the first time and is called intra prediction, following what we described on Subsection 2.2.1, giving up to four times better compression in I-frames. Quarter pixel motion accuracy, is now a standard method for more accurate motion prediction, thus providing better coding efficiency. A 6-tap sync-based FIR filter, is now used for half pixel values; for quarter values, a bi-linear filter is used, taking half-

and integer-pixel values as inputs. Blocks of pixels, have also greater degree of freedom, for partitioning into smaller blocks, giving more accurate prediction. Additionally, DCT transform has altered in integer transform with the same properties, but using now only integer arithmetic, avoids rounding errors between encoder and decoder. Moreover, a deblocking filter is used for the first time in order to alleviate blocking artifacts as explained in Section 2.2. Finally, except for Huffman entropy encoder, now there is option for CABAC, which has about 15% better compression performance, since it is a superior entropy algorithm than Huffman, in terms of coding theory.

FIGURE 2.10: Typical diagram of an H.264/AVC codec [2]

#### 2.3.4 H.265/HEVC

The latest video standard is the H.265 or High Efficiency Video Coding (HEVC), which is the AVC's predecessor and is expected to be adopted in future multimedia products, because it reduces bitrates at half compared to its predecessor. This directly implies that better video quality can be delivered over the same bitrate or for the same video quality, bitrate can be halved.

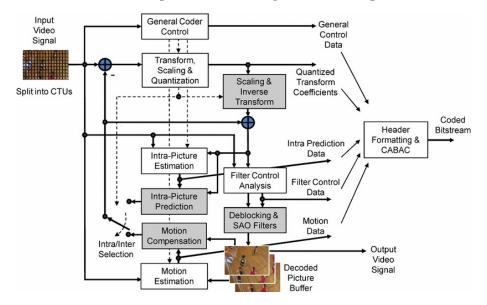

HEVC has further improved the block-based video coding structure that existed so far, adopting a quad-tree structure called Coding Tree Unit (CTU) that starts from the largest block of pixels (typically 64x64) and recursively splits into smaller blocks for prediction (Prediction Unit - PU) and transformation (Transform Unit - TU). Moreover, blocks not only allow symmetric partitions but asymmetric ones are also utilized, allowing for a better match with actual visual-object shapes, thus reducing motion residual energy [23]. Interpolation filters, has quarter-pel accuracy with longer tap FIR filters for improved prediction. AVC was using only 4x4 and 8x8 integer transform sizes, while in HEVC, 16x16 and 32x32 have been introduced, enabling higher energy compaction in high resolution videos. Here, CABAC is standard algorithm for entropy coding module and also besides to deblocking filter, SAO [20] is also used, to ameliorate the quality of reconstructed frames. The diagram of HEVC is presented in Fig. 2.11.

FIGURE 2.11: Typical diagram of an H.265/HEVC codec [1]

## Chapter 3

# **HEVC** Inverse Integer Transform

HEVC integer transform, is the module that undertakes the task to change a block of samples from spatial to frequency domain. Therefore, forward integer transform is used by encoder, in order to evaluate frequency components of a block of samples and how much energy has each of them. Inverse integer transform, is the inverse procedure that takes coefficients and converts them back to spatial domain, thus reconstructing pixel information at decoder's side. The integer transform module, uses essentially the same algorithm with Discrete Cosine Transform (DCT), but it manipulates only integer arithmetic instead of floating point, so to avoid rounding errors that leads on a slight mismatch between encoder and decoder. Video standards up to MPEG-4, use DCT instead of integer transform, but after that, only integer transform is used.

There are several transforms in general, out of DCT, that are used in order to decompose samples from spatial to frequency domain. Karhunen-Love Transform (KLT) [24] is a unitary and orthogonal transform that attains best energy compaction among all, but its high complexity, constraints the implementation for real-time applications. Discrete Fourier Transform (DFT) [25] is a separable transform for different dimensions. It is also a unitary and orthogonal transform that is used to decompose the original data into its sine and cosine components. DCT transform now, belongs to Fourier-family transforms, because it is essentially the even part of a DFT, so it is also a separable transform that we are going to analyze in this Chapter. Hadamard Transform [27] is a simple low complex algorithm, but it achieves moderate energy compaction and is used from video codecs in very special cases. Finally, the Discrete Wavelet Transform (DWT) [30] is a unitary, orthogonal and separable transform that is usually applied to the whole input data (or large parts of it, called tiles) but typically not to small data blocks like all the previous transforms. This Chapter is organized as follows: Section 3.1, shows the basics about DFT algorithm, because DCT and therefore integer transform, is based on it and is going to help in understanding how DCT was created. Section 3.2 shows the DCT forward and inverse algorithm that is used in many different video and image compression standards. All algorithms are based on 2-D transforms, because video standards are using 2-D transforms for the block of pixels, thus capturing both horizontal and vertical signal change. Final Section 3.3 shows how a Fast Fourier Transform (FFT) is constructed from DFT and in respect to this method, DCT fast version is deployed as well, which is utilized in every real-time video application.

### 3.1 Discrete Fourier Transform (DFT)

As previously mentioned in this chapter, DFT is a separable orthogonal transform, that converts input data into its sine and cosine components. 2-D algorithm is the same as two 1-D transforms in row, with the first dimension taking into account horizontal frequencies and the second the vertical ones. Calculation of 2-D forward and inverse DFT is based on Equations 1 and 2 respectively.

$$y(k,l) = \frac{1}{N} \left( \sum_{m=0}^{N-1} \sum_{n=0}^{N-1} x(m,n) e^{-\frac{2\pi i (km+ln)}{N}} \right)$$

(1)

$$x(m,n) = \frac{1}{N} \left( \sum_{k=0}^{N-1} \sum_{l=0}^{N-1} y(k,l) e^{\frac{2\pi i (km+ln)}{N}} \right)$$

(2)

In either equations, x(m, n) represents a block of pixel data which is a 2-D signal and y(k, l) the output coefficients, each of them representing the energy of a basis frequency function, according to its position. The y(0, 0) coefficient is called DC, because it represents the energy of zero frequency in both horizontal and vertical direction. So, if all pixels in a block have equal values, then all coefficients except for DC become zero and DC's energy maximized, according of course to the sample's intensities. Other coefficients than DC, are called AC. Figure 3.1, shows basis functions for each different frequency component. We can see DC component in upper left corner and also how horizontal signal frequency increases, while moving left-wise and how vertical increases for down-wise scanning.

FIGURE 3.1:  $8 \times 8$  DFT basis functions [28]

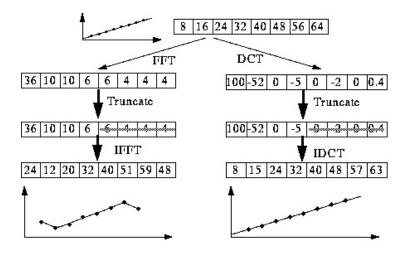

It is straightforward to see someone that DFT produces complex coefficients, with real and imaginary parts, to wit magnitude and phase, The storage and manipulation of these complex values it is a disadvantage when compared to other available transforms, e.g. the DCT which use real and not complex numbers. It is a much better solution than DFT for real implementations, achieving also better energy compaction for highly correlated signals, such as image. Higher energy compaction means that with fewer coefficients we reconstruct signal with less error than DFT. The main reason DCT is used in video codecs, is that a lot of coefficients will be discarded in quantization process and therefore we want to reconstruct as better as possible the signal with fewer coefficients. Figure 3.2, illustrates the main difference between DFT and DCT, as concerning energy compaction and reconstruction with fewer coefficients.

FIGURE 3.2: DFT vs DCT in terms of signal reconstruction [29]

## 3.2 Discrete Cosine Transform (DCT)

The Discrete Cosine Transform (DCT) is a unitary and orthogonal transform, conceptually rather similar to the DFT, but only using real numbers (and not complexes any more). For a NxN block of samples, the forward 2-D DCT is defined by Equation 3

$$y(k,l) = \frac{4C(k)C(l)}{N^2} \left( \sum_{m=0}^{N-1} \sum_{n=0}^{N-1} x(m,n) \cos \frac{(2m+1)k\pi}{2N} \cos \frac{(2n+1)l\pi}{2N} \right)$$

(3)

and the inverse 2-D DCT is defined by 4.

$$x(m,n) = \left(\sum_{m=0}^{N-1} \sum_{n=0}^{N-1} C(k)C(l)y(k,l) \cos\frac{(2m+1)k\pi}{2N} \cos\frac{(2n+1)l\pi}{2N}\right)$$

(4)

$$C(\omega) = \begin{cases} \frac{1}{\sqrt{2}} & \omega = 0\\ 1 & \omega = 1, 2, \dots, n-1 \end{cases}$$

(5)

Like the DFT, since the DCT is also a separable transform, it can be represented as the product of two 1-D DCTs; the first for the 1-D horizontal and the second for the vertical. The 2-D basis functions of DCT are presented in Fig. 3.3. Since the cosine function is real and even, i.e.,  $\cos(x) = \cos(-x)$  and the input signal is also real, the inverse DCT generates a function that is even and periodic in 2N, considering N the length of the

original signal sequence. In contrast, the inverse DFT produces a reconstruction signal that is periodic in N.

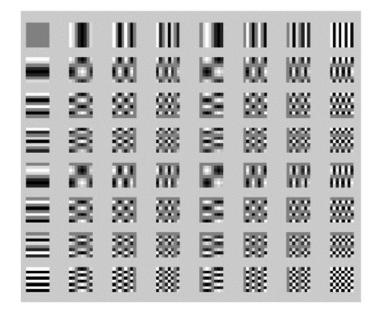

FIGURE 3.3:  $8 \times 8$  DCT basis functions [28]

In other representation, DCT can be declared also as a multiply of two 2-D matrices, each one for 1-D stage of transform. The basic algorithm –not the fast version– that is incorporated in video codecs, is essentially the product of three 2-D matrices: two of them contain the basis of DCT and the third represents the input signal (block of pixels). Equation 6, shows the procedure of a 2-D DCT transform. B is the NxN matrix with transformed coefficients, A is the input NxN pixels or residuals and U the NxN basis components of DCT. We can see briefly that inverse transform procedure is this: a block of coefficients is arrived and 1-D transform is applied in each of its rows capturing horizontal frequency. After that, coefficients from first stage will be the input after transposition of the second step of transform. The output result from the second transform, is the 2-D transform of a NxN block of pixels.

$$B = UAU^T \tag{6}$$

Integer transform of HEVC is essentially the same algorithm with DCT, but U matrices contains only integer values –not real numbers– making an approximation to basis functions. As we said, DCT and therefore integer transform is an orthogonal transform and this is the reason that HEVC contains four such transforms the 4x4, 8x8, 16x16 and

32x23. These four different transforms apply usually to residual of pixels, so to convert them in frequency domain and by quantization, to discard high frequency components of error. The bigger size of transform is used, the better energy compaction is achieved for large blocks of pixels. A typical 4x4 block of pixels-residuals, can be described by 2-3 coefficients if prediction is accurate and error has low energy. We can see that sending three coefficients, we can reconstruct sixteen pixels. Now, a typical 32x32 block can be described by ten about coefficients, thus letting to retrieve 1024 pixels sending only ten coefficients and that is why better energy compaction is achieved.

### **3.3** Fast Transform Implementation

Having seen the DCT algorithm through equations, it is easy to realize that in order to transform a NxN block, a computer have to perform  $N^2$  operations (multiplications and additions) for the 1-D stage and one more time the same computations for the second stage (2-D). So, the complexity of DCT via matrix multiplications is  $O(N^2)$ , which is a prohibited complexity for real-time applications. Especially in HEVC standard, the complexity would be very high for the two large transforms (16x16 and 32x32), thus making difficult the optimization of integer transform module.

Several algorithms have been proposed all those years which reduce DFT-family algorithm's complexity. The most famous technique-algorithm was carried out from Cooley-Tukey and the relevant paper was published in 1965 [36]. This is a divide and conquer algorithm that recursively breaks down a DFT of any composite size N = N1N2, into many smaller DFTs of sizes N1 and N2, along with O(N) multiplications. The best known use of the CooleyTukey algorithm, is to divide the transform into two pieces of size N/2 at each step, (also known as radix-n, where n are the steps) and is therefore limited to a power-of-two sizes, but any factorization can be used in general. The two pieces of N/2 transforms, are consisted from the even entries for the first transform and the odd ones for the second divided transform.

Figure 3.4, shows an 8-point DFT with a radix-4 scheme, according to CooleyTukey's algorithm, that splits in smaller transforms up to 2-point DFT. All these diagrams are called butterfly schemes due to their shapes. The butterfly scheme of the 2-point DFT, is illustrated in Fig. 3.5. Now regarding the total complexity of the fast algorithm, it is easy to see that each N-point or each radix, requires N multiplications and additions. Having  $\log N$  stages for each fast implementation, the total complexity for the 1-D transform becomes  $N \log N$  and  $2N \log N$  for the 2-D transform, since it is separable. By converting a DFT algorithm in FFT, one we achieve, reduce the order's complexity from  $O(N^2)$  to  $O(N \log N)$  which is a very good performance for an algorithm that

will be incorporated into a real-time application and also it enhances significantly the performance of larger transforms such as 16x16 and 32x32. The complete fast DCT diagram on which our implementation is based on is depicted on Fig. 3.6.

FIGURE 3.4: Cooley-Tukey algorithm with radix-4 [26]

FIGURE 3.5: Radix-2 bytterfly [26]

We shown how the DFT algorithm can be modified into FFT, using some techniques in order to reduce its complexity. On exactly the same way, DCT transform is also optimized in order to obtain a version of algorithm that can be used from demanding applications. For DCT and so for integer transform, Chen's algorithm [38] is utilized in order to create a more efficient in terms of complexity algorithm that can be used from video encoding-decoding applications. In HM reference software, the standard algorithm that is utilized for integer transform, is based on Chen's algorithm which contains the 4x4, 8x8, 16x16 and 32x32 transforms. The multiplicands are contained in separate arrays for each size of transform and as we have already said, they are integer approximations of DCT's ones.

FIGURE 3.6: Signal flow graph of Chens fast factorization for 4x4, 8x8, 16x16 and 32x32 transforms [38]

# Chapter 4

# High Level Synthesis on FPGA

The growing capabilities of silicon technology and the increasing complexity of applications in recent decades, have forced design methodologies and tools to move in higher abstraction levels. Raising the abstraction level and accelerating automation of both the synthesis and the verification processes, has allowed designers to explore the design space more efficiently and rapidly (shorter time-to-market). Essentially, the most valuable feature of HLS and that is why industry have started to explore further, is the short time requirement for developing an algorithm into hardware including synthesis and verification processes. As it is already known, an algorithm can be mapped onto a hardware design with different architectural ways considering performance, area and power. This is called design space of a certain algorithm, changing several hardware architectural options, in order to make different Register Transfer Levels (RTLs) designs of a specific algorithm. HLS tools, are very efficient in this approach, because given an algorithm description and only changing directives, different RTL designs are produced. Custom RTL designs, are written by hand with Hardware Description Languages (HDL) code (Verilog, VHDL), so we have to write down a new code each time, if we want to explore a different RTL design. Hence, HLS maintains more efficiency for exploring design space, spending fewer time than classic logic synthesis approach.

In this chapter, we initially present an introduction Section 4.1 about HLS, in order to clarify what is the general concept of HLS and what means "raising the abstraction level". After that, in Section 4.2, we briefly introduce Vivado HLS tool, which is a tool for HLS on FPGAs and is available from Xilinx corporation. We explain a few things about tool's structure and how it manipulates designs, according to the directives that are inserted. The most useful directives of Vivado HLS, are presented in Subsection 4.2.1, since some of them were used in our experiment. Finally, in Subsection 4.2.2 we explain how Vivado controls latency, according to the directives that inserted.

### 4.1 Introduction