Department of Computer & Communication Engineering

# Wirelength and timing driven standard-cell placement

Master of Science thesis

Msc. Student: Eirini Psirra – Ειρήνη ΨύρραProfessor: Georgios Stamoulis – Γεώργιος ΣταμούληςAssist. Professors : Nestoras Eumorfopoulos – Νέστορας ΕυμορφόπουλοςPanagiota Tsompanopoulou – Παναγιώτα Τσομπανοπούλου

#### 2/1/2013

Institutional Repository - Library & Information Centre - University of Thessaly 24/04/2024 19:21:50 EEST - 18.117.97.238

## Acknowledgements

It is a pleasure to thank all those who made this thesis possible. First of all I would like to thank Professor George Stamoulis for being a great supervisor. His ideas and tremendous support had a major influence on this thesis. His academic and working experience has been invaluable to me and his attitude made me more self-confident.

I would also like to thank assistant Professors Panagiota Tsompanopoulou and Nestoras Eumorfopoulos for their support and remarks on their subject of interest on this thesis. Additionally I would like to thank associate Professor and current deputy chairman of the department John Moontanos for his help in every part of my Msc studies and projects.

I am very grateful to Professor Christos Sotiriou for training me in commercial synthesis, simulation and physical design tools. Thus, I examined the full back end flow of the physical design. I could also compare results of my placement tool. The most important, because of him I gained five month working experience during my studies.

I would like to pay tribute to my colleagues at lab "E5" of my department in University of Thessaly. I appreciate the exchange of ideas and their help in every part of my thesis. Namely I would like to thank Dr. Antonios Dadaliaris and PhD candidate Konstantinos Daloukas.

Special thanks to Msc student and my coworker in this thesis John Arvanitakis. The first part of this thesis is a cooperation of us both. We have worked as a team in many projects, including this thesis. I would like to thank him for the well-operating with always great results, support motivation in educational development, encouragement and all the help all these years.

I feel much obliged to Sung Kyu Lim. He kindly gave us permission to use some implementation examples of placement algorithms of his book "physical design automation".

Also I would like to express my appreciation to my friends, for their love and support in all my decisions. Close or miles away, they always are a helpful hand, a funny picture in my memory or a shoulder to cry.

At the end I would like to thank my family. I would like them to know that I imagine, share, care, hope, love and appreciate because they taught me to.

## Contents

| Part | 1: Wire | elength driven placement                           | . 4 |

|------|---------|----------------------------------------------------|-----|

| 1.   | Intro   | oduction                                           | . 5 |

| 2.   | Prel    | iminaries                                          | . 6 |

|      | 2.1     | Definitions                                        | . 6 |

|      | 2.2     | Computer Aided Design                              | . 7 |

|      | 2.3     | Electronic Design Automation                       | . 8 |

|      | 2.4     | Design Flow                                        | . 9 |

|      | 2.4.1   | Front-end flow                                     | 10  |

|      | 2.4.2   | Back-end flow                                      | 11  |

| 3.   | Plac    | ement                                              | 15  |

|      | 3.1     | The Placement problem formulation                  | 15  |

|      | 3.2     | Classification of placement algorithms             | 17  |

|      | 3.3     | Net metrics                                        | 19  |

|      | 3.3.1   | Lk-norm induced distance metric                    | 20  |

|      | 3.3.2   | Rectilinear Steiner Tree and Minimum Spanning Tree | 20  |

|      | 3.3.3   | Clique                                             | 20  |

|      | 3.3.4   | Star                                               | 21  |

|      | 3.3.5   | Bounding Box                                       | 22  |

|      | 3.4     | Minimizing Quadratic Netlengths                    | 23  |

|      | 3.4.1   | Preconditioning                                    | 23  |

|      | 3.5     | Minimizing Linear Netlength                        | 24  |

| 4.   | Plac    | ement methods and Algorithms                       | 25  |

|      | 4.1     | Global placement Methods                           | 25  |

|      | 4.1.1   | Graph partitioning                                 | 25  |

|      | 4.1.2   | Analytic and Relaxation Based Placement            | 31  |

|      | 4.1.3   | Force-Based Methods                                | 32  |

|      | 4.1.4   | Simulated Annealing for Global Placement           | 33  |

|      | 4.1.5   | Clustering                                         | 33  |

|      | 4.2     | Final placement Methods                            | 37  |

|      | 4.2.1   | Legalization                                       | 37  |

|      | 4.2.2   | Local improvement                                  | 38  |

|      | 4.2.3   | Simulated annealing                                | 39  |

|      | 4.2.4   | Greedy Approaches                                  | 40  |

| 4.3                             | Placement Algorithms                      | 41 |  |  |

|---------------------------------|-------------------------------------------|----|--|--|

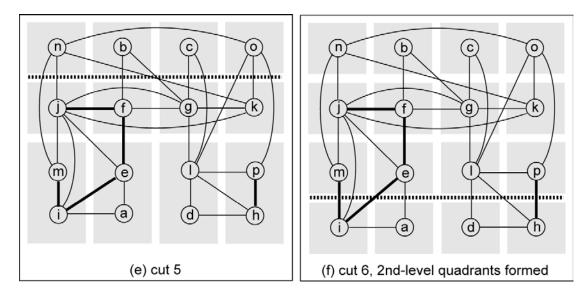

| 4.3.1                           | Min-cut                                   | 41 |  |  |

| 4.3.2                           | Gordian                                   | 43 |  |  |

| 4.3.3                           | TimberWolf                                | 46 |  |  |

| 4.3.4                           | Domino                                    | 48 |  |  |

| 4.3.5                           | FastDP                                    | 49 |  |  |

| 4.3.6                           | Proud                                     | 50 |  |  |

| 4.3.7                           | The Vygen's Method                        | 50 |  |  |

| 4.4                             | Performance driven Placement              | 51 |  |  |

| 4.5                             | Trends                                    | 52 |  |  |

| 5. Win                          | relength driven placement                 | 53 |  |  |

| 5.1                             | Preparation                               | 53 |  |  |

| 5.1.1                           | Input files                               | 53 |  |  |

| 5.1.2                           | EDA Tools                                 | 53 |  |  |

| 5.1.3                           | Output                                    | 53 |  |  |

| 5.2                             | Levelization – A wirelength driven placer | 54 |  |  |

| 5.2.1                           | Levelization technique                    | 55 |  |  |

| 5.2.2                           | Level placer                              | 56 |  |  |

| 5.2.3                           | Legalizer                                 | 58 |  |  |

| 5.2.4                           | Detail placer                             | 59 |  |  |

| 5.2.5                           | Synopsys                                  | 60 |  |  |

| 6. Ber                          | nchmark Circuits                          | 61 |  |  |

| 7. Exp                          | perimental Results                        | 63 |  |  |

| Part 2: Tim                     | ning driven placement                     | 66 |  |  |

| 8. Tin                          | ning driven placement                     | 67 |  |  |

| 8.1                             | Introduction                              | 67 |  |  |

| 8.2                             | Gate and wire delays                      | 68 |  |  |

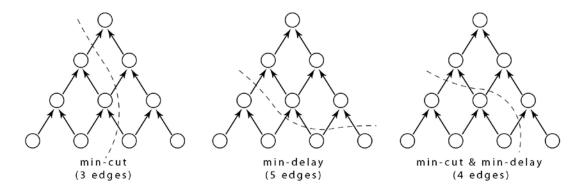

| 8.3                             | Timing driven partitioning                | 71 |  |  |

| 8.4                             | Timing driven placement                   | 73 |  |  |

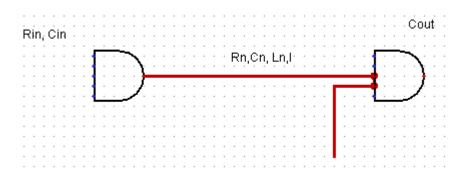

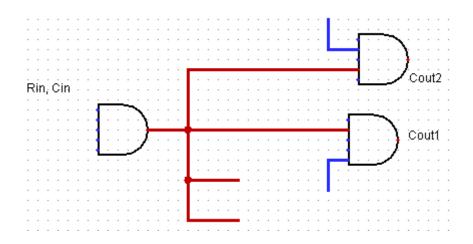

| 8.4.1                           | Net-based approach                        | 74 |  |  |

| 8.4.2                           | Path based approaches                     | 76 |  |  |

| 8.5                             | Other delay optimization techniques       | 77 |  |  |

| 8.6                             | Congestion versus timing closure          | 82 |  |  |

| Part 3: Future Work and Sources |                                           |    |  |  |

| 9. Future Work                  |                                           |    |  |  |

## Part 1: Wirelength driven placement

Institutional Repository - Library & Information Centre - University of Thessaly 24/04/2024 19:21:50 EEST - 18.117.97.238

## 1. Introduction

The research on the field of digital circuits through the decades, from the construction of the first computer to nowadays, has revised basic target many times. Primarily, the target of the scientists was the functionality of the circuits but after achieving it they turned in performing better area, time, power and other optimizations of the circuit.

In the past meeting area, timing, or power constraints was achievable but now with the technological advancement, competition and the growing complexity of the chips, make the design process a compound, interlaced and time-consuming procedure. In this process, many optimization goals and tight constraints must be addressed.

A key task in chip design is placement, in which the positions of the modules have to be determined in a given chip area. Placement has a direct impact of the total wirelength needed to interconnect the modules, as well as on the performance of the chip for timing and power and on smaller chips.

Evolution of transistors' technology has also grown the difference between static timing analysis on synthesis and RC extraction after physical implementation of a circuit because it cannot compute good estimation of net delays. Transistor technology is now at 28nm while nets cannot reduce their size. Placement has a great impact on wirelength while wirelength is getting more critical for a circuit's performance.

For these reasons placement's requirements have been subjected to many modifications, as placement tools became an essential component in design flow at many stages. Nowadays, powerful, flexible and fast placement algorithms are of particular interest more than ever.

## 2. Preliminaries

In this chapter it is introduced the basic terminology of this thesis. Before the problem's description we will present the basic flow of the chip design.

## 2.1 Definitions

<u>Integrated Circuit (IC)</u>: or monolithic integrated circuit (also referred to as chip, or microchip) is an electronic circuit manufactured by the patterned diffusion of trace elements into the surface of a thin substrate of semiconductor material. [wikipedia]

<u>Very-Large-Scale Integration (VLSI)</u>: is the process of creating integrated circuits by combining thousands of transistors into a single chip. [wikipedia]

<u>Application-Specific Integrated Circuit (ASIC)</u>: is an IC customized for a particular use, rather than intended for general-purpose use. [wikipedia]

<u>Standard-cell library</u>: is a collection of low-level logic functions such as AND, OR, INVERT, flip-flops, latches, and buffers. These cells are realized as fixed-height, variable-width full-custom cells. The cells are fixed-height, variable-width full-custom. The fixed-height enables them to be placed in rows. [wikipedia]

<u>Integrated circuit layout</u>: also known IC layout, IC mask layout, or mask design, is the representation of an integrated circuit in terms of planar geometric shapes which correspond to the patterns of metal, oxide, or semiconductor layers that make up the components of the integrated circuit. [wikipedia]

<u>Core area/Die area</u>: Core area is the area of silicon needed for the cell placement. Die area is the whole silicon area of the chip, as these areas may differ.

<u>Module</u>: is defined as a block of cells, other modules or macros. The most used style is the standard cell layout because of its fixed height of the modules that decrease the time complexity and memory allocated for placement algorithms, which for big circuits of 10000000 gates is critical.

There are five major styles of layout:

- 1. *Gate array:* The gate array design consists of prefabricated silicon with identical modules distributed evenly on the real-estate. The function of a module is determined solely by its connections. Therefore the entire logic is determined by the wires. Space has been reserved for routing

- 2. Sea-of-gates: The sea-of-gates layout is similar to gate array, but no space is reserved for routing. Instead the entire real estate has been filled with

preferable transistors. Some of the transistors become unusable however since space must still be allocated for routing.

- 3. *Standard-cell:* is a collection of low-level logic functions such as AND, OR, INVERT, flip-flops, latches, and buffers. These cells are realized as fixed-height, variable-width full-custom cells. The cells are fixed-height, variable-width full-custom. The fixed-height enables them to be placed in rows. Originally routing was done between rows but multilayer technology now allows for routing anywhere on the real-estate.

- 4. *Mixed-cell:* The mixed-cell model is similar to standard-cell layout, but allows large modules in the layout which may very is height and width

- 5. *General-cell(Macros):*The final layout style which is also the only full-custom is the general-cell layout style. In this case modules are allowed any size and position on the real estate. [3]

<u>Overlap</u>: Two modules overlap with respect to placement if the upper right corner coordinates of the first are smaller than the lower left corner of the second.

Legal placement: A placement is legal when the following constraints are met:

- There is no overlap between modules

- All modules are within the core area

Wirelength: the summation of every net's length in an ASIC.

## 2.2 Computer Aided Design

Computer Aided Design (CAD) is the use of computer systems to design detailed physical objects, through the entire research and development process, thus for the creation, modification, analysis, optimization and final draw of a design. CAD software was created to assist the designer, deal with more complex designs, reduce their faults, and decrease the completion time. Moreover, the designer is allowed to keep documentations and create databases for manufacturing. CAD output is often in the form of electronic files for print or machine operations.

CAD involves all the information needed for the manufacturing process, such as shapes, materials, processes, dimensions and tolerances according to application-specific conventions. Furthermore it may be used to design curves and figures in two-dimensional (2D) or three-dimensional (3D) space.

Picture 1: manufacturing process (Wikipedia)

Nowadays, the number of industries turning to CAD is growing, because of its benefits such as lower cost of product development and a shortened design cycle. CAD software is extensively used in many applications such as automotive, shipbuilding, aerospace and microelectronic industries, industrial and architectural design.

Those are the reasons of why the computer aided design has become an especially important technology within the scope of computer-aided technologies. It is one of many tools used by engineers and designers and is used in many ways depending on the profession of the user and the type of software in question.

## 2.3 Electronic Design Automation

Electronic Design Automation (EDA or ECAD) is a category of CAD tools for designing electronic systems such as printed circuit boards and integrated circuits.

Before EDA, integrated circuits were designed by hand and manually laid out. The earliest EDA tools were produced academically. By the mid-70's the first EDA tools for placement and routing were developed. One of the most famous was the "*Berkeley VLSI Tools Tarball*", a set of UNIX utilities used to design early VLSI systems. The beginning of industrial EDA was at 1981, as the larger electronic companies pursued EDA manually until then. Now EDA tools work together in a design flow that designers use to design and analyze entire semiconductor chips.

EDA led to the development, massive production and cost reduction of high-tech conveniences such as cell phones, navigation systems, media players etc. Nowadays EDA has an extraordinary effect on human life, as almost everything and every daily task have been influenced by this. The progression of microprocessor technology in terms of performance and features made the computer an essential tool and part of everyday life.

EDA has increased importance in the latest years, with the continuous scaling in semiconductor technology, because with the DSM era there are a lot of problems to be faced. Some of them are Design for Testability (DFT) and Automatic Test Pattern Generation (ATPG), lithography etc. Moreover, the evolution of the tools is necessary in order to overcome the difficulties of this era.

## 2.4 Design Flow

Design flows are the explicit combination of EDA tools to accomplish the design of an integrated circuit. Moore's Law has driven the entire IC implementation RTL to GDSII design flows from one which uses primarily standalone synthesis, placement, and routing algorithms to an integrated construction and analysis flows for design closure. [wikipedia]

Due to the progress being made by the semiconductor industries, e.g. the transistors' scaling, reducing the interconnection delay has become the great challenge. This fact led to a new way of thinking about integrating design closure tools and new scaling challenges for the current state of the art tools uprised, such as leakage power, variability, and reliability. There are two discrete flows for ASIC and FPGA designs. This thesis is based on the ASIC flow.

As mentioned above all EDA tools work together in a design flow that chip designers use to design and analyze entire semiconductor chips. In this section is described a typical design flow, as there are some variations, e.g. for low-power design. The figure below, illustrates the ASIC flow.

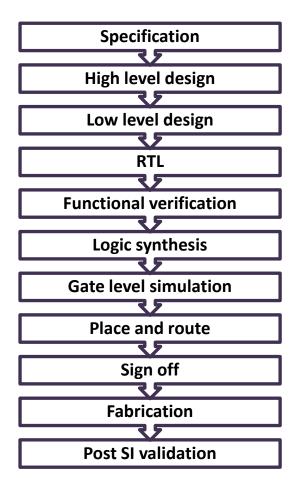

Picture 2: front end and back end design flow. Every step follows the others, top-down. If there is a problem in any step, designers must go back to previews steps. E.g. if the gate level simulation fails, the rtl code must be designed from the start.

The whole process it can be separated in 2 domains:

- Front-end flow

- Back-end flow

#### 2.4.1 Front-end flow

The Front-end flow is the process that guides from the concept to the netlist of logicgates of a circuit. It includes steps, such as architectural design, simulation and synthesis. The front-end flow finishes at the Logic Synthesis step as depicted in the picture.

- <u>Specification</u>: The step at which are described important parameters of the design, e.g. what the design should do.

- <u>High-level design</u>: Various blocks are defined and description of the communication between them. Description is given in high-level languages (SystemC, C, C++).

- <u>Low-level design</u>: It is described how each block is implemented. It contains details about FSMs, counters, registers etc.

- <u>RTL</u>: The step at which Low-Level design is converted into Verilog / VHDL code, using synthesizable constructs of the language.

- <u>Functional Verification</u>: It is verified that the design does its expected function. Testbenches are created to apply all possible stimuli at the input and check the output.

- <u>Logic Synthesis</u>: Is the process in which synthesis tools take RTL code, target technology and constraints as inputs and maps the RTL to target technology primitives. After the gate-level netlist is created, timing analysis is done to check that the mapped design is meeting timing requirements.

- <u>Gate-level Simulation</u>: Check if the Design Under Test (DUT) is functionally correct.

Before passing the netlist to the back-end flow, usually it is done Formal verification and insertion of scan-chains.

- <u>Formal verification</u>: Check if the RTL to gate mapping is correct

- <u>Scan-chain insertion</u>: Insert scan-chain in case of ASIC for design-fortestability(DFT) [asic-world.com]

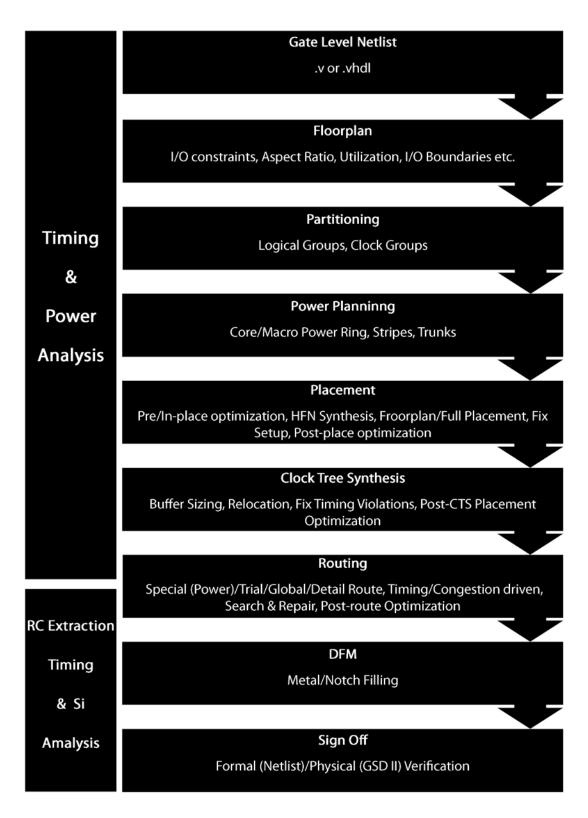

## 2.4.2 Back-end flow

Back-end flow or physical implementation is the step in the standard design cycle which follows after the Front-end. At this step, circuit representations of the components (devices and interconnects) of the design are arranged on a piece of semiconductor material. More specifically they are converted into geometric representations of shapes which, when manufactured in the corresponding layers of materials, will ensure the required functionality of the design. The next step after Physical Design is the Manufacturing process or Fabrication Process that is done in the Wafer Fabrication Houses.

The main steps of the back-end are described in the figure below.

<u>Gate-level netlist</u>: Is the circuit's synthesized netlist, produced after the completion of the front-end flow. It includes only standard-cells and their interconnections, as well and primary inputs and outputs of the circuit.

<u>Floorplanning</u>: Is the process in which the area of the design, the IO structure and the aspect ratio are decided. The usual process is to find structures that should be placed close together, and allocates space for in order to meet the, sometimes, conflicting goals of available space (cost of the chip) and the required performance. During this process some components such as the macro's used in the design, memory, other IP cores and their placement needs, the routing possibilities and also the area of the entire design (core area/die area), are taken into account in order to find the most suitable place for them, as these components can have a dramatic effect on the performance of the chip.

<u>Partitioning</u>: Is a process of dividing the chip into small blocks. This is done mainly to separate different functional blocks and also to make placement and routing easier. Partitioning can be done in the RTL design phase when the design engineer partitions the entire design into sub-blocks and then proceeds to design each module. These modules are linked together in the main module called the TOP LEVEL module.[wiki]

<u>Placement</u>: Is the process of placing the modules of the design, described in the gatelevel netlist, in the core area decided in the floorplan step.

<u>Clock-Tree Synthesis (CTS)</u>: Before CTS, clock is not propagated and considered ideal. Clock tree begins at source clock and ends at pins of a flop.

<u>Routing</u>: There are two types of routing in the physical design process, global routing and detailed routing. Global routing allocates routing resources that are used for connections. Detailed routing assigns routes to specific metal layers and routing tracks within the global routing resources.[wiki]

<u>Signoff</u>: Checks the correctness of the layout design, before it can be taped-out. There are several categories of signoff checks:

- *DRC* Also known as geometric verification, this involves verifying if the design can be reliably manufactured given current photolithography limitations. In advanced process nodes, Design-for-Manufacture (DFM) rules are upgraded from optional (for better yield) to required.

- *LVS* Also known as schematic verification, this is used to verify that the placement and routing of the standard-cells in the design has not altered the functionality of the constructed circuit.

- *Formal Verification* The logical functionality of the post-layout netlist is verified against the pre-layout, post-synthesis netlist.

- *Voltage-drop analysis* Also known as IR-drop analysis, verifies if the powergrid is strong enough to ensure that the voltage representing the binary high value never dips lower than a set margin.

- *Signal-integrity analysis* Noise due to crosstalk and other issues is analyzed, and its effect on circuit functionality is checked.

- *Static-timing analysis (STA)* Is used to verify if all the logic data paths in the design can work at the intended clock-frequency.

- *Electromigration lifetime checks* To ensure a minimum lifetime of operation at the intended clock frequency without the circuit succumbing to electromigration.

- Once the design has been physically verified, optical-lithography masks are generated for manufacturing. The layout is represented in the GDSII stream format that is sent to a semiconductor fabrication plant (fab).

## 3. Placement

In order to produce an ASIC, a robust architecture of sub-circuits that meets the specifications must be designed and standard techniques for transporting an architectural design to a physical design with timing, area and power limitations. The development of digital circuits must depend on a detailed design due to their incremental complexity and large cost of their creation of a lithographic photo-mask.

Physical implementation starts given the physical design's behavioral description language. Then the structure of a circuit must be specified in a structural **R**egister **T**ransfer Level (RTL) language, a high-level hardware description language (HDL) for defining digital circuits. RTL specifications are turned into gate-level netlists, and the circuits are described as a collection of registers, Boolean equations, control logic such as "if-then-else" statements as well as complex event sequences The most popular RTL languages are VHDL and Verilog.

The circuit description does not contain the exact coordinates of every gate in the specified circuit area and does not contain the exact style of interconnections neither, so the next step is to determinate the placement decision of where to place all electronic components, circuitry, and logic elements in a generally limited amount of space and routing of the circuit, which decides the exact design of all the wires needed to connect the placed components. These two operations belong to the same step because the routing follows the placement description and builds up to it, in the way that a good placement can lead to an easier routing decision. Both of these operations are NP-hard problems, so there is a try to find approximate algorithms based on heuristics or branch and bound strategies.

With the placement and routing step, the circuit is fully described. Therefore the characteristics of the design can be computed. The final step is to perform signoff, in order to test all the signoff constraints described in chapter 2.

## **3.1** The Placement problem formulation

The general purpose of solving the VLSI placement problem is to find the best position of each module of a circuit on a specific area with the respect to a cost function that must be minimized.

More specifically, given:

- A netlist of cells from a pre-defined semiconductor library

- A mathematical expression of that netlist as a vertex, edge-weighted graph

- Constraints on pin-locations expressed as constraints on vertex locations / aspect ratio that the placement needs to fit into

• One or more of the following: chip-level timing constraints, a list of critical nets, chip-level power constraints

Placement process returns:

- Cell/vertex locations to minimize placement objective subject to constraints

- No two cells/vertexes overlap

- Placement is routable

An important part of the placement problem is to understand the critical cost functions that must be minimized. Some of these functions might be:

- Minimization of the expected length of longest wire, or the sum of the length of all the wires in the design, which is the primary objective of most existing placers. This not only helps minimize chip size, and hence cost, but also minimizes power and delay, which are proportional to the wirelength.

- Minimization of wire routing congestion. While it is necessary to minimize the total wirelength to meet the total routing resources, it is also necessary to meet the routing resources within various local regions of the chip's core area. A congested region might lead to excessive routing detours, or make it impossible to complete all routes.

- Minimization of timing delay. The clock cycle of a chip is determined by the delay of its longest path, usually referred to as the critical path. Given a performance specification, a placer must ensure that no path exists with delay exceeding the maximum specified delay.

- Minimization of power. Power minimization typically involves distributing the locations of cell components so as to reduce the overall power consumption, alleviate hot spots, and smooth temperature gradients.

- The minimization of the core area, die area, and other area constraints of the design, which come up for different reasons (remote devices, economical reasons etc.).

- The minimization of the distance of modules that use the same clock.

- A secondary objective is placement runtime minimization.

The optimal is to minimize every function but this is impossible because some functions have conflicts thus when one minimizes a variable the other may maximizes its own variable, for example when timing delay is minimized the power is grown. A good placement analysis must respect the cost functions that must be optimized and find a close to the golden mean that keep the balance between the critical variables. Another issue with the cost functions is that the evolution of technology changes their importance in the export of results. For instance, before the 90 nm-node transistors the basic timing delay was existed by a bad minimization of a specific area, but now it is proved that total delay is determined in a very grate percentage by routing, and the cost function that matters more is the total wire-length minimization.

Placement problem is a NP-hard problem, which means that it cannot have a solution in polynomial upper time limit. If can be proved that the decision of a placement is a NP-complete problem then can be proved that the placement problem is an NP-hard problem. Below there is an explanation, but not the entire mathematical proof, as it is out of scope of this thesis:

The placement decision problem can be defined as the algorithm that decides given some modules, pins, nets, a specified area, if all modules can be positioned correctly and legally in the placement area. Of course it cannot be decided in polynomial but in exponential time because every combination of two cells must be checked and that leads to a quadratic problem. Officially the placement decision problem can be retreaded to the subset sum problem, which decides given a set of integers, if there is a non-empty subset whose sum is exactly zero, and is a NP-complete problem. Therefore the decision of a placement is a NP-complete problem.

Also it is proved that if an optimization problem H has an NP-complete decision version L, then H is NP-hard, thus the placement problem is NP-hard because it optimizes a cost function.

## **3.2** Classification of placement algorithms

The placement problem can be divided in two steps:

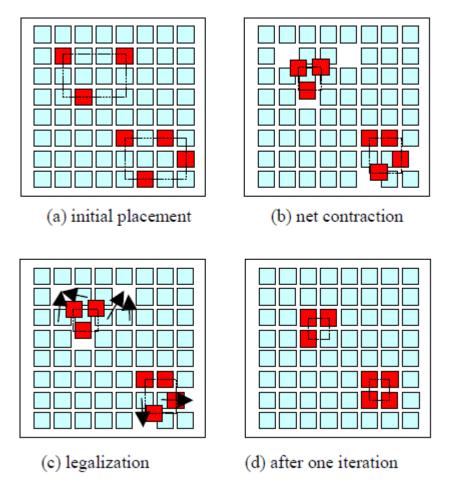

<u>Global placement</u>: It has also mentioned as relative placement, because it uses constructive or iterative algorithms in order to find a near-optimal placement, as a fist attempt of placing the cells into the placement area, usually by dividing it into core bins. This placement has overlaps between cells.

<u>Final placement</u>: It has also mentioned as detailed placement. Using the global placement as an input and a local final placement algorithm, it cuts the core area into core bins and finds a near-optimal placement solution for every core bin. Usually the output is a legal placement proposition, but the inner-solutions are not necessarily legal. If the output has overlaps then a legalization step is necessary to export a result that can be constructed in the psychical design. Additionally, in many final placement optimization. Wire or cell positions can be improved in this step, depend on the cost function, usually by swapping cells or wires movement. A global post placement optimization is usually done as a separate design flow step, after placement completion, which can add buffers in the design or use biggest/shorter standard cells to improve placement's objective subjects. No further discussion will be done for this last step because it is out of this thesis scope.

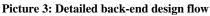

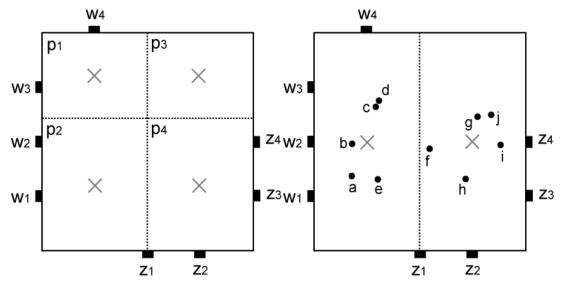

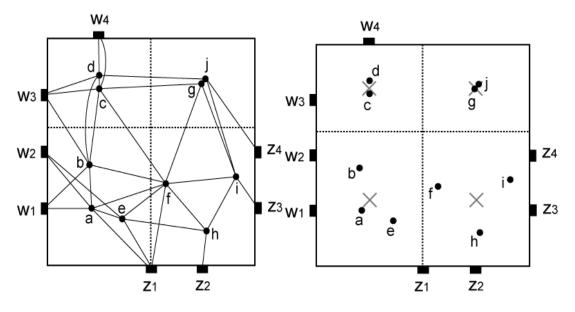

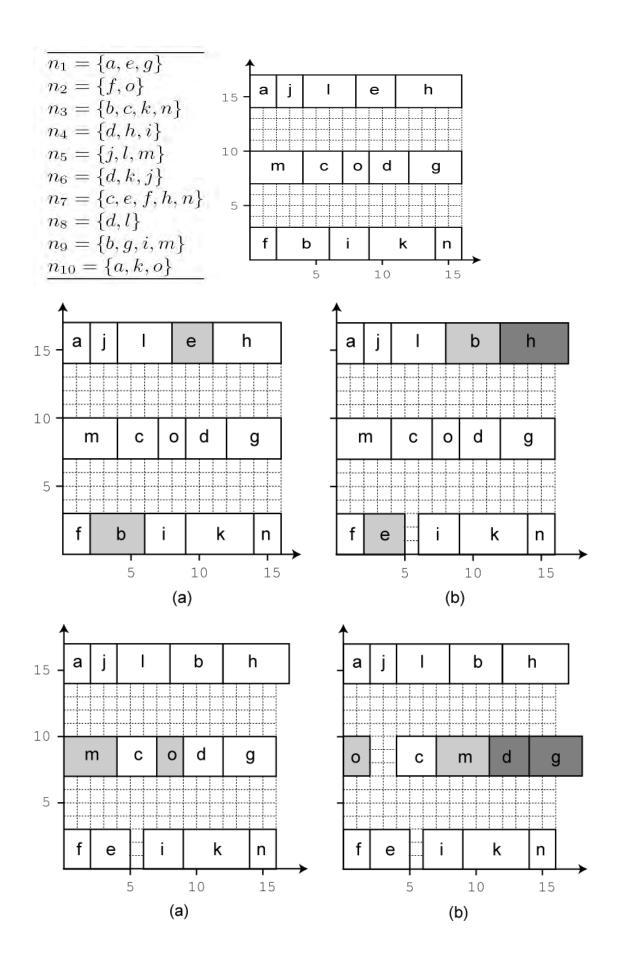

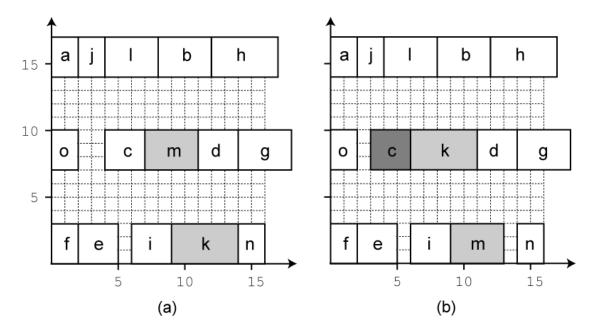

Picture 4: The first picture displays a Global placement, and the second displays a detailed placement with legalization, for the same part of a circuit.

Placement algorithms can also be split into constructive and iterative.

<u>Constructive</u> placement improvement algorithms deal with every cell once, but iterative algorithms have many reiterations of a curtain procedure and deal with every cell iteratively. Constructive algorithms are usually very fast and produce good results because of their global view of the problem. However, they are generally restricted in the choice of objectives and often do not yield the global optimum of the placement problem because of sacking in local minimums.

<u>Iterative</u> placement improvement algorithms aim at improving existing solutions, especially initial placements usually obtained with constructive algorithms. Typically, in one iterative step they select a small and local sub-problem to be solved by exact or heuristic methods. These algorithms also divide into two classes depending upon whether they apply random or deterministic techniques. Iterative improvement methods based on randomized algorithms never reject better solutions, but they also accept intermediate placements of inferior quality with low probabilities. Thus, they have the ability to escape local optima and to approach the global optimum arbitrarily close if sufficient computation time is provided. Since this is not always practicable, particularly for large circuits, layout quality is compromised.

The philosophy of output produced by an algorithm is another way of classifying the placement algorithms. Some algorithms generate the same solution when presented with the same problem, i.e., the solution produced is repeatable. These algorithms are called deterministic placement algorithms. Fixed connectivity rules, cause and effect algorithms, or simultaneous equations solution are deterministic and always produce the same result for a particular placement problem and nothing else could be produced. Some algorithms, on the other hand, work by randomly examining configurations and may produce a different result each time they are presented with the same problem. Such algorithms are called as probabilistic placement algorithms.

Placement algorithms can also be classified from their solution approach of wirelength minimisation, to linear, quadratic or neither of the two. But to understand the difference first there must be defined some wirelength metrics that the algorithms deal with, in the next paragraph.

## 3.3 Net metrics

After implementing placement process in a design, cells obviously have standard coordinates inside the core area. This means that a close to absolute total wire length can be calculated, summarizing every net. Because of not having the exact net distance of nets before routing stage, there is a need to define some netlength metrics with which the wirelength can be calculated and then optimized. Before proceeding, consider that in all distance metrics, cells are defined as points, with coordinates their lower left point or their center.

#### **3.3.1** Lk-norm induced distance metric

$$dk(p,q) = \sqrt[k]{|p_x - q_x|^k + |p_y - q_y|^k}, \quad p,q \in \mathbb{R}^2, \ k \in \aleph$$

Let p and q be two modules, and px py, qx qy their coordinates in x and y axis. L1 is the Manhattan distance and L2 is the Euclidean distance which is mostly using as a netlength distance metric. Also, when  $k \rightarrow \infty$  it gives:

$$d_q(p,q) = \lim_{k \to \infty} d_k(p,q) = \max(|p_x - q_x|, |p_y - q_y|)$$

#### **3.3.2** Rectilinear Steiner Tree and Minimum Spanning Tree

Given n points in the plane, it is required to interconnect them all by a shortest network which consists only of vertical and horizontal line segments. It can be shown that such a network is a tree whose vertices are the input points plus some extra points (Steiner points). [wikipedia]

Assuming that until nowadays only horizontal and vertical wires are used, the total minimal netlength is achieved by connecting pins in each net with a Steiner tree such that there is no intersect between trees. Although the routing of a whole net with multiple nodes is better represented by the rectilinear Steiner tree and it can be considered as the smallest wirelength measure, the rectilinear minimum spanning tree (RMST) provides a reasonable approximation and wire length estimate. Rectilinear minimum spanning tree can be considered as a RSTM without extra (Steiner) points, so every node is interconnected in the shortest network which consists only of vertical and horizontal line segments. For the same number of nodes with specific coordinates, Hwang proved that:

$$RMST length \leq \frac{3}{2} RSMT length$$

The RSMT is an NP-hard problem but proof is out of the scope of this thesis.

#### **3.3.3** Clique

The clique model is very popular in many VLSI problems. This model is based on proper conversion of nets into clique subgarphs. The given weight for every edge that builds the clique is computed by the following type:

$$w(i,j) = \frac{2}{n}$$

Where i, j the nodes connected by an edge and k the total number of the cliques' nodes. This type ensures that the effect of the total weight of big cliques is relatively decreased against small cliques that are usually the majority in physical designs. On the other hand this type ensures that the total weight effect is balanced to the size of every clique.

Then, the length of a net  $n \in N$  is the total distance of pairs of pins in the net:

$$CL_k(n) = \frac{1}{(|n|-1)} \sum_{p \in n} \sum_{q \in n} d_k (A(p), A(q))^k$$

The clique netlength may be evaluated in time  $O(|n|^2)$ . For an improved approximation of the linear net model by the quadratic one, Gordian-L(Sigl, Doll and Johannes [1991]) use the following iterative net model: in iteration k = 2... one optimizes essentially:

$$GordianL_{x}^{(k)}(n) = \frac{1}{|n| - 1} \sum_{p,q \in n} \frac{(x_{k}(p) - x_{k}(q))^{2}}{|x_{k-1}(p) - x_{k-1}(q)|}$$

and  $L^{(k)}(n) = GordianL_x^{(k)}(n) + GordianL_y^{(k)}(n)$ .

Recall that linear clique was the model of choice for a-priori topologies, so in the limit one can obtain the best achievable result. But after all, one cannot expect more than linear convergence of this method, so in general this approximation method will be too slow.

#### 3.3.4 Star

This model is similar to clique model, where the hyperedges of the graph are converted to star subgraphs.

#### **3.3.5** Bounding Box

The bounding box is by far the simplest net metric, as it defines that total netlength of a circuit is the summary of the half perimeter of the bounding box surrounding every net.

$$BB(n) = \max_{p \in n} (A_x(p)) - \min_{p \in n} (A_x(p)) + \max_{p \in n} (A_y(p)) - \min_{p \in n} (A_{xy}(p))$$

Complexity of calculating the total netlength using the bounding box metric is O(n).

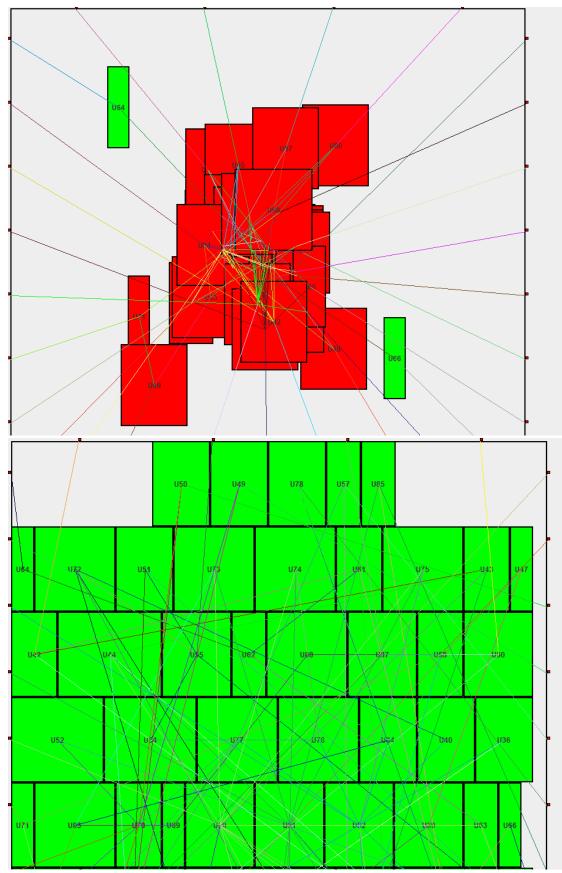

Now considering and comparing the complexity of bounding box metric and the clique metric, it is obvious that algorithms that use bounding box metric called linear minimization algorithms, and algorithms that use the clique metric called quadratic minimization algorithms. The figures below can show the graph style of every metric and the graph style of the difference between linear and quadratic calculation.

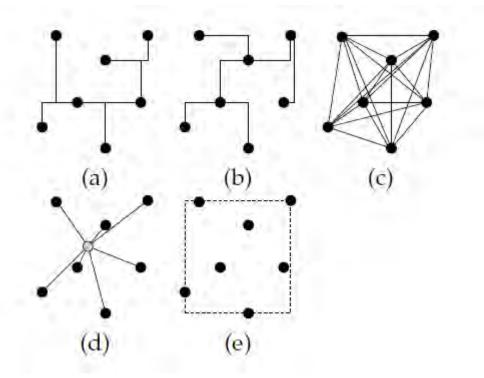

Picture 5: Rectilinear Steiner Tree and Minimum Spanning Tree (a,b), clique(c), star(d), bounding box(e). [3]

## 3.4 Minimizing Quadratic Netlengths

Both quadratic clique and star netlengths can be expressed by matrix notation. If the corresponding problem is relaxed by removing the no-overlap constraints the quadratic netlength we can be minimized many methods, with the most popular to be the Conjugate Gradient Method.

The Conjugate Gradient Method works on parabolic functions by taking steps towards the global minimum. The method requires that the quadratic matrix is symmetric and positive. In each step of this iterative procedure the current solution is moved in the direction of the eigenvalues of the matrix. When the solution is deemed close to minimum the procedure ends. The complexity of this method depends on the spectral condition number k of the matrix and it is  $O(\sqrt{km})$  when m is the number of non-zero elements of the matrix and sparse matrix data structures are used.

The matrix is in general sparse. Each row corresponds to a module. For the star model the number of non-zero elements in a row is roughly equal to the number of nets the module of that row is connected to. For the clique model this number is equal to the number of modules the module is connected to. It is generally assumed that the average number of nets each module is connected to is usually less than 5.

## 3.4.1 Preconditioning

As mentioned above the Conjugate Gradient Method depends on the spectral condition number k. This can be improved by using a preconditioner. The essence of the preconditioning method is that instead of solving a system of the form Ax = b one can solve an auxiliary system  $M^{-1}Ax = M^{-1}b$ . If  $M^{-1}A$  is better conditioned than A we may get faster convergence. The matrix M is called a preconditioner and the problem is of course determining M such that we can easily find  $M^{-1}$ . Ideally one would pick A but since there is no information about  $A^{-1}$ , an alternative choise has to be taken. The simplest preconditioner is the diagonal of A and the most popular is an incomplete cholesky factorization of A. We will not discuss preconditioning further here but even diagonal preconditioning can improve the order of convergence significantly.

## 3.5 Minimizing Linear Netlength

The unconstrained linear bounding-box formulation can also be solved in efficient time. Here the objective function is the dual of a minimum-cost-flow problem. The dual problem can be solved and by using LP-duality a solution to the primal problem can be determined, as it proposed by Weis and Mlynski. Nevertheless even the fastest

algorithms of this kind have quadratic running time,  $O\left(mnlog\left(\frac{n^2}{m}\right)\right)$ .

Linear net models, approach better the actual post-route wirelength, but lead to various drawbacks during placement. The first reason is the optimization issue as linear functions are not differentiable. Despite the fact that placement minimizing linear bounding-box netlength can be considered as the dual of a Minimum Cost Flow problem and computed exactly, linear solutions stuck in local minima and it is difficult to compute global optima in acceptable time if the number of variables is in the millions. The second reason is that placements optimizing linear netlength are not unique in general. Those computed by such a Minimum Cost Flow approach tend to implode cells in some particular corner of the core area and do show significant overlaps, which are solved with many arbitraries and cause worst wirelength solutions as a result. Such an effect does not show up for strictly convex net models. Nevertheless, many non-linear methods exist to approximate the linear netlength model, also called analytic. These approaches are introduced in next paragraphs.

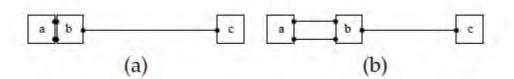

Picture 6: Linear (a), quadratic (b) solution for wirelength minimization [3].

## 4. Placement methods and Algorithms

As mentioned in the previous chapter, traditionally, placement is separated in two stages, global placement and final placement. In this chapter are presented, analytically, the methods of these two stages and the most known algorithms.

## 4.1 Global placement Methods

The main purpose of global placement is to distribute the cells evenly over the placement region and optimize certain objectives e.g. wirelength, timing, power etc. It pays attention to the relative positions of the cells globally.

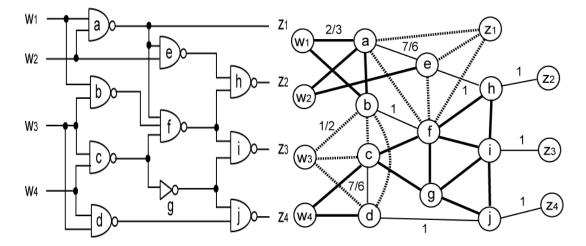

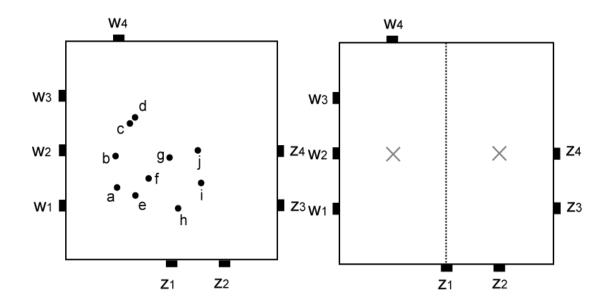

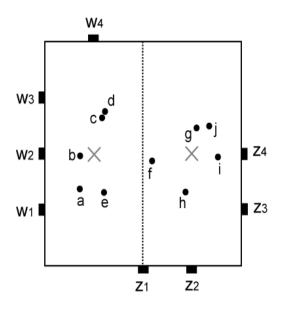

## 4.1.1 Graph partitioning

The most used technique for global placement is based on graph partitioning. Given a gate-level circuit, the goal of circuit partitioning problem is to divide the circuit into K roughly equal-sized partitions. The main goal of this method is to minimize the number of hyper-edges that connect nodes from one partition to another, which is typically called the "cut-size" in the literature. Other objectives include critical path delay, total power consumption, etc. Due to these objectives, partitioning algorithms can be divided into linear and analytic, that use linear solutions for the "cut-size" and quadratic approaches to compute other objectives. These two categories are analyzed further below.

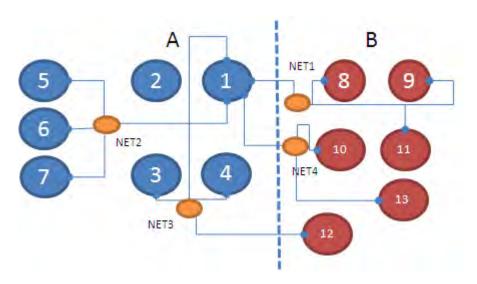

Picture 7: cut-size example, institute of Microelectronics Systems (MES)

#### 4.1.1.1 Linear based partitioning heuristics

Every module that has to be placed is defined as a node of a graph with specific weight. Weight of nodes is computed usually by the cell's fanout and its area or other critical objectives. In this iterative method each bisection has to be chosen such that the weight of nodes on either side is close to equal while at the same time the number of edges cut by the bisection is kept at a minimum. After the components are preplaced with an initial placement algorithm, partitioning starts with the entire graph as the first partition. In every step a partition with total weight W is cut in two other with weight W/2 and this is done recursively for every new partition until the number of

edges cut by the bisection is the minimum. With this technique it is succeeds to keep close to each other all the highly connected components.

Linear graph partitioning approaches do not accomplish wirelength minimization directly but in every, which can achieve placements inside a partition that is faster and dealing with a smaller number of components that are highly connected. If the Simulated Annealing approach will be combined with the graph partitioning technique, it will accept any kind of objective, in particular wirelength, but it can be applied only for tiny instances due to its huge complexity, so for large scale circuits another technique has to be used. Analytic approaches can cover this drawback, especially in global placement, as in detailed placement the core area can be partitioned and can be handled separately. Nevertheless this global placement problem is NP-hard (reduce from 2-partition) because of the balance requirement.

Two famous linear graph-partitioning algorithms are of Kernighan-Lin in 1979 and Fiduccia-Mattheyses in 1982.

Kernighan-Lin: Given a netlist, the first step is to create an edge-weighted undirected graph *G* that represents the circuit. We typically use so called the *k*-clique model, where a net that contains *k* gates forms a *k*-clique in *G*, and each edge in the clique gets a weight of 1/(k - 1). In case an edge (x, y) already exists from a prior net conversion, it weight has to be updated properly. The KL algorithm is applied on this graph, so the cut-size and gain are computed based on it, instead of the original circuit. Next, an initial balanced bipartitioning solution (*P*1, *P*2) of G is acquired, usually randomly. For a cell  $x \in P1$ , the external cost of x is defined as follows:

$$E_x = \sum_{i \in P_2} c(x, i)$$

where c(x, i) is the weight of the edge e(x, i). This *Ex* is the expression for the sum of the weight of edges which connect *x* with nodes that are in other partition, where the neighbors of *x* are defined to be the nodes that are connected with *x* via an edge. Sequentially the internal cost of x is defined as follows:

$$I_x = \sum_{i \in P_1} c(x, i)$$

This Ix is the expression of the sum of the weight of edges that connect x and its neighbors in the same partition. Finally, the gain of swapping x and y is defined as follows:

gain(x, y) = (Ex - Ix) + (Ey - Iy) - 2c(x, y)

Before the first pass starts all cells are considered as locked. Once the pass begins, the following procedure is repeated at every swap until all cells are locked. Firstly, the gain of all unlocked pairs is computed and then the pair with the maximum gain is swapped and the cells in the pair are getting locked. In the third step, the gain and the current cut-size are recorded. When the pass is finished, the first K swaps with the biggest gain are accepted, leading to the minimum cut-size discovered during the entire pass. If the initial cut-size has reduced during the current pass, it means that a better solution has been discovered, and another pass is tried on using as initial

solution the best solution discovered from the current pass; otherwise the algorithm is terminated considering that it cannot find a better solution. Since the cells' swapping, the area is always balanced between the two partitions. Note also that the entire Kernighan and Lin algorithm can be repeated with another random initial solution.

```

Kernighan_Lin (A, B)

compute D values

for i from 1 to n

Locked[ i ]:= false

BestCost := Cost[ 0 ] := cutsize(A, B)

BestChange := 0

for s from 1 to n/2 do

Cost[s]=...

for i, j from 1 to n such that v_i \in A and Locked[1] = false and v_i \in B and Locked[1] = false do

if 2 ω[i, j] - D[i] - D[j] < Cost[s] then

Pair[s] := (i, j)

Costs[s]:=2w[i,j]-D[i]-D[j]

(imin, jmim) := Pair[ s ]

Locked[ imin ] = Locked[ jmin ] = true

for i from 1 to n such that Locked[i] = false do

if v∈ A then

D[i] = D[i] - 2\omega[i, jmin] + 2\omega[i, imin]

else

D[i] = D[i] - 2\omega[i, imin] + 2\omega[i, jmin]

Cost[s]:=Cost[s-1]+Cost[s]

if Cost[s] < BestCost then

BestChange := s

BestCost := Cost s ]

for s from 1 to BestChange do

exchangePair[s]

```

Picture 8: Kernigham - Lin algorithm, institute of Microelectronics Systems (MES).

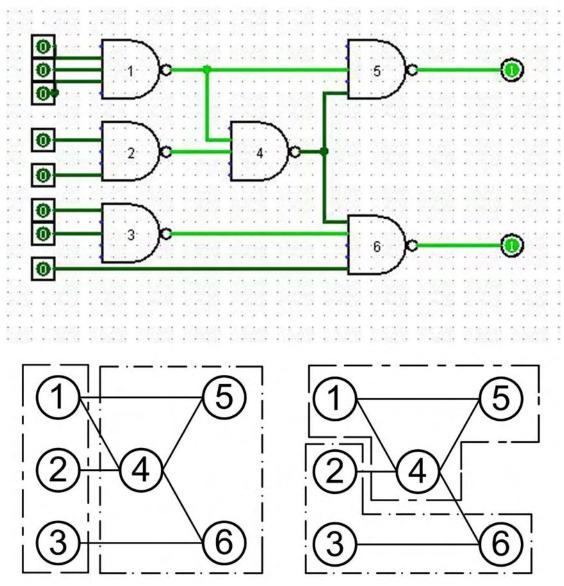

Fiduccia-Mattheyses: The algorithm starts with an initial balanced bipartitioning solution (P1, P2) of the given hypergraph, which is usually obtained randomly.

For a cell  $x \in P1$ , FS(x) is defined as the number of nets that have x as the only cell in P1.

TE(x) is defined as the number of nets that contain x and are entirely located in P1, i.e., all cells in the net are partitioned in P1. Finally, the gain of moving x from P1 to P2 is simply:

gain(x) = FS(x) - TE(x)

Before the first pass starts all cells are considered as locked as in Kernighan and Lin algorithm, and the gain of all cells is computed based on the initial partitioning. Also the cells have to be added to the bucket structure. Once the pass begins four steps have to be repeated at every move until all cells are locked. Firstly, the cell with the maximum gain is considered as legal. A cell move is legal when while moving it to the other partition it does not violate the core area constraint. Secondly, the chosen

cell is moved and locked it in the targeted partition. After these steps, the gain values of the moved cell's neighbors their positions in the bucket are updated, and finally the gain and the current cut-size is recorded. At the end of the pass, the first K moves are identified, accepted and lead to the minimum cut-size during the entire pass. If the initial cut-size has reduced during the current pass, we attempt another pass using the best solution discovered from the current pass as the initial solution; otherwise the algorithm is terminated. Note that the entire FM algorithm can be repeated with another random initial solution.

```

Step 0: Compute the balance criterion

Step 1: Compute the cell gain \Delta g_1 of each cell

Step 2: i = 1

- Choose base cell c_1 that has maximal gain \Delta g_1, move this cell

Step 3:

- Fix the base cell c_i

- Update all cells' gains that are connected to critical nets via the base cell c_i

Step 4:

- If all cells are fixed, go to Step 5. If not:

- Choose next base cell c_i with maximal gain \Delta g_i and move this cell

- i = i + 1, go to Step 3

Step 5:

- Determine the best move sequence c_1, c_2, ..., c_m (1 \le m \le i), so that G_m = \sum_{i=1}^m \Delta g_i is maximized

- If G_m > 0, go to Step 6. Otherwise, END

Step 6:

```

Picture 10: : Fiduccia-Mattheyses example, Wikipedia.

#### 4.1.1.2 Analytic based graph partitioning heuristics

The analytic partitioning heuristics are closely related to the graph-partitioning heuristics. But instead of minimizing cuts they use the analytic placement to guide the position of the cut-lines. The oldest analytic method found in the literature is from 1970 and by Hall, and the most popular algorithms are of Hagen and Kang (EIG), and of Yang and Wong (FBB).

EIG: this algorithm utilizes the second smallest eigenvalue and its eigenvector of a netlist matrix to optimize so called the "ratio cut" metric. This ratio cut metric, defined as c(X, Y)/|X|/|Y|, where c(X, Y) denotes the cutsize between the two partitions X and Y, managing to minimize the cutsize and balancing the area of the existing partitions. Given an undirected graph that represents the connectivity among the nodes, and its Laplacian matrix, the eigenvector of the second smallest eigenvalue of the matrix defines a one-dimensional placement of the graph's nodes [Hall 1970]. In this placement solution, the quadratic length of every edge in the graph is minimized under the constraint  $\sum_i x_i = 1$ , where xi is the x coordinate of node i. It is also shown that the second smallest eigenvalue of the matrix is the lowest bound of the ratio-cut metric. According this, their analytic partitioning algorithm computes bipartitioning solutions with minimum ratio-cut metric, using the one-dimensional placement. So, given a gate-level circuit, first its undirected graph representation must be derived, based on the standard k-clique model. In this model, a net with k gates forms a k-clique, and each edge in the clique gets a weight of 1/(k - 1). The remaining part of the algorithm proceeds as follows:

1. Building of the  $n \times n$  Laplacian matrix Q = D - A, where n is the number of nodes in graph G. A is the adjacency matrix, where each entry a(i,j) denotes the weight of edge e(i,j) in G. D is the degree matrix, where each entry d(i,i) is the sum of the weights of all edges incident to node i in G.

2. Computation of the second smallest eigenvalue and its eigenvector of Q using Lanczos method.

3. Sort of the nodes in G based on their values in the eigenvector and obtain the node ordering  $Z = \{v1, v2, \dots, vn\}$ .

4. Usage of Z to derive and evaluate n - 1 partitioning solutions. More specifically, we first obtain a bipartitioning solution ({v1}, {v2, ..., vn}) and compute its ratio cut metric.4 Next, we evaluate the ratio cut metric of ({v1, v2}, {v3..., vn}) from H, etc. Lastly, we choose the partitioning solution with the minimum ratio cut metric.

FBB: FBB performs flow-based bipartitioning. Given a flow graph G and a pair of source and sink nodes (s, t), the Maximum Flow Minimum Cut Theorem [Ford and Fulkerson, 1962] states that the maximum flow from s to t defines a bipartitioning of G, and the weight of the cut is minimized among all cuts separating s and t. Yang and Wong proposed an iterative method to repeat max-flow computations to find balanced solutions for the partition cuts from s to t, with complexity that approach

asymptotically the same as a single max-flow computation, recycling the growing paths from the previous iterations. When a circuit has multi-terminal nets, they proposed a way to transform them into a flow network G so that any cut in G preserves the correct cut-size information in the circuit. Lastly, they proposed an effective way to achieve the next cut if the current cut is not balanced, which is based on making a minor perturbation to the current flow network.

More specifically, given a circuit *H*, the flow network G must be built, where each net  $n = \{v1, v2, ..., vk\} \in H$  is transformed as follows:

Nodes v1, v2, ..., vk were added into G if not added yet. Two auxiliary nodes n1 and n2 were added into G and are connected with bridging edge e(n1, n2) with its capacity value set to 1. Node n1 is connected with v1, v2, ..., vk with edges of  $\infty$  capacity. Node n2 is connected to v1, v2, ..., vk with edges of  $\infty$ capacity. Next, a pair of source and sink (s, t) has to be chosen randomly. After these, the flowing must be repeated until a balanced bipartitioning solution is found:

The maximum flow from *s* to *t* using the growing path method must be found.

Then we construct the partitioning solutions based on the max-flow computation, which is done by cutting some subset of the saturated nets. Simultaneously, the best solution for the area balancing C(X,X') must be found. Note that all of these solutions have the same cut-size, which is equal to the max-flow value. If a solution that satisfies the area constraint is found, the algorithm is terminated.

Nevertheless, the solution is not necessarily area-balanced. In this case must be examined if the area of X is smaller than the area lowest bound when a node  $v \in Y$  that is contained in a cut net is chosen. Lastly, all nodes in X and v are merged into a single node, which becomes a new source s, and the algorithm starts again from the first step. Otherwise, if the area of X is bigger than the area upper bound, a node  $v \in X$  that is contained in a cut net must be found, all nodes in X' and v are merged into a single node, which becomes a new sink t and the algorithm starts again from the first step.

When the algorithm is in step 1 of some iteration, some of the growing paths are already found in previous iterations. This slows down the process' complexity by finding only the new additional growing paths, in order to obtain a new max-flow. Also, we choose v among the nodes in the cut net randomly, while we are finding a node v to merge with X or with X'. Thus, as the algorithm approaches closer to a balanced solution, we choose the best v among all the nodes in the cut nets.

## 4.1.2 Analytic and Relaxation Based Placement

The quadratic wirelength formulations can be solved fast using numerical linear equations solvers, with the most popular the Conjugate Gradient Method, while the bounding-box formulation requires quadratic running time network-flow methods.

#### 4.1.3 Force-Based Methods

The force-based methods can be defined as methods that handle modules as objects and nets as springs connecting the objects, and try to minimize the interconnection netlength by putting the "spring-system" into equilibrium, in respect to the Hooke's law. This kind of netlength minimization was introduced by Eisenmann and Johannes in 1998. The force-based method uses the analytic placement techniques to achieve an illegal overlapping placement which minimizes quadratic netlength. The process uses this heuristic iteratively introducing "repelling forces" between each module and bins on the placement area with overlap. In every iteration, the current overlapping forces are added to the quadratic netlength and the combined quadratic function is minimized.

The force at a location  $(x, y)^t$  is set to:

$$f(x,y) = \frac{k}{2\pi} \int_{-\infty}^{+\infty} \int_{-\infty}^{+\infty} D(x',y') \frac{r-r'}{|r-r'|^2} dx' dy'$$

To improve the netlength, Eisenmann and Johannes also used a variation of the linearization method. Finally the Domino local search method which will be discussed later was used for final placement. Eisenmann and Johannes only used the heuristic on standard-cell circuits but Mo extended the force-based heuristic to macro-cells, with no linearization scheme to be considered. Also instead of introducing repulsive forces, a filling force is introduced between modules and empty regions of the placement area. Mo also considers orientation of the macro-cells. For each cell the new orientation is determined by considering all eight possible orientations and selecting the one which minimizes the external force. Since changing orientation of too many cells at once.

Finally Routing and pad positioning are meditated. Routing is meditated by estimating congestion in each bin and pad positions are computing according to modules position. Specifically, the pads are included in the quadratic matrixes, but they are allowed to move across on dimension only. The iterative flow is divided into three stages. Stage one gives initial positions of the macro-cells. Stage two optimizes orientation and routing. Finally stage three removes any additional overlap.

Hu and Marek-Sadowska introduced a slight modification of Eisenmann and Johannes' method referred to as Fixed-point Addition and Relaxation (FAR). In their method they create an extra pseudo-module for each module and an extra pseudo-

connection between each module and its associated pseudo-module. They noticed that fixed-points are easier to control than the repelling forces, and that their analytic placements can also be contained into a specific region, in comparison to the constant forces.

Attractor Repellor Approach (ARP) is another force-based method, proposed in 1999 by Etawil. It is a completely different method that the previous, because instead of looking at overlapping regions a repelling force is introduced between directly connected modules. This alternate idea may have many drawbacks, like too much overlap that grows the total wirelength in legalization stage. Therefore Etawil introduces attractive forces in low density regions.

## 4.1.4 Simulated Annealing for Global Placement

Simulated annealing (SA) is a generic probabilistic method for the global optimization problem. It firstly proposed from Kirkpatrick, Gelett and Vecchi(1983) and Cerny (1985). It results a good approximation to the global optimum of an objective function in a large, discrete search space with many local minima. In many cases simulated annealing may be more efficient than any other heuristic.

Because of its simplicity, it has become the most famous meta-heuristic, used in many applications, including physical placement, if all else fails. However, simulated annealing applied to the placement problem has shown that it is high time costly when used for large scale circuits Nevertheless, it is used from the Dragon placer, for the global placement, and it is very used in final placement, even when it is used in partitions of the global placement.

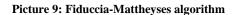

## 4.1.5 Clustering

Some placement algorithms combine modules in clusters (clustering). Clustering is a powerful method dealing with sub-circuits, and can reduce the running time since there are fewer modules. Also, clustering can move a simple placement algorithm out of local minimum because it considers more than simple individual cell movement. Clustering methods have been used with the graph partitioning algorithms to improve the speed of the partitioning. However clusters have also been used in detailed placement. Given a gate-level circuit, the goal of circuit clustering is to group gates and their interconnections into clusters and obtain the network of the clusters. Thus, after clustering, a cluster becomes a done of the graph, resulting reductions of the nodes and their interconnections. Sequentially, clustering is used before portioning and placement algorithms, to reduce of the run time complexity of any heuristic applied after it. Clustering objective functions is to minimize the connections from a

cluster to another maximizing the number of connections inside a cluster, and to maximize the number of inter-cluster connections on any path. Typical constraints of this method may include the maximum cluster size and the maximum number of external connections for a cluster. The number of clusters to be obtained is not specified, and the area balance among the clusters is usually not required.

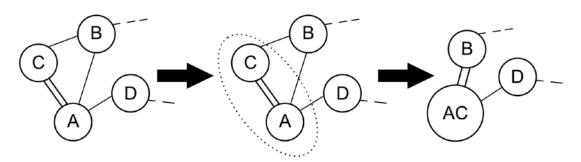

Picture 11: clustering example. Starting with A, it is clustering with C because they have the greatest connection. Then AC is going to be in the same cluster as B, for the same reason.

There are two ways to consider clustering problem in physical placement, in order to organize the clusters better for this specific problem:

- Produce the clusters strictly following the hypergraph representation of the circuit, as a general problem without considering placement.

- Produce the clusters based on placement heuristics and commute weights according to the objective function.

The most popular algorithms that use clustering based on placement heuristics are Rajaraman and Wong algorithm in 1995, FlowMap algorithm of Cong and Ding in 1992 and Multi-level Coarsening algorithm if Karypis in 1997. The first two are timing driven algorithms, where the longest path delay inside a cluster is minimized under a certain delay model. The last one minimizes the number of connections between clusters.

#### **Rajaraman and Wong Algorithm**

Given a directed acyclic graph which represents a gate-level circuit the algorithm produces a timing driven clustering solution.

In respect to the "general delay model" that uses, below are introduced the delays in the circuit:

- The delay inside each node of the cluster is computed.

- The inter-cluster edges have constant delay.

- The intra-cluster edges do not incur any delay.

- The size of each cluster is bounded by another constant.

- The critical paths delay from any primary input to primary output in the clustered network is minimized.

• Some nodes in the original DAG may be duplicated in the clustering solution.

The algorithm consists of two phases, labeling and clustering phase. During the labeling phase, the critical path delay from any primary input to each node is computed, adding both the node's delay and the delay from the primary input to the node (inter-cluster edge). During the labeling process, the clustering information about the nodes that will be clustered in the same cluster-node is also collected, and in case a node is included in multiple clusters, it is duplicated to exist in both clusters. More specifically, a  $n \times n$  matrix D that contains all-pair critical path delays is created. Each entry at row x and column v, denoted by D(x, v), is the critical path delay from the output of x to the output of v in the DAG using node delay values only and ignoring all interconnect delays. After this, the labels of all primary input nodes are initialized to their delay values and all other nodes are set to zero. We then visit non-primary inputs in a topological order to compute their labels.

During the clustering phase, the nodes are visited in the opposite topological order, and the general clustering process takes place.

#### **FlowMap Algorithm**

This algorithm produces also a timing driven clustering solution, but in difference to the Rajaraman and Wong algorithm it uses the "unit delay model". In this model only the inter-cluster edges appear to have a unit delay while the nodes and intra-cluster edges do not incur any delay. The difference between the timing driven clustering using the unit delay model compared with the general delay model is that the number of external connections for each cluster is bounded by a constant. The maximum delay from any primary input to primary output in the clustered network is minimized in the solution. Some nodes in the original directed acyclic may be duplicated in the clustering solution.

FlowMap algorithm consists of two phases, the labeling and the mapping phase. During the labeling phase all nodes are met in topological order. For each node n the clustering set is computed, as the set of nodes that will be clustered together in the same cluster. Another variable has to be computed, named label l(n). This denotes the critical path delay from every primary input to v, where only the inter-cluster edges incur a unit delay. During the mapping phase, the nodes are visited in the opposite topological order, and the general clustering process takes place.

#### **Multi-Level Coarsening Algorithm**

Multi-level coarsening is an algorithm for clustering that first introduced as a part of hMetis algorithm for placement. hMetis algorithm released as the best bipaartitioning algorithm in Design Automation Conference (DAC) in 1997 from Karypis. It consists of two phases, clustering and partitioning, to solve the balanced bipartitioning problem, where the given circuit is divided into two roughly equal sized partitions. This algorithm's target is to minimize interconnects from each cluster to another, respecting the "multi-level optimization" heuristic that obtains iterative clustering processes. During the first iteration, the highly connected nodes are grouped into level

1 clusters, and create a graph that contains them. This graph has fewer nodes than the original graph. Next level-1 clusters are grouped together to form level-2 clusters and their graph is created. This process is repeated until we group the clusters together in the target level K, in the clustering hierarchy, and the size of the graph is reduced spectacularly.

After the clustering, the level-K clusters have to be partitioned using any of the existing partitioning algorithms. After the partitioning process ends, every level-K cluster has to be decomposed to its level-K-1 clusters, and a partitioning algorithm is performed again to optimize further the current partitioning solution. This process of decomposing and optimizing the graphs' solutions is repeated until there are no clusters but the partitioned circuit. This clustering algorithm, because of considering its high level cluster interconnections, and because of its iterative nature, gives better partitioning solution.

More specifically, given a hypergraph that represents the original circuit, hMetis algorithm utilizes three algorithms to compute the multi-level cluster hierarchal, which are introduced below:

- Edge coarsening (EC): Initially, the nodes in the graph are unmarked and visited in a random order. Given an unmarked node v, the "neighbors" of v must be collected, which is the set of nodes that are unmarked and are included in the edges that contain v. For each neighbor n of v, the weight of edge (v, n) is computed by assigning a value 1/(|h| by1), where h denotes the edge that contains both n and v. After examining all neighbors of v, the neighbor with the maximum edge weight must be selected and v and n must be merged together. Both n and v so are marked that these nodes are not clustered again later. This process completes when all nodes are visited.

- Hyperedge coarsening (HEC): Initially, the nodes in the hypergraph are unmarked. If the hyperedges are not weighted they are sorted by size with an increasing order, otherwise are sorted by their weights decreasingly. In every case they are visited in the sorted order and there are examined if any of them contains any node that is already marked. If not, all nodes are grouped in the hyperedge to form a cluster. Otherwise, we skip to the next hyperedge. After visiting all hyperedges, each node that is not part of any cluster becomes a cluster of its own.

- Modified hyperedge coarsening (MHEC): This algorithm first applies hyperedge coarsing to the given hypergraph and after the hyperedges to be clustered have been selected, the algorithm visits them again in the sorted order. Then, for each hyperedge that has not yet been clustered there is examined if it contains any node that is unmarked, to cluster them all together. MHEC achieves reduce further the number of the inter-connections among clusters after balance the size among the clusters.

# 4.2 Final placement Methods

The aim of final placement implementation is to further improve the placement's solution quality. It is more constrained than the global placement as it optimizes the objectives and produces a legal placement. It usually uses more accurate models such as half-perimeter wirelength. Compared to legal placement there has been much less work in terms of final placement. At the following paragraphs there will be represented the most significant methods of final placement.

A classification of final placement methods is difficult because they may utilize a number of different algorithms within the same method, and some amount of legalization may be inherent in the proceeding global placement. There tends to be five main categories of techniques used more frequently, or a combination of them.

- The first is the network flow methods. In these methods a transportation problem is solved using a minimum cost flow or shortest path algorithm. The core area is divided into core bins, and density values are calculated for each bin based on the cell area in it. The cost of moving a cell to another bin is calculated according to the objective function. Generally, cells are moved from the densest bin to the less dense bins, following paths that result in the least degradation of placement quality.

- The second category, min-cut methods, separates the global placement into sets of equal number of paths and uses partitioning techniques to minimize their interconnections.

- The third category, linear placement methods, optimizes a linear arrangement of cells within a single row.

- Another basic category, random methods, such as one based on simulated annealing, randomly moves around locally to improve some objective function.

- At last, some greedy approaches are used for wirelength optimization in the final placement stage.

More specifically, final placement can be divided in two steps, legalization and detailed placement wirelength optimization.

## 4.2.1 Legalization

Given an illegal placement (constraints described in chapter 1), legalization is the process that eliminates all overlaps by perturbing the modules as little as possible.

Removing overlaps is the first challenge for a detailed algorithm. The common technique for removing overlaps is by stacking cells along rows or spreading out cells

within all placement bins. Another approach is stacking cells row by row without inserting white space and without consideration of the imbalance. This approach was first met in Feng Shui algorithm.

In a different method that was met in Domino algorithm, an overlap-free compact placement is constructed by growing the placement like a crystal region by region from left to right.

Another approach grows the placement cell by cell from left to right and it performs a less restrictive version of packing cells to the left, introduced in Tetris algorithm. Sometimes, detailed placement is separated in two stages with a coarse legalizer such as Mongrel making substantial improvements in overlap removal before a fine-grain legalizer is finally used.

## 4.2.2 Local improvement

Minimizing wirelength or other objectives during detailed placement stage often is done by swapping target cells from different rows. Other cells in these rows might have to be shifted in order to remove the possible overlap or white space.

Some placement tools consider only any combination of cells' order within one single row. Domino improves the current wirelength driven placement solution iteratively. It also reduces overlaps by separating the core area into bins and solves the problem locally, each of which is formulated as a transportation problem solved by network flow methods. Then only within a row cell swaps are allowed, avoiding extensive shifting of cells. Another placement technique proposes using dynamic programming approaches to separate the cells within a row into two groups dynamically changed, and finally rearrange them with a near optimal way in the row. However this technique has extra complexity for multiple numbers of rows. Capo uses a branchand bound end placer to find the best permutation of cells in a small region. It divides and stitches white space with cells if there is white space with the region, thereby distribution the cells in the region evenly.

Some placement use cells' swapping between different rows. For instance, during the Dragon2000's detailed placement swaps cells in different without any consideration of objective value's changes, and in most of the cases other cells have to be shifted to refine the placement, which sometimes results worst placement solutions. Another approach that was met in FengShui, swaps cells in different rows only when this swap results in no overlap with other cells in order to avoid shifting other cells. However these movements limit the effectiveness of inter-row cell swaps. Another related issue is that the calculation of accurate wirelength changes for shifted cells might be computational expensive. Timberwolf uses estimated wirelength changes of those shifted cells to reduce computation cost.

#### 4.2.3 Simulated annealing

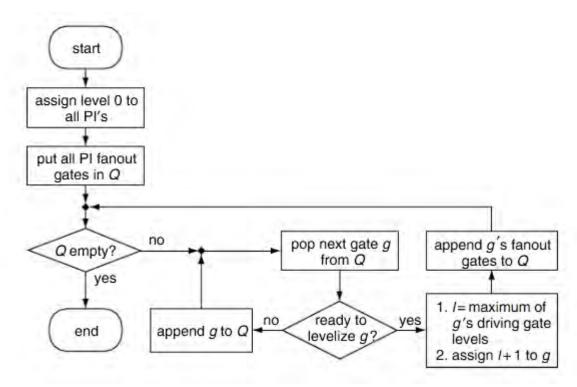

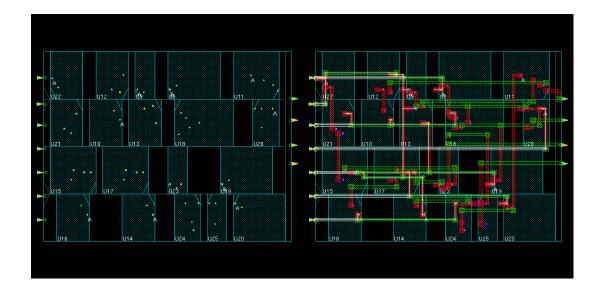

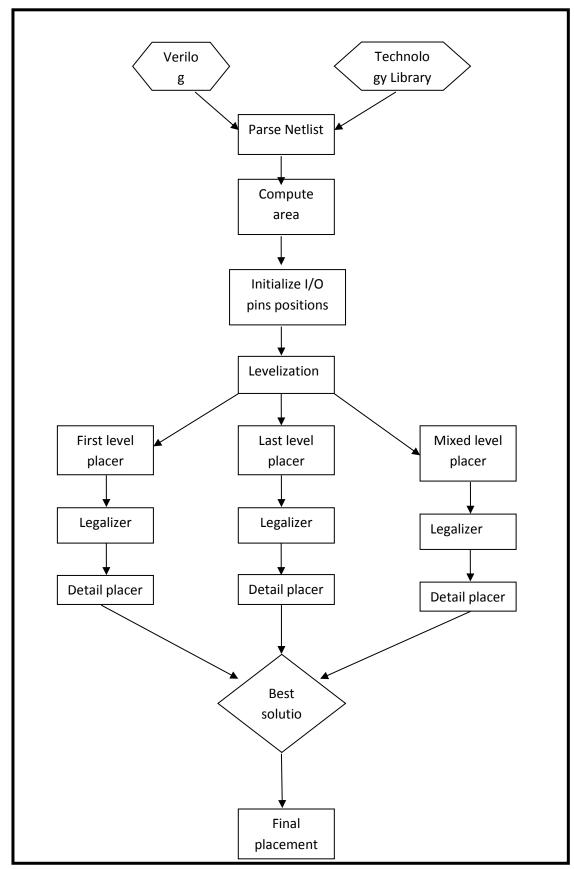

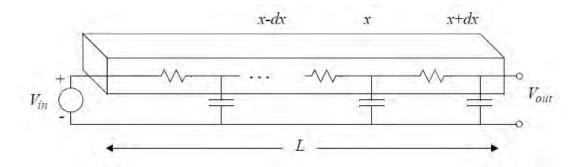

As introduced in previews paragraph Simulated annealing (SA) is a generic probabilistic method for the global optimization problem. It results a good approximation to the global optimum of an objective function in a large, discrete search space with many local minima. In many cases simulated annealing may be more efficient than any other heuristic.